IPC-SM-782A-表面贴装焊盘图形设计标准.pdf.pdf - 第96页

4.0 COMPONENT DIMENSIONS Figure 2 provides the component dimensions for SOT 89 components. Component Identifier L (mm) T (mm) W1 (mm) W2 (mm) W3 (mm) K (mm) H (mm) P (mm) min max min max min max min max min max min max ma…

1.0 SCOPE

This subsection provides the component and land pattern

dimensions for SOT 89 (small outline transistor) components.

Basic construction of the SOT 89 device is also covered. At

the end of this subsection is a listing of the tolerances and

target solder joint dimensions used to arrive at the land pat-

tern dimensions.

2.0 APPLICABLE DOCUMENTS

See Section 8.0 for documents applicable to the subsections.

2.1 Electronic Industries Association (EIA) JEDEC

Pubication 95 Registered and Standard Outlines for Solid

State and Related Products, TO-243, Issue ‘‘C’’ dated

7/15/86

Application for copies should be addressed to:

Global Engineering Documents

1990 M Street N.W.

Washington, DC

3.0 COMPONENT DESCRIPTIONS

These parts are for high power transistors and diodes. These

parts are used where heat transfer to a supporting structure

is important.

3.1 Basic Construction See Figure 1. The SOT 89 pack-

age dimensions are designed to meet the needs of both the

hybrid and printed board surface mount industries. In order to

provide an adequate heat transfer path, there is no clearance

between the body of the component and the packaging and

interconnect structure. This design may accommodate the

reflow or wave soldering processes.

3.1.1 Termination Materials Leads must be solder-

coated with a tin/lead alloy. The solder should contain

between 58 to 68% tin. Solder may be applied to the leads by

hot dipping or by plating from solution. Plated solder termina-

tions should be subjected to post-plating reflow operation to

fuse the solder. The tin/lead finish should be at least 0.0075

mm [0.0003 in] thick.

Solder finish applied over precious metal electrodes should

have a diffusion barrier layer between the electrode metalliza-

tion and the solder finish. The barrier layer should be nickel or

an equivalent diffusion barrier, and should be at least 0.00125

mm [0.00005 in] thick.

3.1.2 Marking Parts are available with or without marked

values.

3.1.3 Carrier Package Format Carrier package format

shall be according to the following: body type TO-243, 12 mm

tape/8 mm pitch.

3.1.4 Resistance to Soldering Parts should be capable of

withstanding ten cycles through a standard reflow system

operating at 215°C. Each cycle shall consist of 60 seconds

exposure at 215°C. Parts must also be capable of withstand-

ing a minimum of 10 seconds immersion in molten solder at

260°C.

IPC-782-8-7-1

Figure 1 SOT 89 construction

IPC-SM-782

Surface Mount Design

and Land Pattern Standard

Date

8/93

Section

8.7

Revision Subject

SOT 89

Page1of4

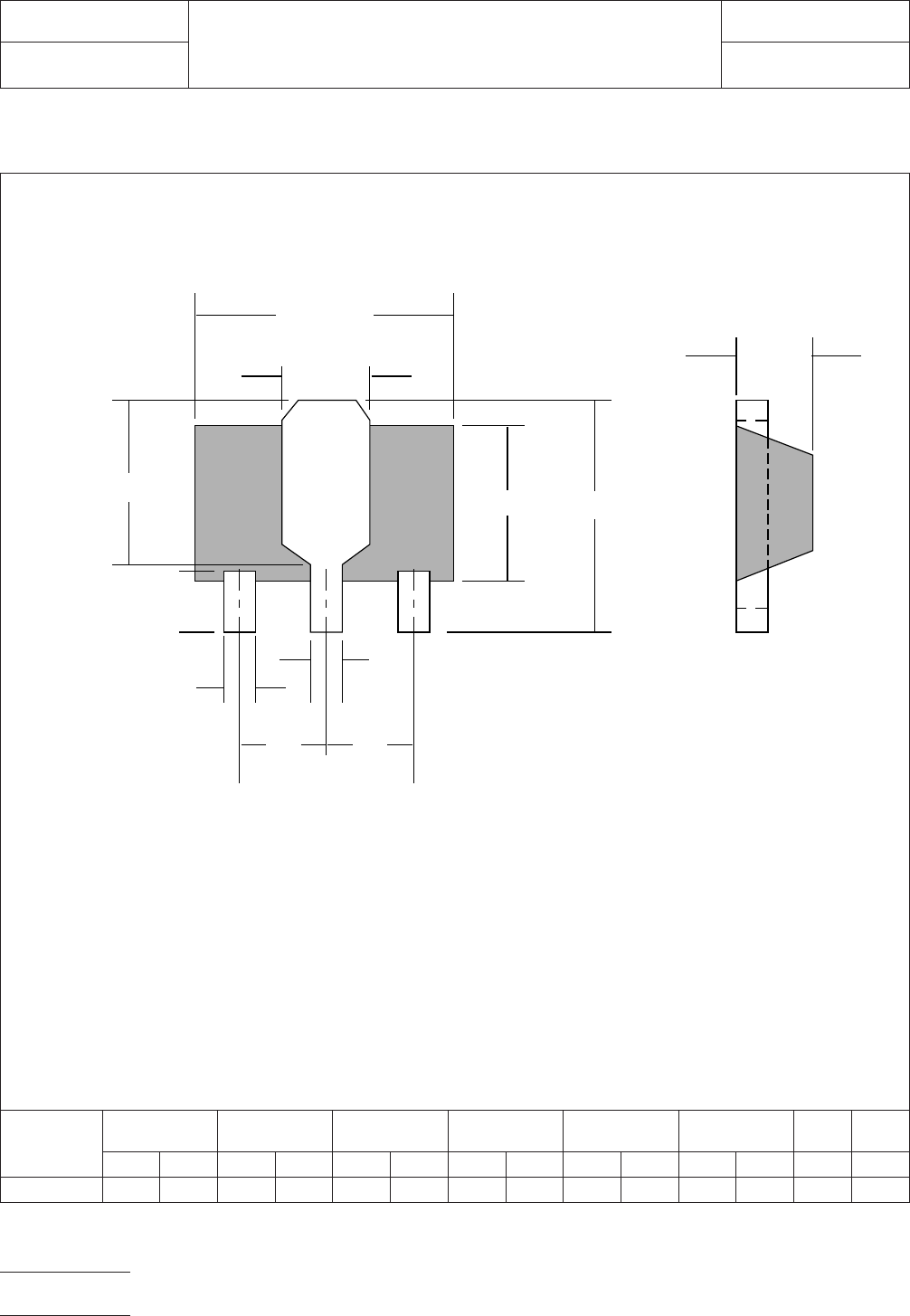

4.0 COMPONENT DIMENSIONS

Figure 2 provides the component dimensions for SOT 89 components.

Component

Identifier

L (mm) T (mm) W1 (mm) W2 (mm) W3 (mm) K (mm)

H

(mm)

P

(mm)

min max min max min max min max min max min max max basic

SOT 89 3.94 4.25 0.89 1.20 0.36 0.48 0.44 0.56 1.62 1.83 2.60 2.85 1.60 1.50

Figure 2 SOT 89 component dimensions

▼

W3

L

K

W2

W1

T

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

P

▼

▼

H

▼

▼

2.29–2.60

4.40–4.60

Dimensions are in millimeters.

▼

▼

P

IPC-782-8-7-2

IPC-SM-782

Subject

SOT 89

Date

8/93

Section

8.7

Revision

Page2of4

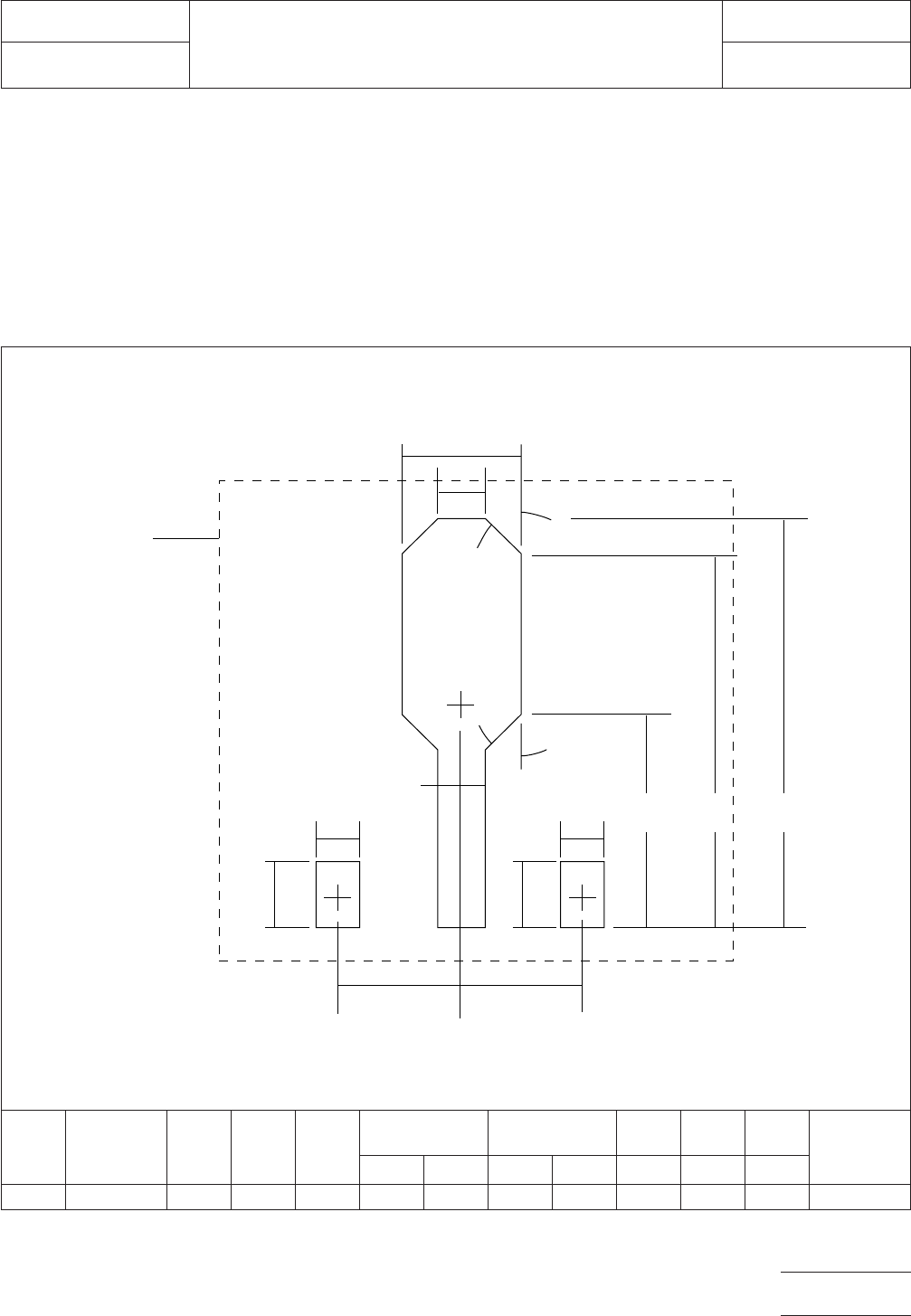

5.0 LAND PATTERN DIMENSIONS

Figure 3 provides the land pattern dimensions for SOT 89

components. These numbers represent industry consensus

on the best dimensions based on empirical knowledge of fab-

ricated land patterns.

In the table, the dimensions shown are at maximum material

condition (MMC). The least material condition (LMC) should

not exceed the fabrication (F) allowance shown on page 4.

The LMC and the MMC provide the limits for each dimension.

The dotted line in Figure 3 shows the grid placement court-

yard which is the area required to place land patterns and

their respective components in adjacent proximity without

interference or shorting. Numbers in the table represent the

number of grid elements (each element is 0.5 by 0.5 mm) in

accordance with the international grid detailed in IEC publica-

tion 97.

RLP

No.

Component

Identifier Z (mm)

Y1

(mm)

X1

(mm)

X2 (mm) X3 (mm)

Y2

(mm)

Y3

(mm)

E

(mm)

Placement

Grid

(No. of Grid

Elements)min max min max ref ref basic

215 SOT 89 5.40 1.40 0.80 0.80 1.00 1.80 2.00 2.40 4.60 1.50 12x10

Figure 3 SOT 89 land pattern dimensions

▼

Y2

▼

Y3 Z

▼

▼▼

▼

▼

X3

X1

Y1

EE

45°

45°

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

Grid

placement

courtyard

X2

▼

▼

X1

▼

▼

X2

▼

Y1

▼

▼

IPC-782-8-7-3

IPC-SM-782

Subject

SOT 89

Date

8/93

Section

8.7

Revision

Page3of4