MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS - 第215页

MIL-STD-883F METHOD 2010.11 18 June 2004 5 FIGURE 2010-2. Multil ayered metall ization . FIGURE 2010-3. Multil evel metall ization . ( 26) Operat ing metal lizati on (conduc tors ) . Metal or any other mat erial used for…

MIL-STD-883F

METHOD 2010.11

18 June 2004

4

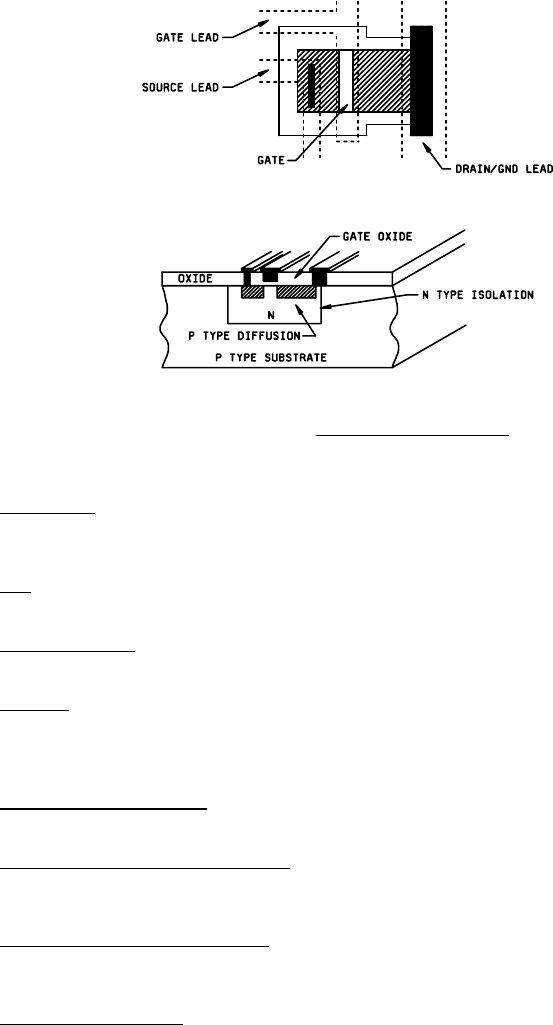

FIGURE 2010-1. P channel MOS transistor

.

(18) Junction line

. The outer edge of a passivation step that delineates the boundary between "P" and "N" type

semiconductor material. An active junction is any P/N junction intended to conduct current during normal

operation of the circuit element, (e.g., collector to base).

(19) Kerf

. That portion of the component area from which material has been removed or modified by trimming or

cutting.

(20) Line of separation

. Visible distance or space between two features that are observed not to touch at the

magnification in use.

(21) MESFET

. (Metal semiconductor field-effect transistor). A field-effect transistor in which a metal

semiconductor rectifying contact is used for the gate electrode. Typically the structure is fabricated in

gallium arsenide and the term GaAs MESFET may be used. Both depletion-type and enhancement type

devices have been manufactured. The acronyms are D-MESFET, and E-MESFET, respectively.

(22) Metallization nonadherence

. Unintentional separation of material from an underlying substrate excluding air

bridges and undercutting by design.

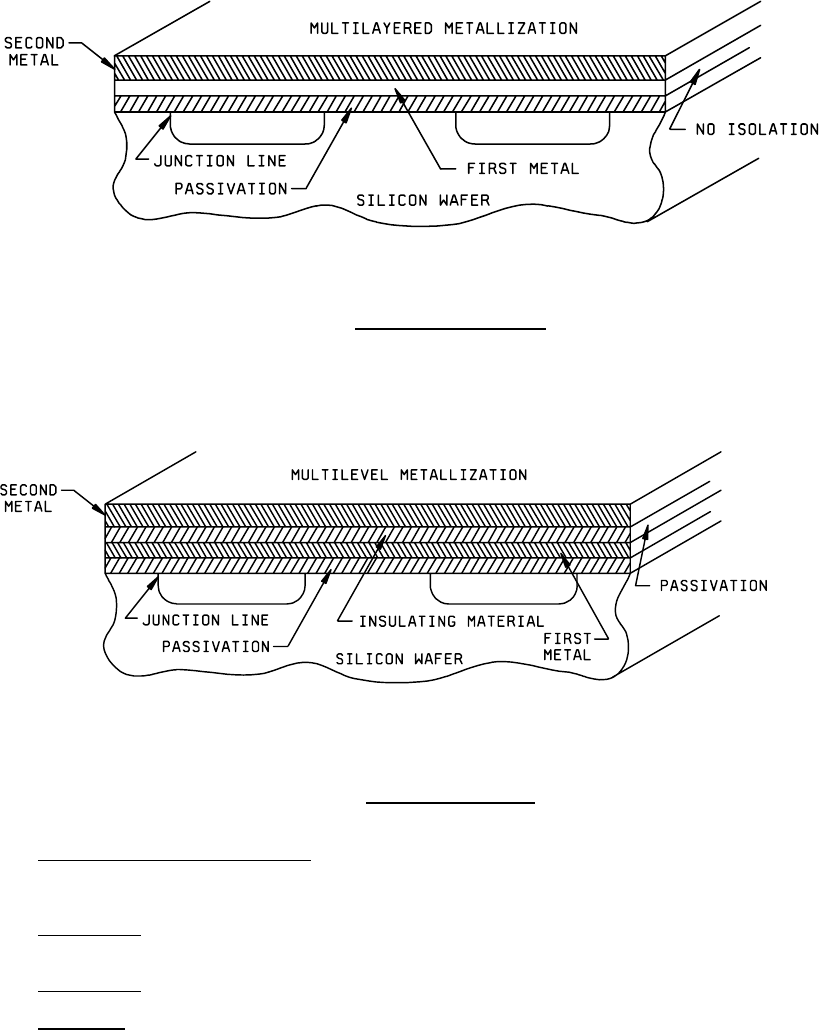

(23) Multilayered metallization (conductors)

. Two or more layers of metal or any other material used for

interconnections that are not isolated from each other by insulating material. The term "underlying metal"

shall refer to any layer below the top layer of metal (see figure 2010-2).

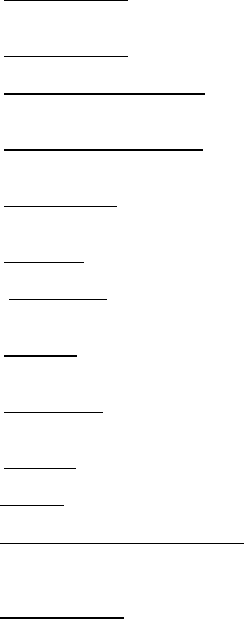

(24) Multilevel metallization (conductors)

. Two or more levels of metal or any other material used for

interconnections that are isolated from each other by insulating material (also referred to as interlevel

dielectric) (see figure 2010-3).

(25) Narrowest resistor width

. The narrowest portion of a given resistor prior to trimming.

MIL-STD-883F

METHOD 2010.11

18 June 2004

5

FIGURE 2010-2. Multilayered metallization

.

FIGURE 2010-3. Multilevel metallization

.

(26) Operating metallization (conductors)

. Metal or any other material used for interconnection except metallized

scribe lines, test patterns, unconnected functional circuit elements, unused bonding pads, and identification

markings.

(27) Original width

. The width dimension or distance that would have been present, in the absence of the

observed abnormality (e.g., original metal width, original diffusion width, original beam width, etc.).

(28) Package post

. A generic term used to describe the bonding location on the package.

(29) Passivation

. The silicon oxide, nitride or other insulating material that is grown or deposited directly on the

die prior to the deposition of metal or between metal levels on multilevel devices.

MIL-STD-883F

METHOD 2010.11

18 June 2004

6

(30) Passivation step. An abrupt change of elevation (level) of the passivation such as a contact window, or

operating metallization crossover.

(31) Peripheral metal

. All metal that lies immediately adjacent to or over the scribe grid.

(32) Redistribution Layer (RDL)

. Layer added to original wafer/die surface to allow for the redistribution of bond

pads into a format more suitable to flip chip.

(33) Redistribution metalization

. The metal deposited on the RDL to create the electrical conductors which

connect the original bond pads to the distributed solder bump pads.

(34) Shooting metal

. Metal (e.g., aluminum, gold) expulsion of various shapes and lengths from under the wire

bond at the bonding pad.

(35) Solder ball

. Solder ball or sphere attached to the UBM through the contact via after a re-flow process.

(36) Solder Bump

. Solder that is either electroplated or screened into the photo resist opening. After the photo

resist is removed the solder resembles a bump before it is reflowed into ball or sphere.

(37) Substrate

. The supporting structural material into or upon which or both the passivation, metallization and

circuit elements are placed.

(38) Substrate via

. A small hole formed through the wafer and metallized, causing electrical connection to be

made from the frontside (the side on which the circuitry is formed) to the backside of the wafer.

(39) Thick film

. That conductive/resistive/dielectric system that is a film having greater than 50,000Å thickness.

(40) Thin film

. That conductive/resistive/dielectric system that is a film equal to or less than 50,000Å in thickness.

(41) Under Bump Metalization (UBM)

. Metals deposited on top of the aluminum bond pads or on the solder bump

pads that enhance wetting and protect against intermetalic reactions between the solder and the original

metal on the pads.

(42) Via metallization

. That which connects the metallization of one level to another.

g. Interpretations. Reference herein to "that exhibits" shall be considered satisfied when the visual image or visual

appearance of the device under examination indicates a specific condition is present and shall not require

confirmation by any other method of testing. When other methods of test are to be used for confirming that a

reject condition does not exist, they shall be approved by the acquiring activity. For inspections performed on the

range of 75X to 100X, the criteria of 0.1 mil of passivation, separation or metal can be satisfied by a line of

separation or a line of metal visible.

h. Foreign material control. The manufacturer shall perform an audit on a weekly basis for (1) the presence of

foreign material within incoming piece part lids and bases, and (2) the presence of foreign material on the die

surface or within the package of assembled parts.

The audit of assembled parts may be satisfied during routine internal visual inspection. If the presence of foreign

material is discovered, the manufacturer shall perform the necessary analysis on a sample of the foreign material

on the suspect devices to determine the nature of the material. The manufacturer shall document the results of

this investigation and corrective action to eliminate the foreign material and this information will be available to the

Government QAR, and the acquiring activity or the qualifying activity, as applicable. A corrective action plan shall

be obtained within a maximum of 10 working days of discovery.

The audit of incoming piece part lids and bases shall be performed before parts are assembled, or may be

satisfied during routine incoming quality inspection. If the presence of foreign material of a size 1 mil or greater is

discovered, the manufacturer will analyze the foreign material to determine its nature and document the results of

the analysis. If applicable, these results shall be distributed to the vendor supplying the parts, with the request

that the vendor document corrective actions to minimize or eliminate such foreign material. This information will

be available to the manufacturer, Government QAR, and the acquiring activity or qualifying activity, as applicable.