MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS - 第226页

MIL-STD-883F METHOD 2010.11 18 June 2004 16 Condition A Conditi on B Class le vel S Class lev el B FIGURE 2010-16. Bond pad termi nology . NOTE: W hen a f illet are a ex ists, it is to be con sidered as part of th e ente…

MIL-STD-883F

METHOD 2010.11

18 June 2004

15

Condition A Condition B

Class level S Class level B

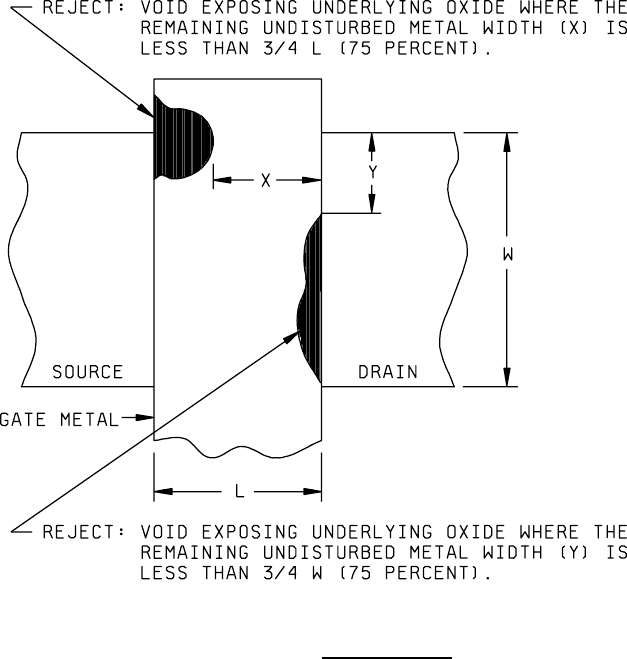

d. Void(s) that leave less than 75 percent of the d. Void(s) that leave less than 60 percent of the

metallization area over the gate oxide undisturbed metallization area over the gate oxide undisturbed

(applicable to MOS structures only). (applicable to MOS structures only).

e. Void(s) that leaves less than 75 percent of the metallization width coincident with the source or drain diffusion

junction line undisturbed (applicable to MOS structures only) (see figure 2010-15).

FIGURE 2010-15. MOS void criteria

.

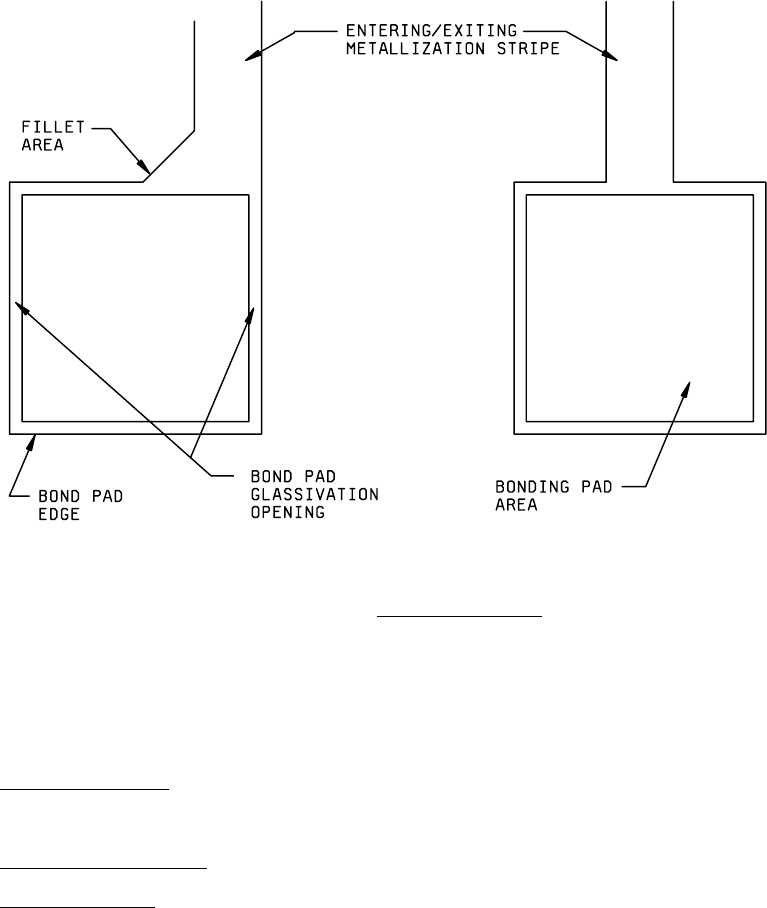

f. Void(s) in the bonding pad area that leaves less than 75 percent of its original unglassivated metallization area

undisturbed (see figure 2010-16).

g. Void(s) in the bonding pad or fillet area that reduces g. Void(s) in the bonding pad or fillet area that

the metallization path width connecting the bond to reduces the metallization path width connecting

the interconnecting metallization to less than 75 the bond to the interconnecting metallization

percent of the narrowest entering metallization stripe to less than 50 percent of the narrowest entering

width. If two or more stripes enter a bonding pad, metallization stripe width. If two or more

each shall be considered separately. (see figure stripes enter a bonding pad, each shall be

2010-16). considered separately (see figure 2010-16).

MIL-STD-883F

METHOD 2010.11

18 June 2004

16

Condition A Condition B

Class level S Class level B

FIGURE 2010-16. Bond pad terminology

.

NOTE: When a fillet area exists, it is to be considered as part of the entering/exiting metallization stripe.

h. Void(s) in the metallization area of a thin film capacitor that leave less than 75 percent of the designed

metallization area.

i. For GaAs microwave devices only, voids in the gate stripe.

3.1.1.3 Metallization corrosion

. Any metallization corrosion. Metallization having any localized discolored area shall be

closely examined and rejected, unless it is demonstrated to be a harmless film, glassivation interface, or other obscuring

effect.

3.1.1.4 Metallization nonadherence

. Any metallization lifting, peeling, or blistering.

3.1.1.5 Metallization probing

. Criteria contained in 3.1.1.1 shall apply as limitations on probing damage.

MIL-STD-883F

METHOD 2010.11

18 June 2004

17

Condition A Condition B

Class level S Class level B

3.1.1.6 Metallization bridging

.

NOTE: For SOS devices, exclude the insulator scribe lines.

a. Any metallization bridging where the separation a. Any metallization bridging where a

between metallization paths is reduced to less line of separation is not visible

than 50 percent of the original design. between metallization paths.

b. Any metal that is displaced, as a result of NOTE: For GaAs microwave devices,

bonding, from its original position on the metallization bridging across spacings

bonding pad (shooting metal) that reduces of less than 1 µm shall be inspected

the separation between unglassivated only in accordance with 3.2 and table I

operating metallization or scribe line at 400X to 1,000X. If a clear line of

and the bonding pad to less than 0.25 mils separation is not discernible,

or 50 percent design separation, device functional testing at the

whichever is less. wafer level shall suffice.

b. Any metal that is displaced, as a result

of bonding, from its original position

on the bonding pad (shooting metal) that

reduces the separation between

unglassivated operating metallization or

scribe line and the bonding pad such

that a line of separation is not

visible.

3.1.1.7 Metallization alignment

.

a. Contact window that has less than 75 percent of a. Contact window that has less than 50 percent

its area covered by metallization. of its area covered by metallization.

b. Contact window that has less than a continuous 50 b. Contact window that has less than 40 percent

percent of its perimeter covered by metallization. of its perimeter covered by metallization.

c. Contact window that has less than 75 percent of its perimeter on two adjacent sides covered by metallization

(applicable to MOS structures only).

NOTE: When, by design, metal is completely contained in a contact window or does not cover the entire contact

perimeter, criteria 3.1.1.7a, b, or c can be deleted, provided the design criteria is satisfied.

d. A metallization path not intended to cover a contact window that is not separated from the contact window by a

line of separation.

e. Any exposure of the gate oxide (i.e., oxide not covered by gate electrode in the area between source and drain

diffusions, applicable to MOS structures only) (see figure 2010-17).

3.1.1.8 Via hole metallization

. For GaAs devices only,

a. Overetched via hole or misaligned via visible around the pad.

b. Poor adhesion (lifting, peeling or blistering).

c. Any cracks originating at the via hole.

d. Evidence of bulging metal over a via hole.

e. Evidence of solder coming up through via hole pad, when die is mounted on a carrier.