MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS - 第275页

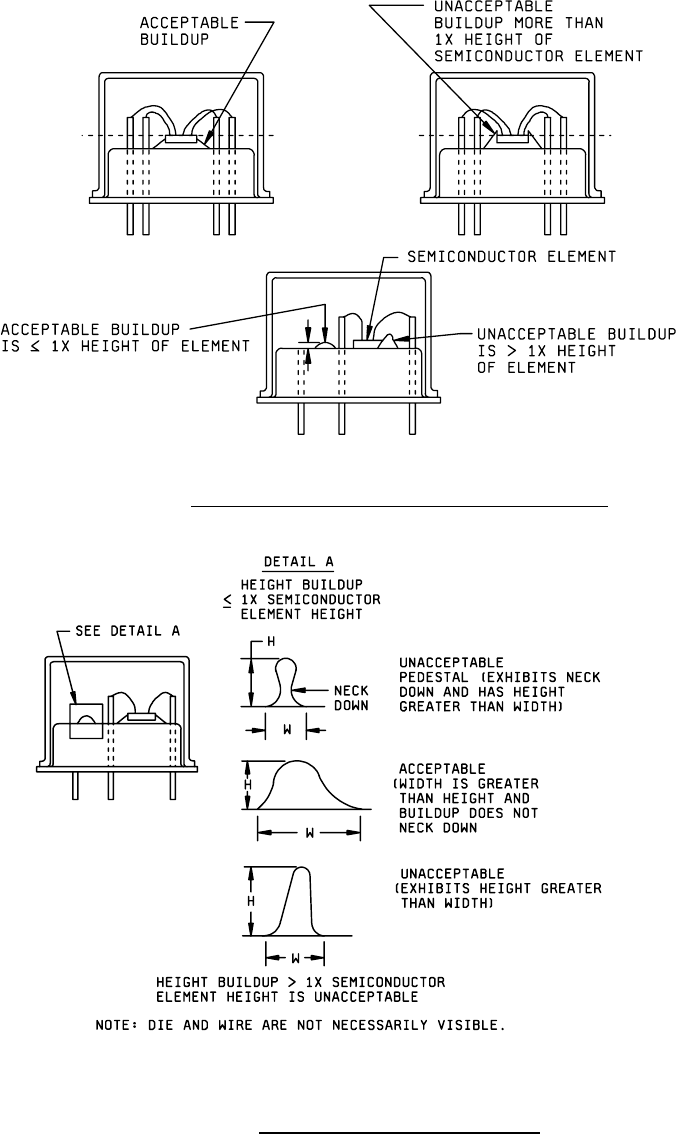

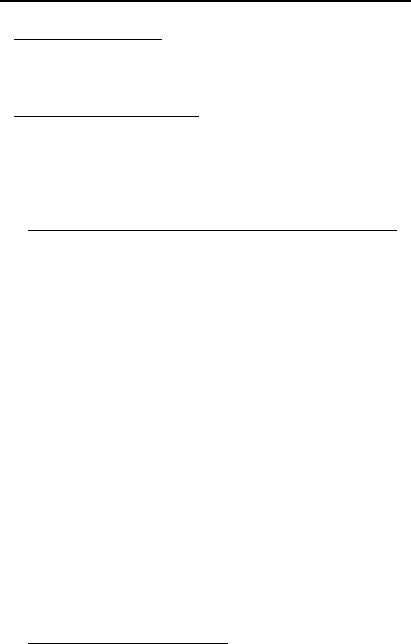

MIL-STD-883F METHOD 2012.7 1 June 1993 9 FIGURE 2012-2. Accept able and unacc eptable bondi ng material build- up . FIGURE 2012-3. Extraneous bonding mat erial build-up .

MIL-STD-883F

METHOD 2012.7

1 June 1993

8

(f) Any wire making a straight line run from die bonding pad to package post that has no arc,

unless specifically designed in this manner (e.g., clips or rigid connecting leads).

(g) Any internal post that is bent more than 10° from the vertical (or intended design position) or is

not uniform in length and construction or comes closer than one post diameter to another post.

(h) Where a low profile case (such as TO-46) is used, any post which comes closer to the top of

the case than 20 percent of the total inside dimension between the header and the top of the

case. In devices which have the semiconductor element vertical to the header, any device

where the semiconductor element comes closer than 0.05 mm (0.002 inch) to the header or to

any part of the case.

(i) Any case which does not have a header design incorporating a header edge or other feature

(e.g., a "splash ring") to prevent solder or weld splash from entering the interior of the case.

(3) Cylindrical axial lead type (see figure 2012-8).

(a) Whisker to case distance less than one-half of the diameter of the external lead wire.

(b) Distance from case to semiconductor die or to any eutectic bonding material less than 0.05

mm (0.002 inch).

(c) Whisker tilted more than 5° in any direction from the device lead axis or deformed to the

extent that it touches itself.

(d) C and S shaped whisker with air gap between any two points on it less than twice the

diameter or thickness of the whisker wire. On diodes with whiskers metallurgically bonded to

the post and to the die, the whisker may be deformed to the extent that it touches itself if the

minimum whisker clearance zone specified in figure 2012-8 (a) is maintained.

(e) Whiskerless construction device with anode and cathode lead connections displaced more

than 0.25 mm (0.01 inch) with respect to the central axis of the device.

(f) Semiconductor element mounting tilted more than 15° from normal to the main axis of the

device.

(g) Die hanging over edge of header or pedestal more than 10 percent of the die area.

(h) Less than 75 percent of the semiconductor element base area is bonded to the mounting

surface.

(i) Voids in the welds, from any edge, between the leads and the heat sink slugs greater than 15

percent of the lead wire diameter. Any voids whatever in the central part of the area that

should be welded.

(j) Devices with package deformities such as, body glass cracks, incomplete seals (voids,

position glass, etc), die chip outs and severe misalignment of S and C shaped whisker

connections to die or post.

MIL-STD-883F

METHOD 2012.7

1 June 1993

9

FIGURE 2012-2. Acceptable and unacceptable bonding material build-up

.

FIGURE 2012-3. Extraneous bonding material build-up

.

MIL-STD-883F

METHOD 2012.7

1 June 1993

10

3.11 Examination and acceptance criteria for hybrid devices.

3.11.1 Device construction

. Acceptable devices shall be of the specified design and construction with regard to the

characteristics discernible through radiographic examination. Devices that deviate significantly from the specified

construction shall be rejected.

3.11.2 Individual device defects

. The individual device examination shall include, but not be limited to, extraneous

matter, location and orientation of elements, cracks in the substrate that exceed 0.127 mm (0.005 inch) in length or point

toward active metallization, adhesive build-up, solder splashes, placement of wires, voids in the lid seal (this may not

apply to power hybrid devices), and improper wetting between the substrate(s) and the package. Any device for which

the radiograph reveals any of the following defects shall be rejected:

3.11.2.1 Presence of extraneous matter (foreign particles)

.

a. Unattached foreign material greater than 0.025 mm (0.001 inch), or of any lesser size which is sufficient to bridge

metallization or nonconnected conducting elements, that appears to be on the surface of the die, component,

substrate, or within the package.

b. Attached foreign material that bridges metallization paths, package leads, lead to package metallization, functional

circuit elements, junctions, or any combination thereof.

NOTE: Attached or unattached material may be verified by comparing two identical views with a mild mechanical

shock, such as PIND test, between the two views.

c. Wire tails or extra wires which make contact with any metallization not connected to the wire, or which exceed four

wire diameters in length at the substrate pad or package post, or two wire diameters at the top of a die or

component.

d. Any evidence of solder, alloy, or conductive adhesive that appears to bridge noncommon metallization (i.e., wire(s),

bonding post, active metallization or any combination thereof) not intended by design.

e. Gold flaking on the bonding post or anywhere inside the case.

3.11.2.2 Unacceptable construction

.

a. voids in substrate or component attachment medium.

(1) Contact area voids in excess of one-half of the total contact area.

(2) A single void which traverses either the length or width of the substrate or semiconductor element

and whose area exceeds 10 percent of the total intended contact area.

NOTE: To obtain, and/or verify substrate attachment the use of a thermal resistance analyzer, which

measures the thermal characteristics (heat dissipation), is strongly recommended.

b. Wires present, other than those connecting specific areas as per the drawing, except wires designated as tuning

devices on the bonding diagram, and except where bond-offs are allowed.

c. Improper component placement.

d. Cracks, splits, or chips in the component or substrate which enter the active circuit area.