MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS - 第278页

MIL-STD-883F METHOD 2012.7 1 June 1993 12 e. Voids in the l id seal in whic h the seal is not continuous or i s reduc ed from i ts des ign seal ing widt h by more than 75 percent . NOTE: Seal ing voids may not be detect …

MIL-STD-883F

METHOD 2012.7

1 June 1993

11

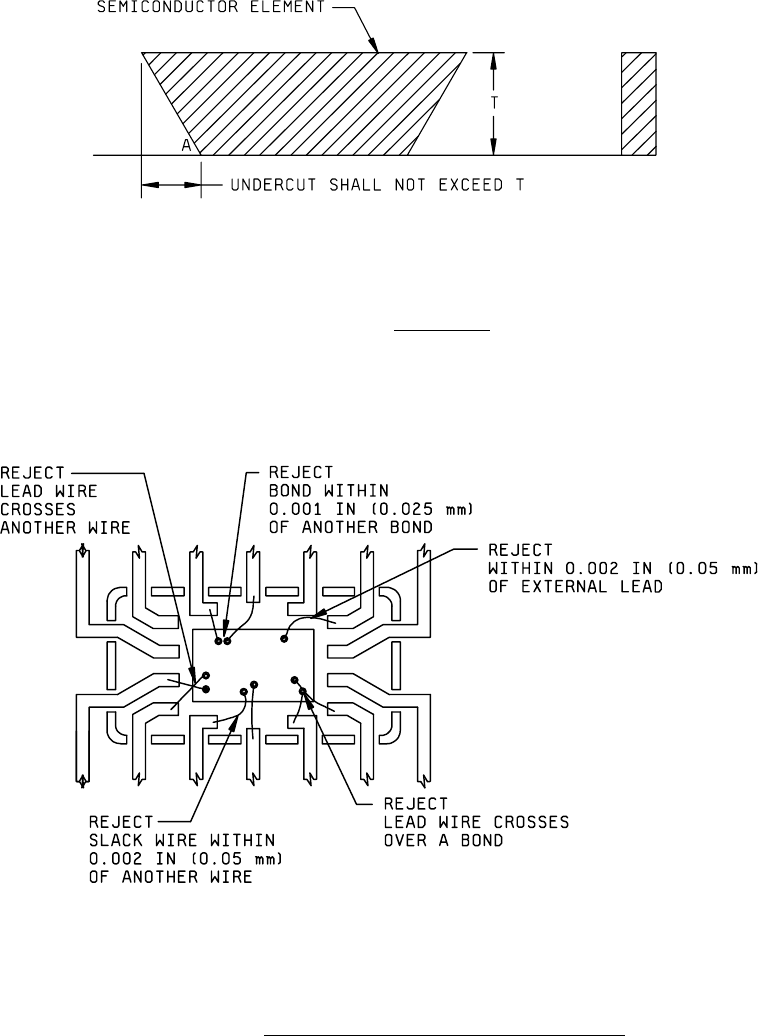

NOTE: Angle A shall be greater than 45°.

FIGURE 2012-4 Undercutting

.

FIGURE 2012-5. Clearance in dual-in-line or flat pack type device

.

MIL-STD-883F

METHOD 2012.7

1 June 1993

12

e. Voids in the lid seal in which the seal is not continuous or is reduced from its design sealing width by more than 75

percent.

NOTE: Sealing voids may not be detectable within power hybrid packages.

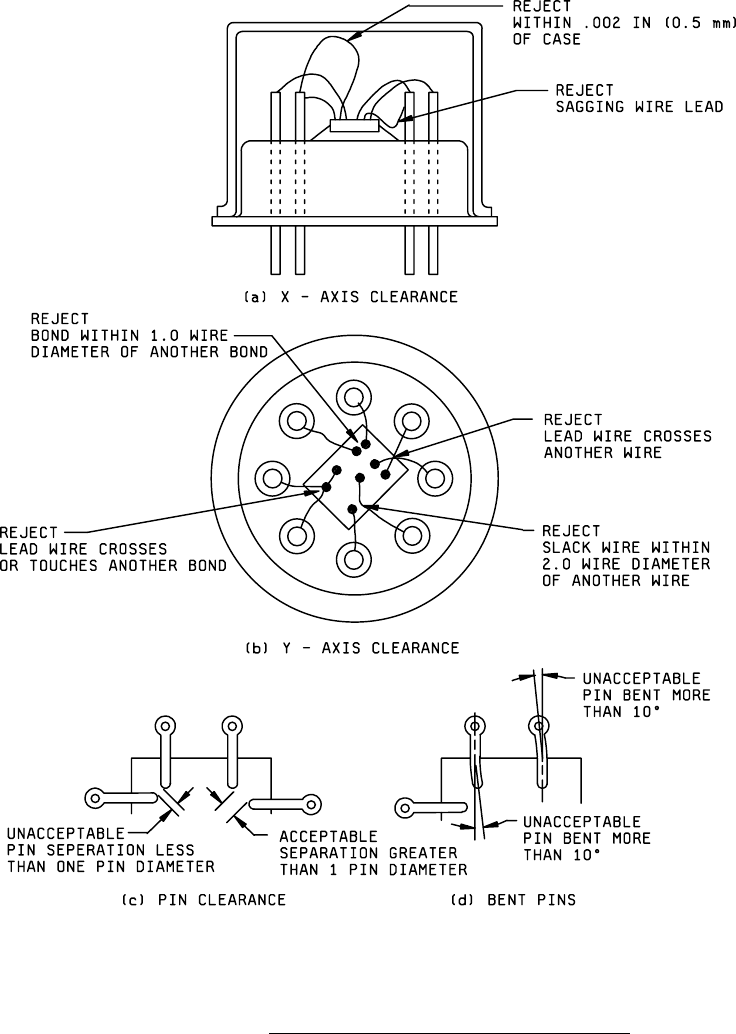

f. Inadequate clearance.

(1) Any wire that comes closer than 0.025 mm (0.001 inch) to another wire (excluding common wires)

within a spherical radial distance from the bond perimeter of 0.127 mm (0.005 inch) for ball bonds,

or 0.254 mm (0.010 inch) for ultrasonic and thermocompression wedge bonds.

NOTE: Insulated wires defined in the device specification/drawing are excluded from this criteria.

(2) Excessive loop or sag in any wire so that it comes closer than two wire diameters to another wire,

package post, unglassivated operating metallization, die, or portion of a package after a spherical

radial distance from the bond perimeter of 0.127 mm (0.005 inch) for ball bonds or 0.254 mm (0.010

inch) for ultrasonic and thermocompression wedge bonds.

NOTE: Insulated wires defined in the device specification/drawing are excluded from this criteria.

(3) Missing or extra wire(s) or ribbon(s) not in conformance with the bonding diagram except those

wire(s) or ribbon(s) designated as microwave tuning devices on the bonding diagram.

NOTE: Extra wires added for statistical process control lot or lot sample bond strength/process

machine/operator evaluation in accordance with MIL-PRF-38534 are excluded from this criteria.

(4) Any wire that has no arc and makes a straight line run from die bonding pad to package post.

(5) Wires crossing wires except common conductors or as allowed in 3.2.2e of method 2010

(condition A).

(6) Excessive height in any component or wire loop such that it is closer than

0.127 mm (0.005 inch) to the lid when installed.

(7) Any wires which are broken.

NOTE: Wire bond tails, as defined by method 2017, are excluded from this criteria.

(8) Excessive sag where the wire lies on the substrate for a distance greater than 1/2 the distance

between the edge of the substrate bonding pad and the chip to which the wire is bonded, or comes

closer than 0.025 mm (0.001 inch) to runout of any conductive epoxy which mounts the chip.

(9) Bonds placed so that the wire exiting from the bond crosses over another bond, except for common

bonds.

NOTE: For RF/microwave devices, bonds placed so that the wire exiting from a bond crosses over

another bond, except by design, in which case the clearance shall be two wire diameters minimum

(common bonds are excluded from this criteria).

MIL-STD-883F

METHOD 2012.7

1 June 1993

13

FIGURE 2012-6. Clearance in round or box transistor type device

.