MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS - 第515页

MIL-STD-883F METHOD 3015.7 22 March 1989 1 METHOD 3015.7 ELECTROSTATI C DISCHARGE SENSITIVI TY CLASSIFICATION 1. PURPOSE . This method est ablis hes the pr ocedure f or cl assi fying mi croc irc uits acc ording to t heir…

MIL-STD-883F

METHOD 3014

15 November 1974

2

This page intentionally left blank

MIL-STD-883F

METHOD 3015.7

22 March 1989

1

METHOD 3015.7

ELECTROSTATIC DISCHARGE SENSITIVITY CLASSIFICATION

1. PURPOSE

. This method establishes the procedure for classifying microcircuits according to their susceptibility to

damage or degradation by exposure to electrostatic discharge (ESD). This classification is used to specify appropriate

packaging and handling requirements in accordance with MIL-PRF-38535, and to provide classification data to meet the

requirements of MIL-STD-1686.

1.1 Definition

. The following definition shall apply for the purposes of this test method.

1.1.1 Electrostatic discharge (ESD)

. A transfer of electrostatic charge between two bodies at different electrostatic

potentials.

2. APPARATUS

.

2.1 Test apparatus

. ESD pulse simulator and device under test (DUT) socket equivalent to the circuit of figure 3015-1,

and capable of supplying pulses with the characteristics required by figure 3015-2.

2.2 Measurement equipment

. Equipment including an oscilloscope and current probe to verify conformance of the

simulator output pulse to the requirements of figure 3015-2.

2.2.1 Oscilloscope and amplifier

. The oscilloscope and amplifier combination shall have a 350 MHz minimum bandwidth

and a visual writing speed of 4 cm/ns minimum.

2.2.2 Current probe

. The current probe shall have a minimum bandwidth of 350 MHz (e.g., Tektronix CT-1 at 1,000 MHz).

2.2.3 Charging voltage probe

. The charging voltage probe shall have a minimum input resistance of 1,000 M and a

division ratio of 4 percent maximum (e.g., HP 34111A).

2.3 Calibration

. Periodic calibration shall include but not be limited to the following.

2.3.1 Charging voltage

. The meter used to display the simulator charging voltage shall be calibrated to indicate the actual

voltage at points C and D of figure 3015-1, over the range specified in table I.

2.3.2 Effective capacitance

. Effective capacitance shall be determined by charging C1 to the specified voltage (with table

I), with no device in the test socket and the test switch open, and by discharging C1 into an electrometer, coulombmeter, or

calibrated capacitor connected between points A and B of figure 3015-1. The effective capacitance shall be 100 pF ±10

percent over the specified voltage range and shall be periodically verified at 1,000 volts. (Note: A series resistor may be

needed to slow the discharge and obtain a valid measurement.)

2.3.3 Current waveform

. The procedure of 3.2 shall be performed for each voltage step of table I. The current waveform

at each step shall meet the requirements of figure 3015-2.

2.4 Qualification

. Apparatus acceptance tests shall be performed on new equipment or after major repair. Testing shall

include but not be limited to the following.

2.4.1 Current waveform verification

. Current waveform shall be verified at every pin of each test fixture using the pin

nearest terminal B (see figure 3015-1) as the reference point. All waveforms shall meet the requirements of figure 3015-2.

The pin pair representing the worst case (closest to the limits) waveform shall be identified and used for the verification

required by 3.2.

3. PROCEDURE

.

3.1 General

.

3.1.1 Test circuit

. Classification testing shall be performed using a test circuit equivalent to figure 3015-1 to produce the

waveform shown on figure 3015-2.

MIL-STD-883F

METHOD 3015.7

22 March 1989

2

3.1.2 Test temperature. Each device shall be stabilized at room temperature prior to and during testing.

3.1.3 ESD classification testing

. ESD classification testing of devices shall be considered destructive.

3.2 ESD simulator current waveform verification

. To ensure proper simulator operation, the current waveform verification

procedure shall be done, as a minimum, at the beginning of each shift when ESD testing is performed, or prior to testing

after each change of the socket/board, whichever is sooner. If the simulator does not meet all requirements, all

classification testing done since the last successful verification shall be repeated. At the time of initial facility certification

and recertifications, photographs shall be taken of the waveforms observed as required by 3.2c through 3.2e and be kept on

file for purposes of audit and comparison. (Stored digitized representations of the waveforms are acceptable in place of

photographs.)

a. With the DUT socket installed on the simulator, and with no DUT in the socket, place a short (figure 3015-1)

across two pins of the DUT socket and connect one of the pins to simulator terminal A and the other pin to terminal

B.

b. Connect the current probe around the short near terminal B (see figure 3015-1). Set the simulator charging

voltage source V

S

to 4,000 volts corresponding to step 4 of table I.

c. Initiate a simulator pulse and observe the leading edge of the current waveform. The current waveform shall meet

the rise time, peak current, and ringing requirements of figure 3015-2.

d. Initiate a simulator pulse again and observe the complete current waveform. The pulse shall meet the decay time

and ringing requirement of figure 3015-2.

e. Repeat the above verification procedure using the opposite polarity

(V

S

= -4,000 volts).

f. It is recommended that the simulator output be checked to verify that there is only one pulse per initiation, and that

there is no pulse while capacitor C1 is being charged. To observe the recharge transient, set the trigger to the

opposite polarity, increase the vertical sensitivity by approximately a factor of 10, and initiate a pulse.

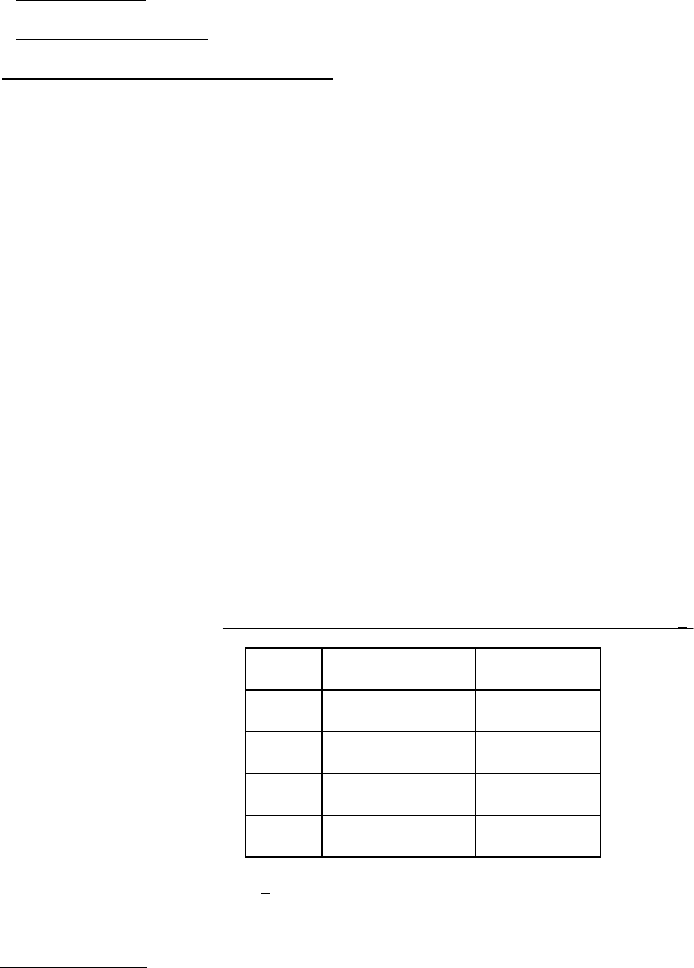

TABLE I. Simulator charging voltage (V

S

) steps versus peak current (I

P

). 1/

Step

V

S

(volts) I

P

(amperes)

1 500 0.33

2 1,000 0.67

3 2,000 1.33

4 4,000 2.67

1

/ I

P

is the current flowing through R2 during

the current waveform verification procedure

and which is approximately V

S

/1,500 ohms.

3.3 Classification testing

.

a. A sample of devices (see 4.c) shall be characterized for the device ESD failure threshold using the voltage steps shown

in table I, as a minimum. Finer voltage steps may optionally be used to obtain a more accurate measure of the failure

voltage. Testing may begin at any voltage step, except for devices which have demonstrated healing effects, including

those with spark gap protection, which shall be started at the lowest step. Examination of known technology family input

or output V/I damage characteristics (i.e., curve tracer), or other simplified test verification techniques may be used to

validate the failure threshold (e.g., cumulative damage effects may be eliminated by retesting at the failure voltage step

using a new sample of devices and possibly passing the step).