MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS - 第652页

MIL-STD-883F METHOD 5010.4 18 June 2004 2 TABLE I. Element evaluat ion su mmary . Element Par agraph Requireme nt Micr ocircuit wafer 3.2.2 Appendi x II (herei n) Package 3.2.3 Table II ( herein) 3.2.1. 2 Element eval ua…

MIL-STD-883F

METHOD 5010.4

18 June 2004

1

METHOD 5010.4

TEST PROCEDURES FOR COMPLEX MONOLITHIC MICROCIRCUITS

1. PURPOSE

. This method establishes screening, qualification, and quality conformance requirements for the testing of

complex monolithic microcircuits to assist in achieving the following levels of quality (class level B and S) and reliability

commensurate with the intended application. Complex monolithic microcircuits are defined as monolithic devices that

contain a minimum of 4,500 transistors. It shall be used in conjunction with other documentation such as appendix A of

MIL-PRF-38535 and an applicable device specification or drawing to establish the design, material, performance, control,

and documentation requirements which are needed to achieve prescribed levels of device quality and reliability.

2. APPARATUS

. Suitable measurement equipments necessary to determine compliance with applicable acquisition

documents and other apparatus as required in the referenced test methods.

3. PROCEDURE

. The procedures defined herein, including appendix I and II, outline the requirements and testing

necessary to certify and qualify a complex microcircuit design, fabrication, assembly and testing facility. It illustrates the

concept of generic qualification through the use of standard evaluation circuits and process monitors.

3.1 Test procedures for complex monolithic microcircuits

. Complex monolithic microcircuits shall be tested as described

herein, and in the device specification or drawing.

3.1.1 Precedence

. Unless otherwise specified in the device specification or drawing, the test requirements and

conditions shall be given herein.

3.1.2 Electrostatic discharge sensitivity

. Electrostatic discharge sensitivity testing, marking, and handling shall be in

accordance with appendix A of MIL-PRF-38535.

3.1.3 Failure analysis

. When required by the applicable device specification failure analysis of devices rejected during

any test in the screening sequence shall be accomplished in accordance with method 5003, test condition A.

3.1.4 Failure analysis class level S

. Class level S devices shall be analyzed in accordance with method 5003, test

condition B to identify the cause for failed lots and burn-in failures in accordance with appendix A of MIL-PRF-38535,

A.4.3.3.1, and A.4.6.1.2.1. The documented results shall only be reported to the qualifying or acquiring activity when

specifically requested.

3.1.5 Class requirements

. Within tables having a class column, only those test and inspections or subgroups identified

with "B" are applicable to class level B. All apply to class level S.

3.1.6 Radiation

. When required by the applicable device specification or drawing, qualification, and quality conformance

inspection requirements for radiation hardness assured devices are in addition to the normal class level S and B

requirements. These requirements for each specified radiation levels (M, D, P, L, R, F, G and H) are detailed in table VIII

herein.

3.2 Element evaluation

.

3.2.1 General

.

3.2.1.1 Element

. Herein "element" refers to materials for device assembly. Before device assembly, element

characteristics shall be evaluated and verified to assure their compatibility with element specifications, device requirements,

and manufacturing procedures (see table I). Also, characteristics which cannot be verified after manufacturing but could

cause function failure shall be evaluated and verified before assembly.

*

*

*

MIL-STD-883F

METHOD 5010.4

18 June 2004

2

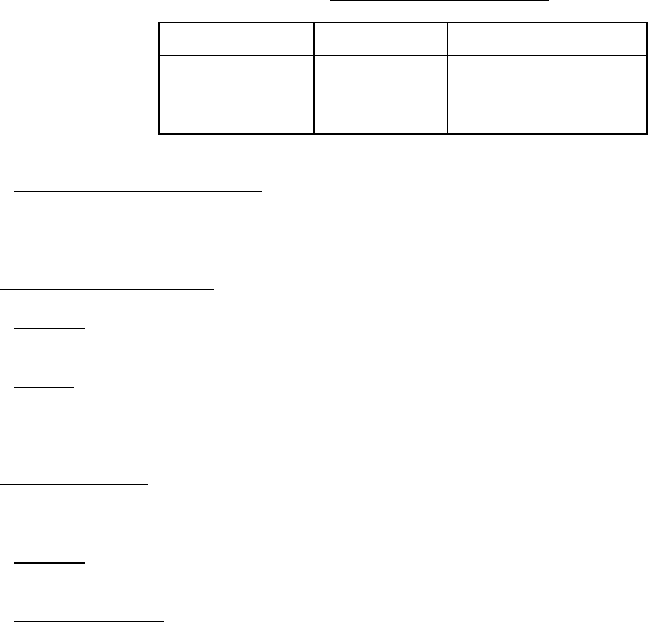

TABLE I. Element evaluation summary.

Element Paragraph Requirement

Microcircuit wafer 3.2.2 Appendix II (herein)

Package 3.2.3 Table II (herein)

3.2.1.2 Element evaluation requirements

. Element evaluation may be performed at either the element supplier or device

manufacturing facility up to the point where the element must undergo processing or assembly prior to testing. If element

evaluation is performed by the supplier, then the device manufacturer must obtain a summary of the results for verification,

and record retention.

3.2.2 Microcircuit wafer evaluation

.

3.2.2.1 Definition

. Diffused wafers used and evaluated shall, as a minimum, be complete with interconnect layers and

glassivation from material that was homogeneously processed through wafer fabrication.

3.2.2.2 General

. For the purpose of microcircuit wafer evaluation and wafer lot acceptance, measurement of the process

monitor (PM), verifying that the identified parameters are within process limits, will be required from each wafer lot in

accordance with appendix II wafer lot acceptance herein. Each die from each diffused wafer lot shall be electrically tested

prior to assembly in accordance with the manufacturer's in-house documentation.

3.2.3 Package evaluation

. Each package type shall be evaluated and characterized in accordance with table II herein

prior to use. Finite element analyses techniques may be used. Packages used for complex monolithic microcircuits and

fabricated to this test method shall be tested as follows:

3.2.3.1 Definition

. Package used and evaluated shall consist of the same element specifications, materials, and finish;

and homogeneously processed through device assembly.

3.2.3.2 Incoming inspection

.

a. From the initial package inspection lot, a randomly selected sample shall be subjected to package evaluation (see

table II). Additionally, subgroup 3 testing shall be accomplished using sealed packages. A die may be attached.

Subgroups 2, 3, and 4 apply to cases only.

b. Additionally, subgroups 1, 2, and 3 of table II shall be accomplished for each subsequent acquisition.

c. For solderability (subgroup 2), lead integrity (subgroup 3), and metal package isolation (subgroup 4) defined within

table II, a quantity (accept number) of 15 (0) shall apply to the number of terminals or leads tested. The leads

shall be randomly selected from the three packages.

MIL-STD-883F

METHOD 5010.4

18 June 2004

3

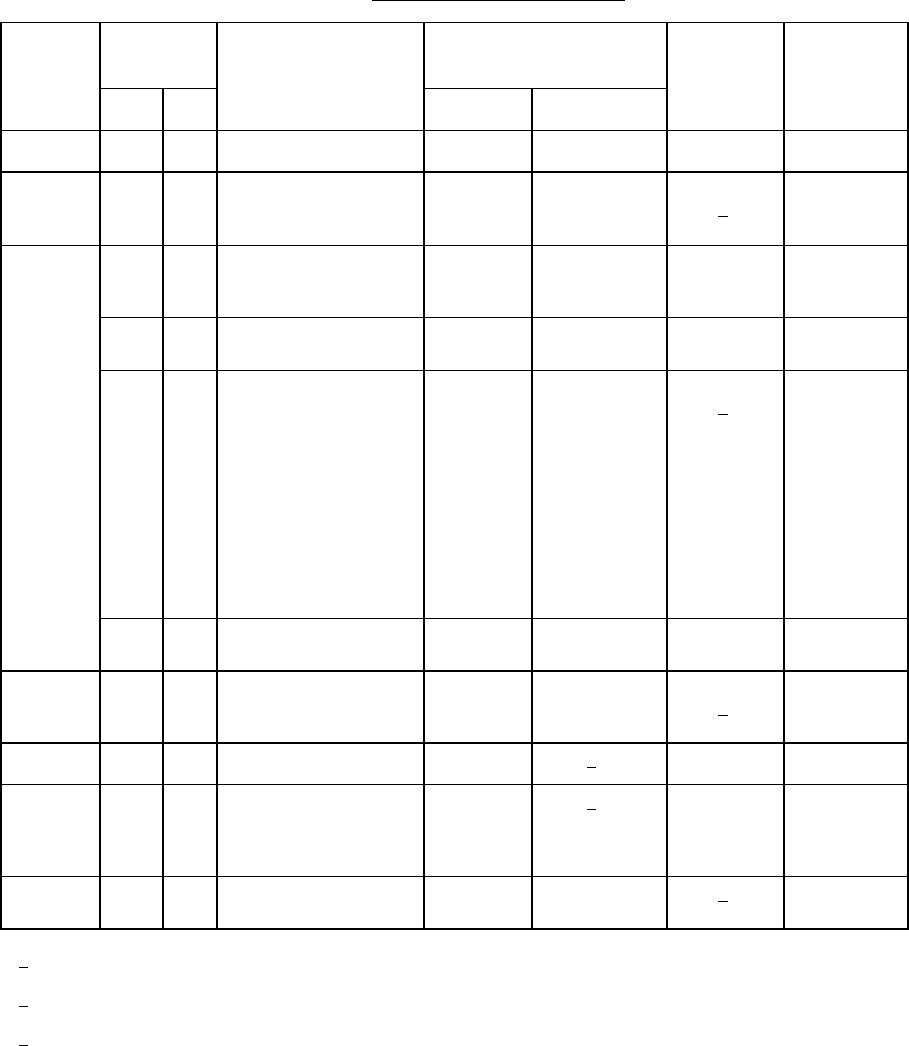

TABLE II. Package evaluation requirements

.

Subgroup

Class levels

Test MIL-STD-883 Quantity

(accept

number)

Reference

paragraph

S B

Method Condition

1 X X Physical dimensions 2016

15 (0) 3.2.3.3

2 X X Solderability 2003 Solderability

temperature

245 ±5°C

3 (0)

1

/

3 X X Thermal shock

or

Temperature cycle

1011

1010

C

C (20 cycles)

3 (0)

X X High temperature bake 1008 2 hours at

150°C

3 (0)

X X Lead integrity 2004

2028

B2

(lead fatigue)

D

(leadless chip

carriers)

B1

(leaded chip

carrier

packages)

(Pin grid array

leads and

rigid leads)

3 (0)

1

/

X X Seal 1014 D

Sealed cases

3 (0)

4 X X Metal package

isolation

1003 600 V dc,

100 nA

maximum

3 (0)

1

/

3.2.3.4

5 X X Insulation 1003 2/ 3 (0)

6 X X Conductor MIL-STD-

202

method

307

2/ 3 (0)

7 X X Thermal

characterization

1012

3/

1

/ A quantity (accept number) of 15 (0) shall apply to the number of terminals or leads to be tested. The leads

shall be randomly selected from three packages minimum.

2

/ Selected from three packages minimum. Conditions as specified by acquisition document and Appendix A of

MIL-PRF-38535.

3

/ Required on all package types prior to initial use.