MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS - 第665页

MIL-STD-883F METHOD 5010.4 18 June 2004 15 TABLE VI. Group C t esti ng . Subgroup Class leve ls Test MIL- STD-883 Sample si ze number, accept number Referenc ed paragra ph S B Method Condi tion 1 X X X X X X X X X X X X …

MIL-STD-883F

METHOD 5010.4

18 June 2004

14

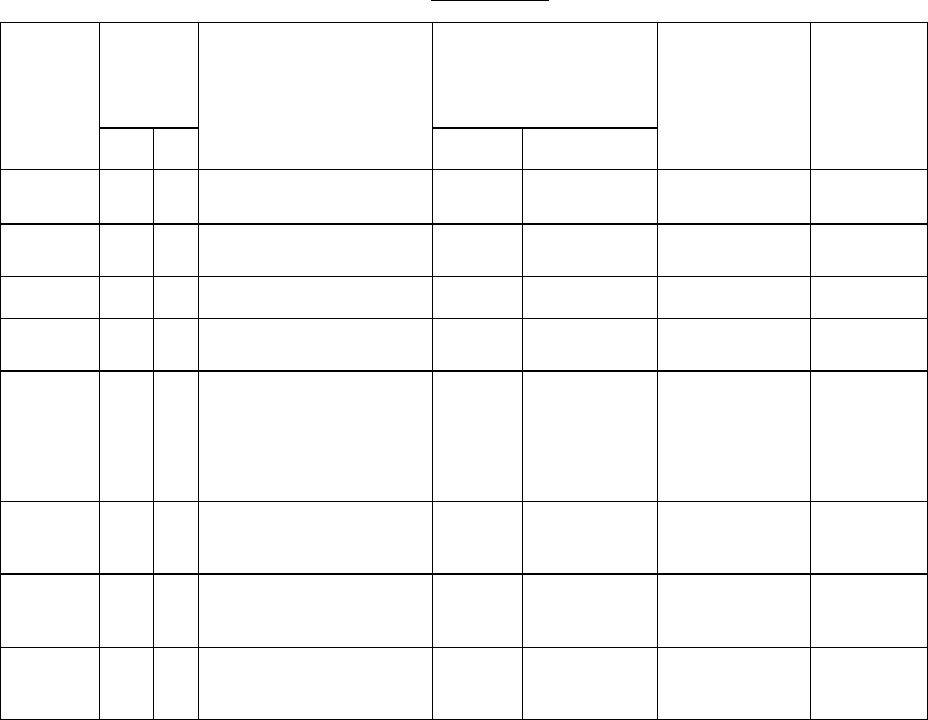

TABLE V. Group B testing.

Subgroup

Class

level

Test

MIL-STD-883 quantity/(accept

number)

or sample

size number,

accept number

Referenced

paragraph

S B

Method Condition

1

X X Physical dimensions 2016

2 (0)

2 X

Particle impact noise

detection test

2020 A or B 15 (0) 3.4.7

3 X X Resistance to solvents 2015

3 (0)

4 X X Internal visual and

mechanical

2014

1 (0) 3.4.2

5 X X Bond strength

a. Thermocompression

b. Ultrasonic or

wedge

c. Flip-chip

d. Beam lead

2011

C or D

C or D

F

H

2 (0)

6 X X Die shear strength or

substrate attach

strength

2019

or

2027

2 (0)

7 X X Solderability 2003 Solder

temperature

245°C ±5°C

1 (0)

8 X X Seal

a. Fine

b. Gross

1014

Sample size

number = 15

C = 0

3.4.8

MIL-STD-883F

METHOD 5010.4

18 June 2004

15

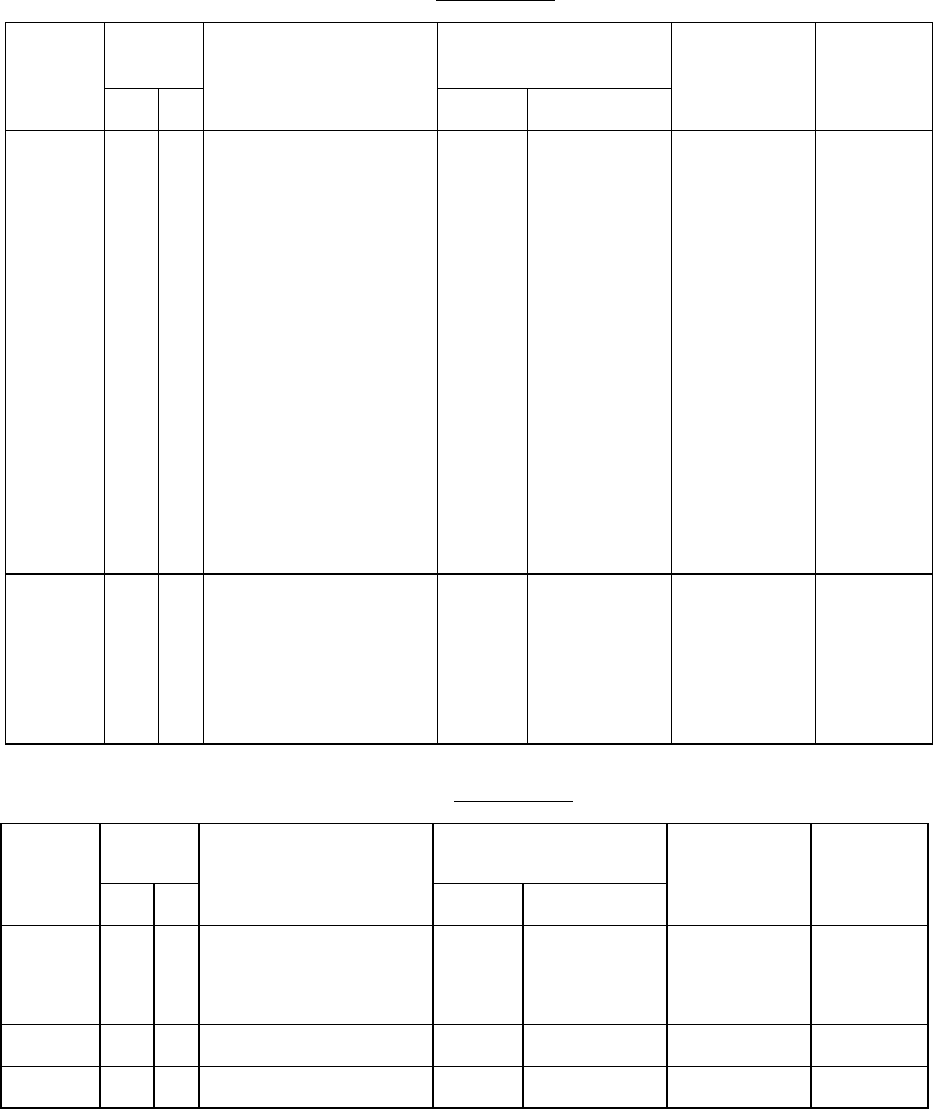

TABLE VI. Group C testing

.

Subgroup

Class

levels

Test MIL-STD-883 Sample size

number,

accept number

Referenced

paragraph

S B

Method Condition

1 X

X

X

X

X

X

X

X

X

X

X

X

X

External

Temperature cycling

Mechanical shock or

constant acceleration

Seal (fine and gross)

Radiographic

Visual examination

End point electrical

2009

1010

2002

2001

1014

2012

C

100 cycles

minimum

B, Y1 axis

E, Y1 axis

Y axis

In accordance

with visual

criteria of

method 1010.

As specified

in accordance

with device

specification

Sample size

number = 15

C = 0

3.4.13

3.4.5

3.4.6

3.4.8

3.4.12

3.5.2.3

2 X X Steady-state life test

End point electrical

1005 1,000 hours

at +125°C

minimum

As specified

in accordance

with device

specification

Sample size

number = 22

C = 0

3.5.2.3

TABLE VII. Group D testing

.

Subgroup

Class Test

MIL-STD-883 Quantity/

accept

number

Referenced

paragraph

S B

Method Condition

1 X X Internal water vapor

content

5000 PPM maximum water

content at +100°C

1018

3 devices

(0 failures)

or

5 devices

(1 failure)

2 X X Moisture resistance 1004

5 (0)

3 X X Salt atmosphere 1009

5 (0)

MIL-STD-883F

METHOD 5010.4

18 June 2004

16

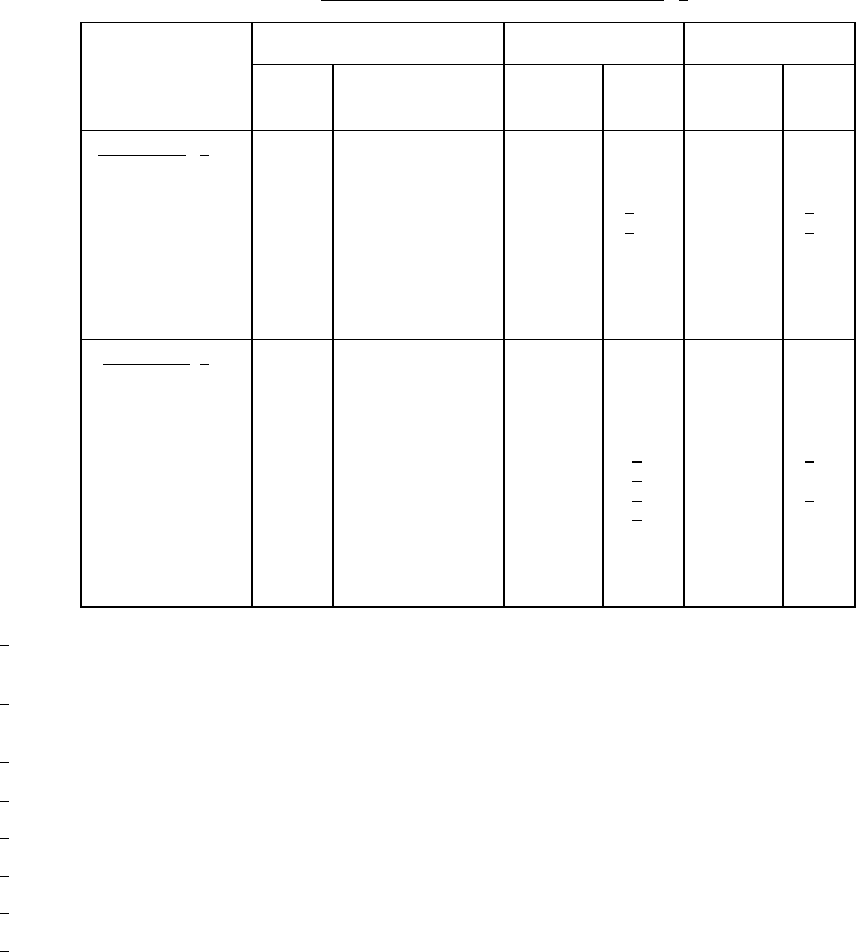

TABLE VIII. Group E (radiation hardness assurance tests). 1/

Test

MIL-STD-883 Class level S Class level B

Method

Condition Quantity/

accept

number

Notes

Quantity/

accept

number

Notes

Subgroup 1 2/

Neutron irradiation

a. Qualification

b. QCI

Endpoint electrical

parameters

1017

+25°C

As specified in

accordance with

device

specification

a. 11 (0)

b. 11 (0)

3

/

3

/

a. 11 (0)

b. 11 (0)

4

/

4

/

Subgroup 2 5/

Steady-state total

dose irradiation

a. Qualification

b. QCI

Endpoint electrical

parameters

1019

+25°C

Maximum supply

voltage

As specified in

accordance with

device

specification

a. 4 (0)

2 (0)

b. 4 (0)

2 (0)

a. 6

/

8

/

b. 6

/

8

/

a. 22 (0)

b. 22 (0)

7

/

7

/

1

/ Parts used for one subgroup test may not be used for other subgroups but may be used for higher levels in the same

subgroup. Total exposure shall not be considered cumulative unless testing is performed within the time limits of the

test method.

2

/ Waive neutron test for MOS IC devices except where neutron susceptibility is less than 10

13

neutrons/cm

2

(e.g.,

charge coupled devices, BICMOS, ect.). Where testing is required, the limit for neutron fluence shall be 2x10

12

neutrons/cm

2

.

3

/ Per wafer lot. If one part fails, seven additional parts may be added to the test sample with no additional failures

allowed, 18(1).

4

/ Per inspection lot. If one part fails, seven additional parts may be added to the test sample with no additional failures

allowed, 18(1).

5

/ Class level B devices shall be inspected using either the class level B quantity/accept number criteria as specified, or

by using the class level S criteria on each wafer.

6

/ Per wafer for device types with less than or equal to 4,000 equivalent transistors/chip selected from the wafer at a

radius approximately equal to two-thirds of the wafer radius, and spaced uniformly around this radius.

7

/ Per inspection lot. If one part fails, 16 additional parts may be added to the test sample with no additional failures

allowed, 38(1).

8

/ Per wafer for device types with greater than 4,000 equivalent transistor/chip selected from the wafer at a radius

approximately equal to two-thirds of the wafer radius and spaced uniformly around this radius.