80S-15贴片机 - 第480页

SIPLACE 80 S/ F/G Service M anual 11 Control Unit Edition 04/97 11 - 11 11.5 Wrap Connectio ns of Machine Controller MC2 (rig ht-hand side, appli es to 80 S only) 11.5.1 KSP-M18-A16 C8451-A45-A51-X Machi ne Controller Th…

11 Control Unit SIPLACE 80 S/F/G Service Manual

Edition 04/97

11 - 10

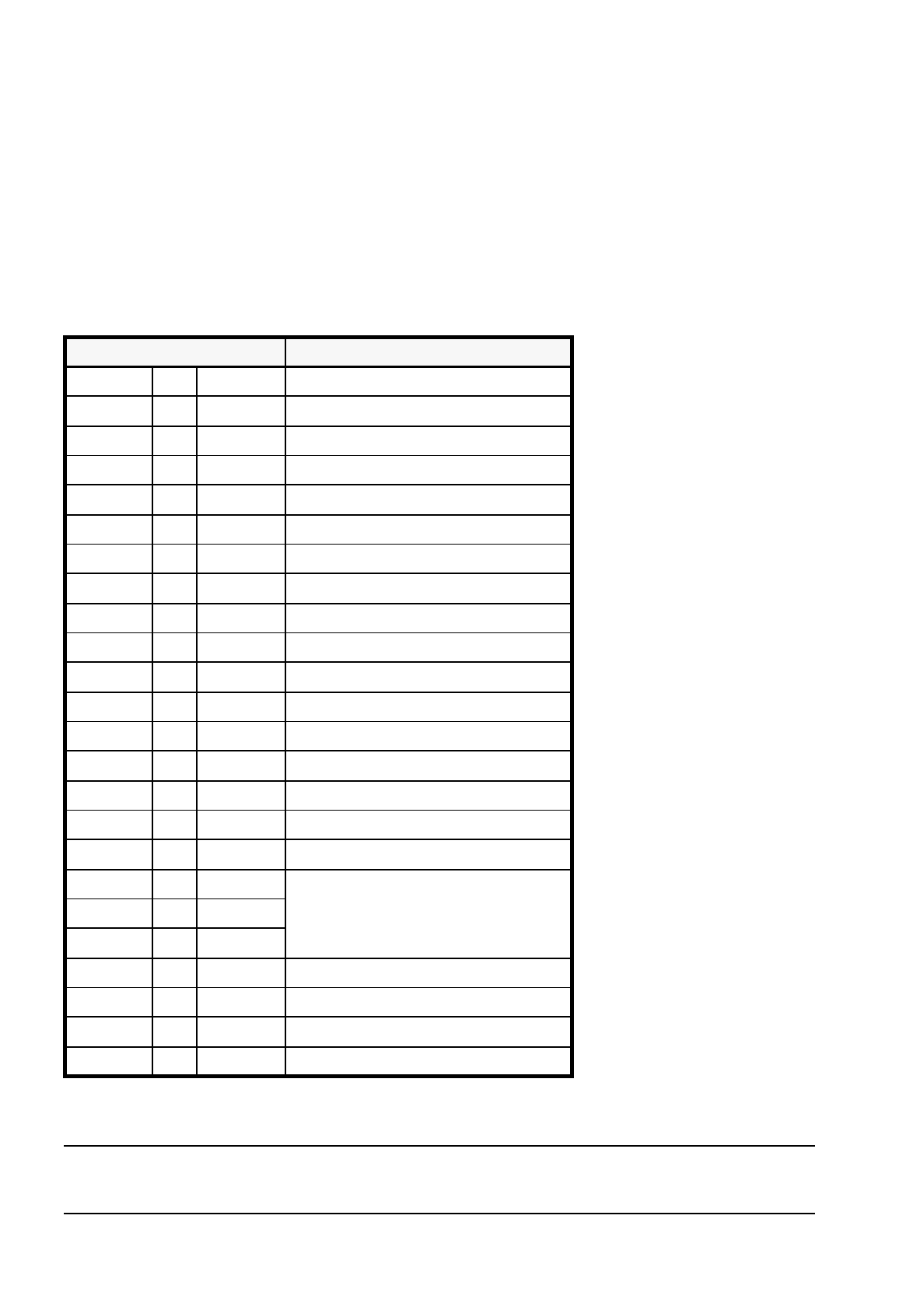

11.4 Wrap Connections of Machine Controller MC1 (left-

hand side)

11.4.1 KSP-M18-A16 C8451-A45-A52-X Machine Controller

The following jumpers must be present:

NOTE:

Wrap connections which differ from the standard configuration are marked by an asterisk (*).

Connection Significance

WM1/11

→

WM1/12 Operation without 80C187 co-processor

WM2/11

→

WM2/12 AMS-INIT connected to assembly

WJ2/1

→

WJ2/2 SRAM and DPRAM connected to Vcc

WC2/1

→

WC2/2 SMP HOLD sets M18 to HOLD

WM4/2

→

WM1/2 Interrupt MOD1 on IR2 Master

WM4/3

→

WM2/5 Interrupt SCC on IR3 Master

WM4/4

→

WM1/1 Interrupt MOD0 on IR4 Master

WM4/6

→

WM2/2 Interrupt WAKEUP on IR6 Master

WM4/7 *

→

WK2/8 Interrupt AMS-INT7 on IR7 Master

WM2/6 *

→

WK2/6 SOFTINT on AMS-INT5

WC1/1

→

WM1/6 SCC-Clock, 4.91 MHz

WJ3/1 *

→

WJ3/2 WAKEUP on IO address 1100H

WJ3/1

→

WJ3/6 WAKEUP on IO address 1100H

WF2/2

→

WF2/4 32K DPRAM in upper half of segment

WN2/1

→

WN2/2 DPRAM address on AMS bus 50000H

WN2/2

→

WN2/4 DPRAM address on AMS bus 50000H

WJ1/1

→

WJ2/5 0 waitstates command delay

WJ1/4

→

WJ2/6

4 waitstates command delay for SMP bus

access

WJ1/4

→

WJ2/7

WJ1/4

→

WJ2/8

WF1/2

→

WF1/3 V24 D2 on SCC

WM3/9

→

WM4/10 64 Kilobyte EPROMs

WM3/10

→

WM4/11 64 Kilobyte EPROMs

WM3/11

→

WM4/12 64 Kilobyte EPROMs

Tab. 11.4 - 1 Wrap connections of the KSP-M18-A16 C8451-A45-A52-X machine controller

SIPLACE 80 S/F/G Service Manual 11 Control Unit

Edition 04/97

11 - 11

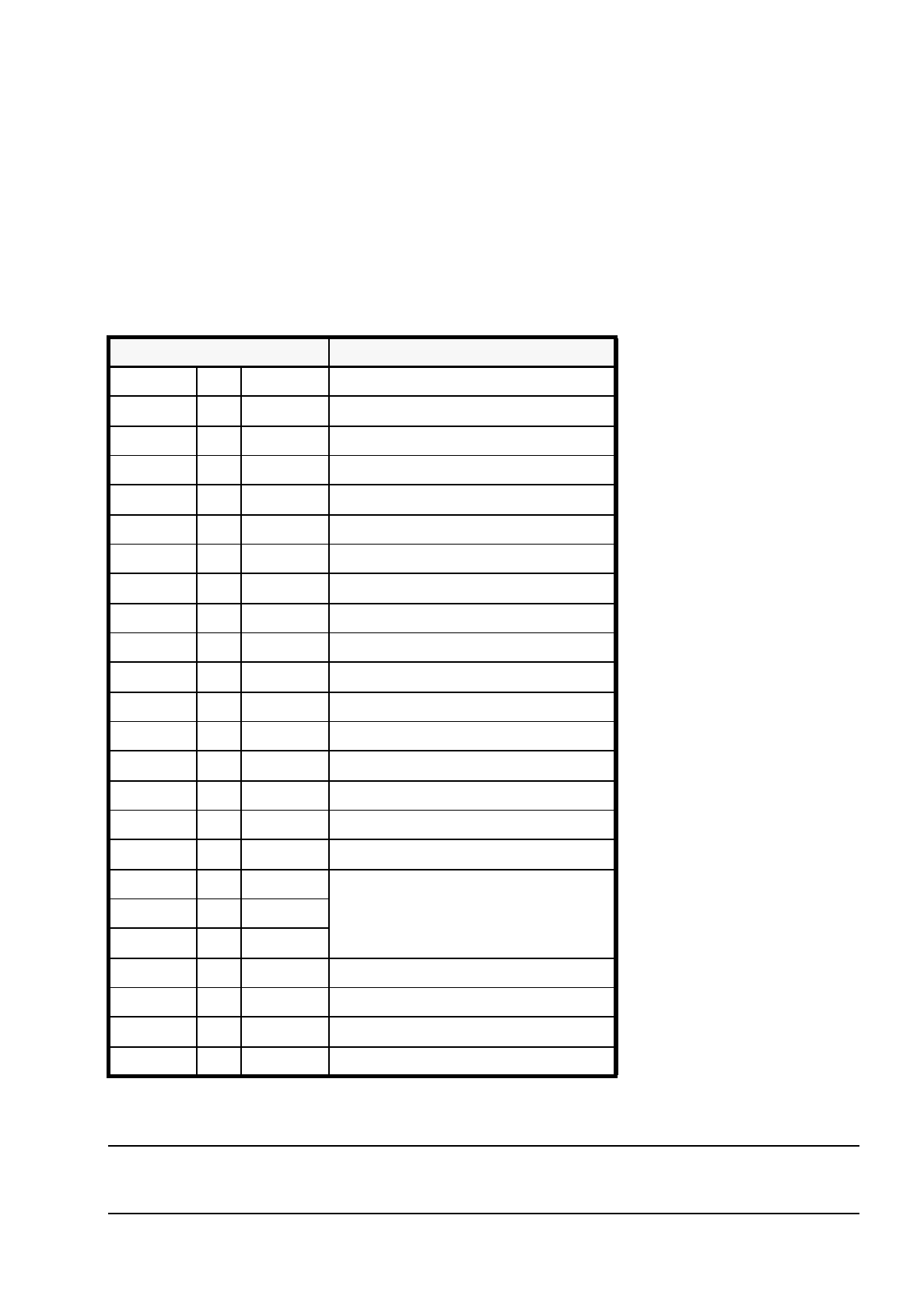

11.5 Wrap Connections of Machine Controller MC2

(right-hand side, applies to 80S only)

11.5.1 KSP-M18-A16 C8451-A45-A51-X Machine Controller

The following jumpers must be present:

NOTE:

Wrap connections which differ from the standard configuration are marked by an asterisk (*).

Connection Significance

WM1/11

→

WM1/12 Operation without 80C187 co-processor

WM2/11

→

WM2/12 AMS-INIT connected to assembly

WJ2/1

→

WJ2/2 SRAM and DPRAM connected to Vcc

WC2/1

→

WC2/2 SMP HOLD sets M18 to HOLD

WM4/2

→

WM1/2 Interrupt MOD1 on IR2 Master

WM4/3

→

WM2/5 Interrupt SCC on IR3 Master

WM4/4

→

WM1/1 Interrupt MOD0 on IR4 Master

WM4/6

→

WM2/2 Interrupt WAKEUP on IR6 Master

WM4/7 *

→

WK2/7 Interrupt AMS-INT6 on IR7 Master

WM2/6 *

→

WK2/5 SOFTINT on AMS-INT4

WC1/1

→

WM1/6 SCC-Clock, 4.91 MHz

WJ3/1

→

WJ3/6 WAKEUP on IO address 1000H

WF2/2

→

WF2/4 32K DPRAM in upper half of segment

WN2/1

→

WN2/2 DPRAM address on AMS bus 50000H

WN2/2

→

WN2/4 DPRAM address on AMS bus 50000H

WJ1/1

→

WJ2/5 0 waitstates command delay

WJ1/4

→

WJ2/6

4 waitstates command delay for SMP bus

access

WJ1/4

→

WJ2/7

WJ1/4

→

WJ2/8

WF1/2

→

WF1/3 V24 D2 on SCC

WM3/9

→

WM4/10 64 Kilobyte EPROMs

WM3/10

→

WM4/11 64 Kilobyte EPROMs

WM3/11

→

WM4/12 64 Kilobyte EPROMs

Tab. 11.5 - 1 Wrap connections of the KSP-M18-A16 C8451-A45-A51-X machine controller

11 Control Unit SIPLACE 80 S/F/G Service Manual

Edition 04/97

11 - 12