IPC-2221A-2003中文版-印制板设计通用标准 - 第16页

3.2 布设设计 布设设计过程 宜 包含 公 司 内 部 尽 可能 多 的有 关 部 门 (包括制 造、 装 配 和测 试)对布设 细节 的 正 式 设计评 审 。有 关 部 门代 表对布设的 批 准 将 确保 这 些 与 产品 相 联 系 的 因 素 已被 考 虑 在设计 中 。 互连 结构设计的成功或 失败取决 于许多相应 的 关 联 因 素 的 考 虑 。 从 成品 使用 的 角 度出发 、 下 列对设计有 影响 的 典 型 参数…

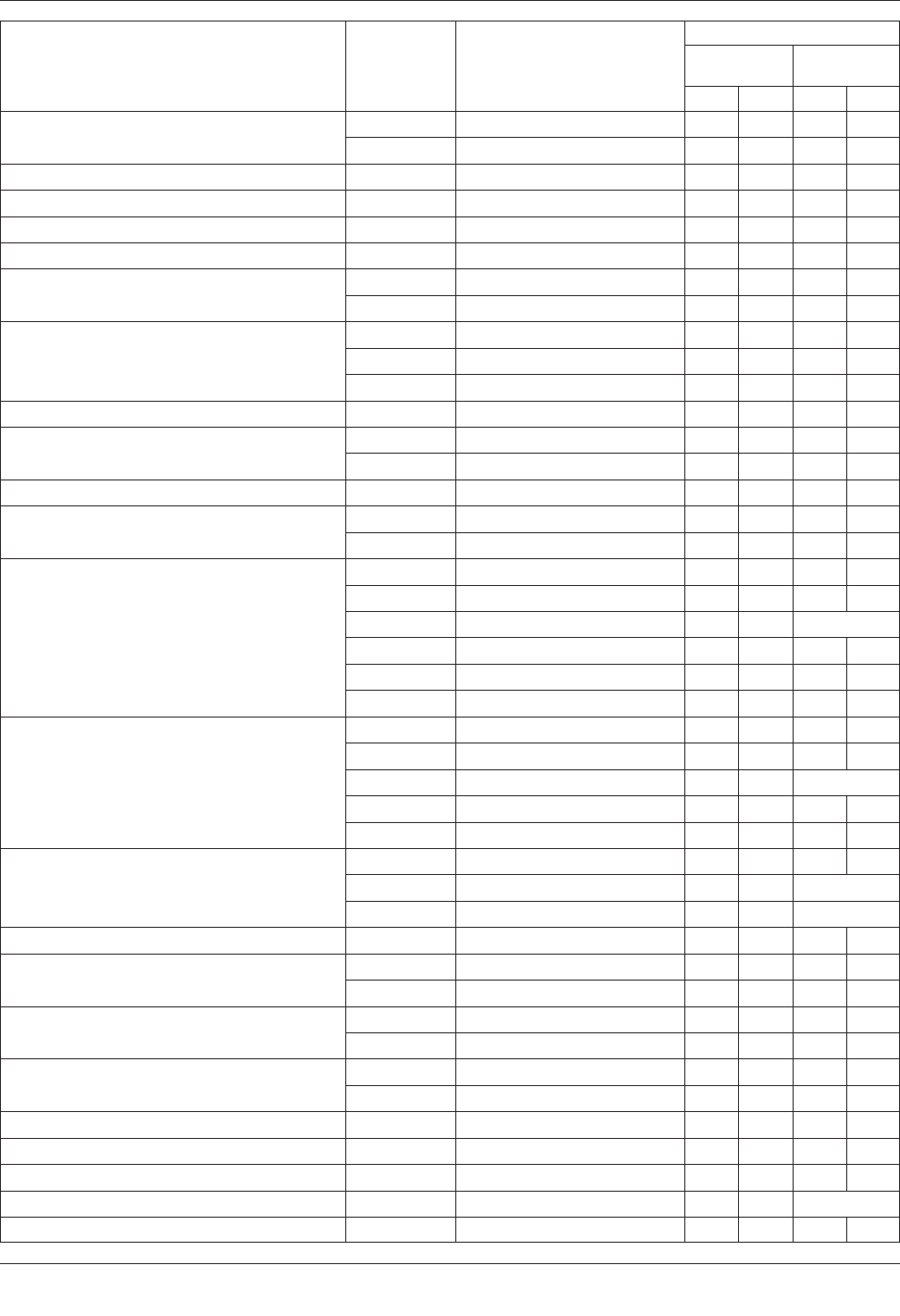

设计特征

电⽓性能 (EP)

机械性能 (MP)

可靠性 (R)

制造能⼒/产量

(M/Y)分类 性能参数

如果设计的特征值增加的影响

性能参数是

导致的性能

或可靠性结果

增加 减少 增强 减弱

导线厚度 EP 水平串扰 XX

R信号线完整性 XX

导线垂直间距 EP 垂直串扰 XX

PCB 的Zo和器件 Zo的比较 EP 反射XX

导通孔孔壁间的距离 R 电气绝缘 XX

孔环(孔口连接盘及孔底连接盘对导通孔) M/Y 可生产性 XX

信号层数 MP 物理尺寸/重量 XX

M/Y 层间重合度 XX

器件I/0节距板厚度 MP 物理尺寸/重量 XX

R导通孔完整性 XX

M/Y 导通孔镀层厚度 XX

铜镀层厚度 R 导通孔完整性 XX

厚径比 R导通孔完整性 XX

M/Y 可生产性 XX

外电镀(仅镍-Kevlar纤维板) R导通孔完整性 XX

导通孔直径 M/Y 导通孔镀层厚度 XX

R导通孔完整性 XX

层压板厚度(芯板) EP 水平串扰 XX

EP 垂直串扰 XX

EP 特性阻抗 X 设计驱动

MP 物理尺寸/重量 XX

R导通孔完整性 XX

MP 平整度稳定性 XX

预浸材料厚度(芯板) EP 水平串扰 XX

EP 垂直串扰 XX

EP 特性阻抗 X 设计驱动

MP 物理尺寸/重量 XX

R导通孔完整性 XX

介电常数 EP 反射XX

EP 特性阻抗 X 设计驱动

EP 信号速度 X 设计驱动

CET(层间的) R导通孔完整性 XX

CET(层内的) R 焊接点完整性 XX

R信号线完整性 XX

树脂的T

g

R导通孔完整性 XX

R 焊接点完整性 XX

铜延展性R导通孔完整性 XX

R信号线完整性 XX

铜的抗剥离强度 R 元件焊盘对介质层的附着力X X

尺寸稳定性 M/Y 层间重合度 XX

树脂流动度 M/Y PWB树脂空洞 XX

刚性 MP 弯曲模量 X 设计驱动

挥发物含量 M/Y PWB树脂空洞 XX

2003年5月 IPC-2221A

5

3.2 布设设计

布设设计过程宜包含公司内

部尽可能多的有关部门(包括制造、装配和测

试)对布设细节的正式设计评审。有关部门代

表对布设的批准将确保这些与产品相联系的因

素已被考虑在设计中。

互连结构设计的成功或失败取决于许多相应的

关联因素的考虑。从成品使用的角度出发、下

列对设计有影响的典型参数均宜进行考虑:

• 设备环境条件、例如环境温度、器件产生的

热、散热、撞击、震动;

•如果组装件是可维护和修复、则必须考虑元

件/电路的密度、印制板/敷形涂层材料的选

择、器件组装的可行性;

• 安装界面对安装孔的大小与位置、连接器定

位、引线突出部分的限制、部件布局、支架

及其它硬件布局产生的影响;

• 可能影响器件布局、布线、连接器装配等的

测试、故障定位要求;

• 工艺容差、例如导线宽度、间距、焊盘制作

等的蚀刻系数补偿(见第5章和第9章);

• 制造工艺的限制,例如最小的蚀刻要素、最

薄镀层厚度、板外形和尺寸等;

• 涂层和标识的要求;

• 使用的组装技术、例如表面安装、通孔安

装、和混合技术;

• 板的性能等级(见1.6.2);

• 材料选择(见第4章);

•受限于制造设备限制的印制板组装件的可生

产性;

–挠性(弯折性)要求;

–电气/电子性能;

–性能要求;

• ESD 敏感度考虑。

3.2.1 成品要求

在设计开始前应明确成品

要求。在设计过程中应重点考虑维护、服务性

要求。通常这些因素、会影响布设和布线。

3.2.2 密度评估

在上个世纪的后半叶,已经

使用过各种各样的材料和工艺去制造电子用基

材,从由树脂(例如,环氧树脂),增强材料(例如

玻璃布或纸),及金属箔(例如,铜)等制成的传

统印制板,到由各种薄膜和厚膜技术镀金属制

成的陶瓷板。然而、他们都共有一个属性:即

他们必须沿着导体布设信号线。

这同时又有每种技术能容纳多少布线的极限的

问题。表明一种基材布线能力极限的因素有:

• 基材上导通孔或孔之间的节距/间距;

• 导通孔之间能布设的导线数;

• 所要求的信号层数。

另外、制作盲埋孔的方法有利于通过有选择性

地占用布线通道来布线。被布设于完全通过印

制板的导通孔排除了在所有导体层上为布线使

用间距的需要。

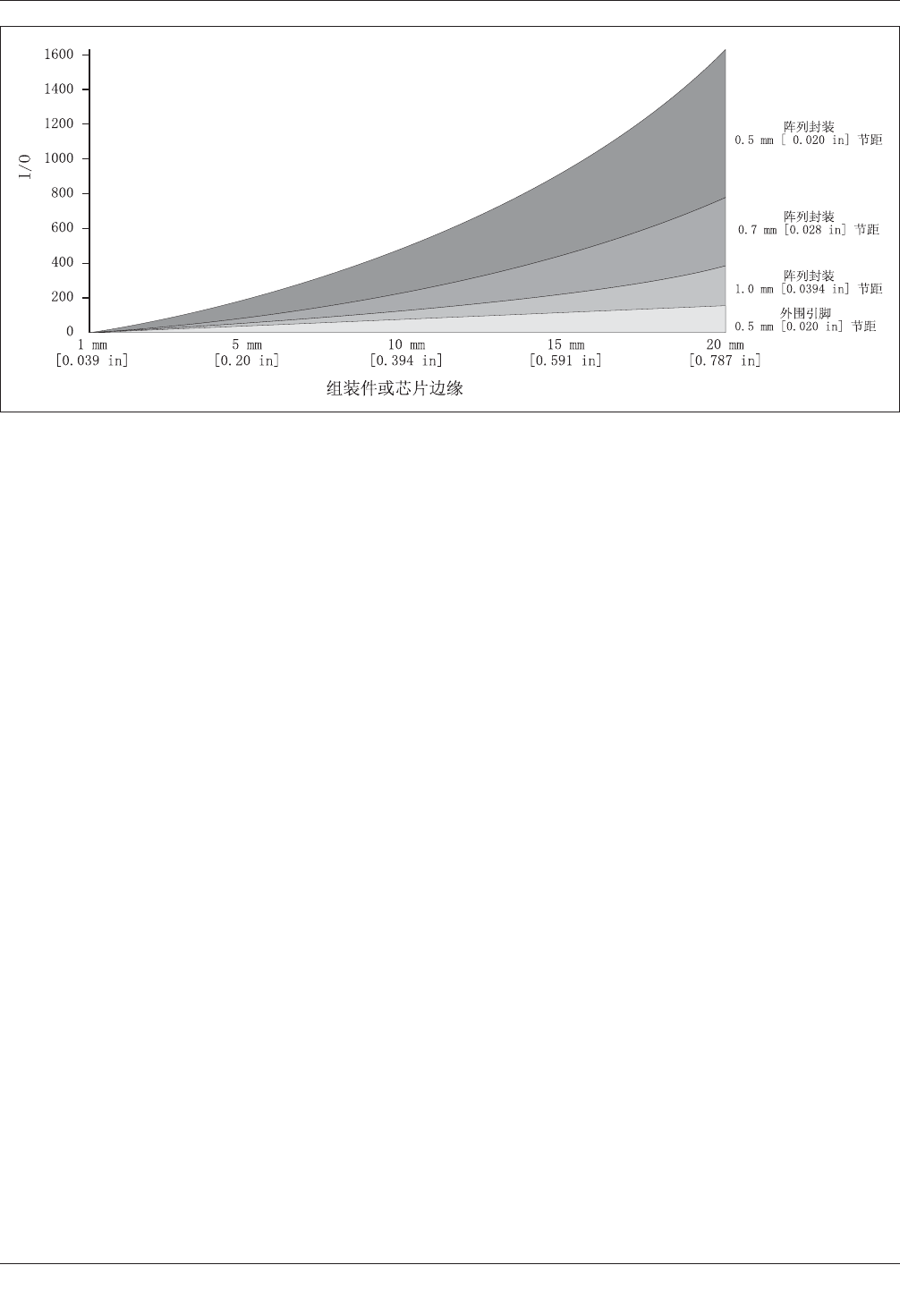

这些因素结合起来能得到一个确定一种技术的

布线能力的等式。在过去、大多数元件曾经沿

着两侧或多侧的外围有端点。然而、平面阵

列元件 节约空间且允许使用较低I/O节距(见

图3-1)。

3.3 原理图/逻辑图

原理图/逻辑图描述电气

功能和互连性、为印制板设计和装配提供信

息。适用时、原理图宜确定关键电路布设区

域、屏蔽要求、电源/接地层分布的要求、测

试点的位置以及输入/输出连接器的定位。原

理图的信息可以硬拷贝或由人工或自动生成的

计算机数据。

3.4 部件表

部件表是在组装印制板时所使

用部件和材料的列表。制造流程中最终使用的

部件和材料应在部件表或原理图中定义。制造

工艺中所用材料的可以除外、但可以包括相应

的参考信息、例如、组装件制造的有关规范及

有关原理逻辑图。

组装图中指定的所有机械部件的编号和部件列

表中指定的编号应吻合。

IPC-2221A 2003年5月

6

电气元器件、比如电容、电感、电阻、IC、

需采用参考标识(例如C5、CR2、F1、R15、U2

等)、并应与在逻辑图中指定的同一器件标号

相匹配。

建议将元件分类、例如电容、电阻、IC等、并

按照某种升序方式或数字进行排序。

部件表可以是在标准格式中手写、人工打字或

由计算机生成。

3.5 测试要求事项

通常、 在设计开始之

前、宜会同制造、组装和测试技术等召开一个

可测试性评审会。可测试性涉及到电路的可视

度、密度、操作、电路的可控制性、测试区的

划分、特殊测试要求以及规范。参见附录A列

出了可测试性准则的设计核对清单。

在可测试性评审会期间、 要建立测试工具原

则、并确定相对于板的布线状况、最有效的测

试工具性价比。

在布线过程中、任何对测试程序、测试工具有

影响的电路变动都要立即报告给有关人员以便

根据不同的情况找到最佳的折衷方案。测试能

力已发展到可校验板错误的阶段、并尽可能给

出故障的位置。测试观念和要求宜为设计验证

及制造中的故障的探测、隔离及纠正提供了便

利、并保障印制板组装件生命周期。

3.5.1 印制板组装件可测试性

印制板组装件

的可测试性设计包括系统级的可测试性问题。

在大部分应用中、包括系统级错误隔离以及恢

复要求、例如平均修复时间、超时百分比、单

一失误操作、最长修复时间等。为满足合同规

定、系统设计可包括可测试性要素、有时同样

要素可在印制板组装件中用来增强可测试性。

印制板组装件可测试性必须与设计的集成、测

试、维护的完整性相兼容。工程测试人员需对

设计的完整性和可测试性进行规划。当建立印

制板安装测试策略时、若印制板组装件为敷形

涂覆、必须考虑库存和现场测试设备的能力和

个人经验等所有因素。在不同阶段测试方法不

同。例如、第一单元的测试与全系统运行的测

试有很大差别。

在PWB设计开始之前、系统可测试性功能要求

宜提交给总体设计概念评审中。这些要求和派

生的要求在不同的印制板组装件和文件中要区

分开。系统规划级的测试标准和印制板组装件

要求的区分组装件不在本文件讨论之列。附录

A提供了一个评价可测试性设计例子。

印制板组装件测试分为功能测试和在线测试两

种基本类型。功能测试通常是测试电气的设计

功能。功能测试仪通

过连接器、测试点或测试

针床与被测板相连接。板级功能测试是在印制

IPC-2221a-3-01

图3-1 组装件尺⼨与I/O数

2003年5月 IPC-2221A

7