IPC-2221A-2003中文版-印制板设计通用标准 - 第47页

IPC-2221a-5-07 图5-7 在制板的 基 准要素 、mm IPC-2221a-5-08 图5-8 连接器 键槽 位 置 与 公差 ⽰例 、mm[in] 2003年5月 IPC-2221A 37

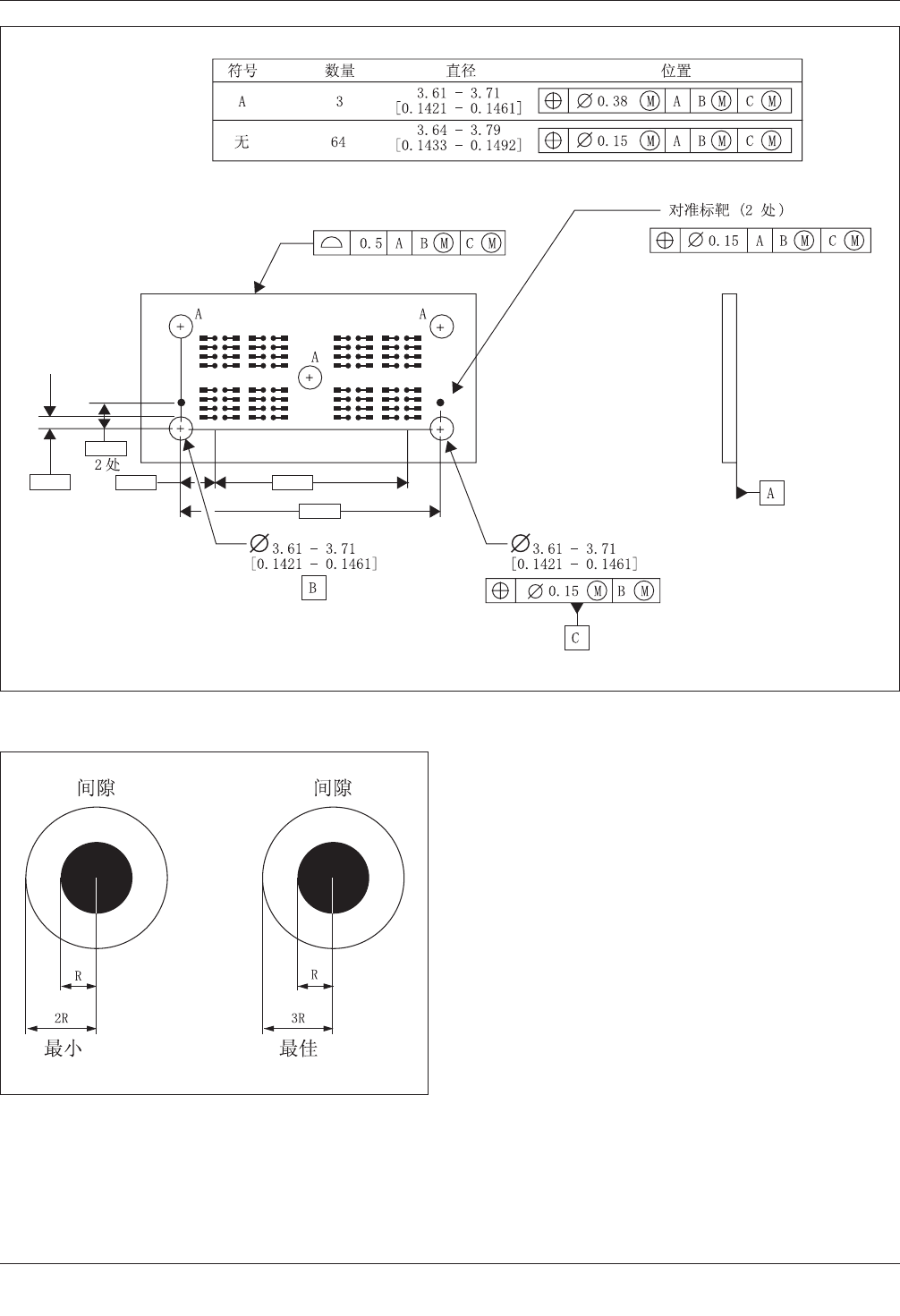

IPC-2221a-5-05e

图5-5E 采⽤⼏何尺⼨标注和公差标注的印制板图形⽰例、mm

IPC-2221a-5-06

图5-6 对准标志间隙要求

IPC-2221A 2003年5月

36

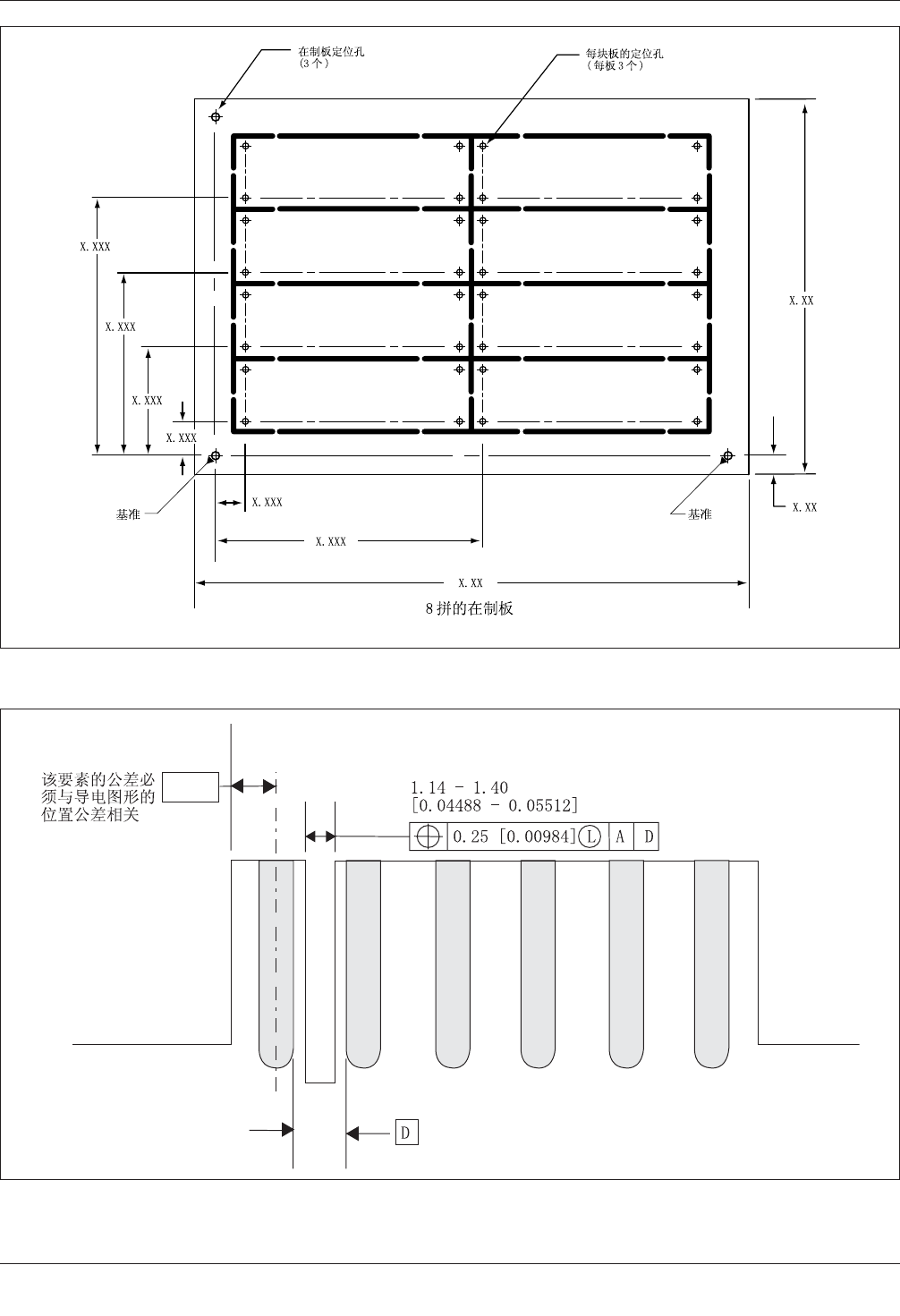

IPC-2221a-5-07

图5-7 在制板的基准要素、mm

IPC-2221a-5-08

图5-8 连接器键槽位置与公差⽰例、mm[in]

2003年5月 IPC-2221A

37

6 电⽓特性

6.1 电⽓事项

6.1.1 电⽓性能

当印制板组装件准备加敷

形涂覆时、就应适当掩蔽、或用其他方式保护

和构造、使在施加敷形涂覆时不致降低组装件

的电性能。高速电路设计宜参考IPC-D-317的

推荐。

6.1.2 电源分配事项

印制板设计宜考虑的

一个特别重要的方面是电源分配。接地可作为

分配系统的一部分。这不仅仅提供了一个直流

(DC)电源回路、也是高速信号一个交流(AC)参

照面。下面一些内容宜加以考虑。

整个DC配电要保持较低射频(RF)阻抗。不正确

的接地设计会导致RF发射。这是由通过不均匀

板阻抗扩展的辐射场梯度产生、并且去耦电容

器不足以有效减小板的电磁干扰(EMI)。

用足够的去耦电容可使印制板连接器电源分配

退耦。让足够的单个电源/接地去耦电容均匀

分布在整个逻辑设备板区域。将电容引线尽可

能短并连接在靠近关键回路处、可使耦合电容

的阻抗和辐射环降到最低。多层印制板中、电

源和接地分布的一项较好的技术是使用平面

层。电源和接地分布采用平面时、建议在连到

各自的内部平面之前、输入电源和地信号终止

于输入去耦电路。如需要外部电源总线、可使

用商品化总线方案、这在8.2.13说明。当使用

电源导线时、如图6-1所示、电源走线与接地

线宜尽量靠近。电源和接地线应尽量宽。电源

面和接地面在高频下实质上成为一个平面、因

此宜保持彼此相邻。

图6-1A是一个不良布设、高感应、少邻近信号

回路通道、这样会导致串扰。

图6-1B是

较好布设、能降低配电、逻辑回路阻

抗、导线串扰和板辐射。

最好的布设是图6-1C、能 进一步 减 少 EMI问

题。

在数字配电方案中、接地和电源宜首先设计、

不是像一般模拟电路那样放到最后才做。所有

接口技术、包括电源、宜沿单基准边或区域布

线。要避免异端互连。不能避免时、电源和地

宜小心走线、远离有源电路(见图6-2)。在互

连基准边、所有接地结构要做得尽量厚。

器件间宜尽量使用最短的导线。印制板宜划分

为高、中、低频电路区域(见图6-3)。

6.1.3 电路类型事项

当设计印制板装配时宜

考虑下列原则:

• 当适用时、要始终确定元件的正确极性;

•正确标识晶体管的发射极/基极和集电极(适

用时晶体管壳接地);

• 引线长度尽量短、并确定某些元件间的电容

耦合问题;

•如使用不同接地、要让各个接地总线或接地

面尽量相互远离;

• 与数字信号相反、模拟设计宜首先考

虑信号

导线、最后考虑接地面或接地线连接;

• 让对热敏感元件与发热元件尽量远离放置

(当需要时加散热片)。

6.1.3.1 数字电路

数字电路由能提供状态信

息(1或0)的电子元件组成、状态信息是整个电

路性能的一个功能。通常用逻辑集成电路来执

行这种功能、而分立元件有时也用来提供数字

响应。

集成电路元件使用多种逻辑系列。每个系列都

有自己的参数、对应不同数字传输速度、以及

提供性能需要的温升特性。一般说来、单个板

常使用同一逻辑系列、以简化导线长度单套设

计规范、导线长度为信号激励所限制。一些较

常用的逻辑系列是:

TTL - 晶体管晶体管逻辑

MOS-金属氧化物半导体逻辑

CMOS-互补型金属氧化物半导体逻辑

ECL-发射极耦合逻辑

GaAs - 镓砷逻辑

IPC-2221A 2003年5月

38