IPC-7095D-CHINESE NP 2019 - 第20页

IPC-7095D-W AM1 CN 2019 年 1 月 4 图 3-1 BGA 封装制造工艺 BGA 使用焊料凸点而非引线来进行互连 ,可消除由引线损伤和共面性带来的问题 。 1mm 至 1.5mm 节距的 BGA ,其间隙高度远超 250 μ m ,因此由焊膏印刷、贴片 、再流以及清洗工艺造成的问题大为减少。 BGA 同时 也提供了比密节距器件短得多的信号路径,在高速电路应用中,较短的信号路径十分关键。端子类型也会影响 相邻 I/…

IPC-7095D-WAM1 CN2019 年 1 月

3

JEP95 Section 4.14

球栅阵列封装 (BGA)

JEP95 Section 4.17

球栅阵列 (BGA) 封装测量和方法

JESD22-A102

Unbiased Autoclave Test Method

JESD22-B108

表面贴装半导体器件的共面性测试

JESD22-B112

封装高温翘曲测量方法

JESD22-B115

焊球拉离

JESD22-B117

焊球剪切

JESD94

Application Speci

fi

c Quali

fi

cation Using Knowledge Based Test Methodology

JESD217

Test Methods to Characterize Voiding in Pre SMT Ball Grid Array Packages

2.4 EIA

5

EIA-481

8 mm �rough 200 mm Embossed Carrier Taping and 8 mm & 12 mm Punched Carrier Taping of Surface

Mount Components for Automatic Handling

3 标准选择和 BGA 实施管理

3.1 术语和定义

术语和定义应当符合 3.1.1 至 3.1.4 以及 IPC-T-50。

3.1.1 阻焊膜限定(SMD)BGA 焊盘

阻焊膜开孔直径与 BGA 焊盘直径相等的一种印制板焊盘。

3.1.2 非阻焊膜限定(NSMD)BGA 焊盘

阻焊膜开孔直径大于 BGA 焊盘直径的一种印制板焊盘。也称作铜

限定 BGA 焊盘。

3.1.3 不润湿开路(NWO

) 不完全润湿或不润湿于印制板连接盘的再流焊膏(或助焊剂)与 BGA 焊球形成

的一种冶金物质。

3.1.4 枕头效应(HoP)

两个区分明显的冶金物质组成的焊点,它由 BGA 焊球与不完全或未熔融的再流焊膏

形成。

3.2 概述

每个电子系统都由各种接口以及印制板组件构成。一般来说,这些系统的复杂度反映在所使用的

元器件类型及其互连结构上。元器件的复杂度通常通过其物理尺寸和输入 / 输出(I/O)端的数量来判断,元

器件的复杂度越高,其互连的基板也越复杂。终端产品对成本和性能的驱动已导致元器件密度增加,从而使大

量元器件连接在可安装面积缩小的单个印制板组件上。此外,通过提高器件 I/O 端口数同时减小触点节距,增

加了单个器件功能数。触点节距的减小对组装厂和印制板制造商带来了挑战,他们会遇到操作、共面性及对准

方面的问题。

元器件封装,微处理器和存储器封装要求影响了其余电子组装的封装问题。元器件封装的驱动力是热管理、电

气性能、降低动态翘曲、可靠性、空间安装限制以及成本问题。外围器件 1mm 的节距已成为业界惯例,然而

这样的封装可容纳的引脚数不超过 84 个,较大引脚数的外围器件需要的节距为 0.65mm、0.5mm 和 0.3mm。

尽管小于 1mm 的引线节距对于减小封装尺寸是有用的,但密度的增加会给大部分制造商带来很多问题。密节

距的引线通常十分脆弱且易损(引起如共面性、引线弯曲和歪斜)。贴装这些封装时,必须采用带有视觉系统

的贴片机和托盘包装处理器。但这两项要求会大大增加设备投资成本。

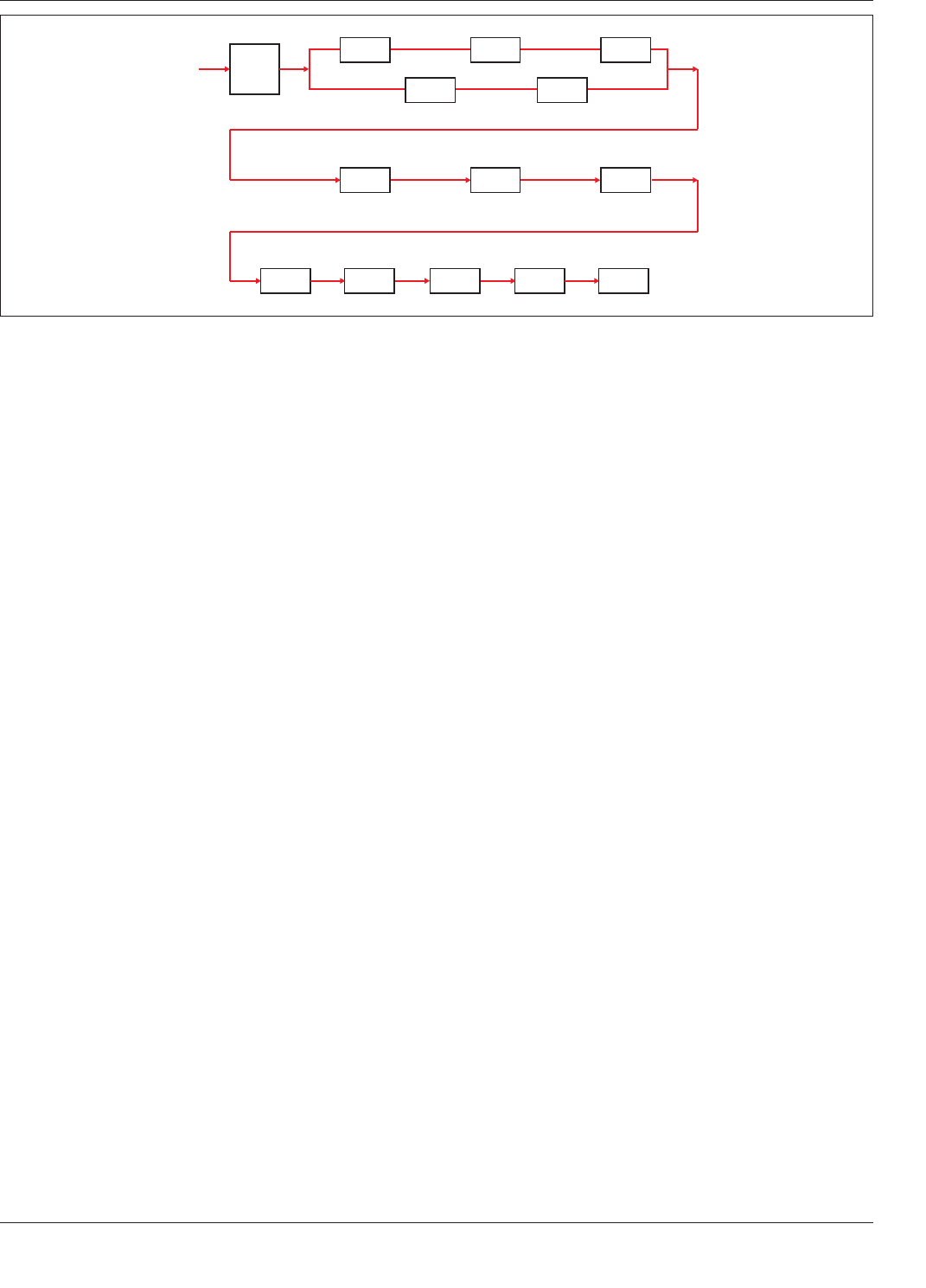

已研发出的 BGA 克服了由密节距、高引线数外围器件带给组装的挑战。图

3-1 显示了BGA封装生产工艺的

一个例子。

5. https://www.ecianow.org/standards-practices/standards/

IPC-7095D-WAM1 CN 2019 年 1 月

4

图 3-1 BGA 封装制造工艺

BGA 使用焊料凸点而非引线来进行互连,可消除由引线损伤和共面性带来的问题。1mm 至 1.5mm 节距的

BGA,其间隙高度远超 250

μ

m,因此由焊膏印刷、贴片、再流以及清洗工艺造成的问题大为减少。BGA 同时

也提供了比密节距器件短得多的信号路径,在高速电路应用中,较短的信号路径十分关键。端子类型也会影响

相邻 I/O 端的间隙。

内部或用户设计指南应该表明密节距器件与安装基板间允许增加间隙的重要性。除了免清洗助焊剂之外,差不

多平贴于印制板组件(小于 250

μ

m)的密节距器件都会产生清洁问题。为了能够获得合适的清洗效果,推荐

使用间隙高度为 0.4mm 至 0.5mm 的封装。满足这一要求将基于 BGA 的封装尺寸,因为较小的封装 x-y 外形使

清洗溶液较易于渗透。

3.3 组件架构说明

将 BGA 整合到电子组件中需有专门的工程资源来开发、实施和整合组装工艺。 尽管

BGA主导了现有的 SMT基础架构,但为了能将 BGA成功运用到现有产品配置中,还必须解决技术方面的问题。

3.3.1 连接盘图形和印制板的考量

连接盘图形对制造来说是重要的,因为连接盘的尺寸大小会影响到焊点形

成的一致性和可靠性,也会影响清洗和可测试性。由于焊点检验和返工 / 维修难度的增加,连接盘图形的设计

对 BGA 显得更为关键,因此需要搞清楚 BGA 连接盘的设计问题。有必要确保形成适当的焊点,以避免缺陷(如

桥连和开路)而达到最佳可靠性。

IPC-7351 标准提供了基于三种密度等级的连接盘图形的设计指导。BGA 的连接盘可以是 SMD,即阻焊膜覆盖

到部分连接盘;也可以是金属限定 MD 连接盘,即阻焊膜远离连接盘。以上两种方法各有其优缺点,具体怎

样选择通常取决于 BGA 的节距(影响连接盘尺寸)或者大小(影响器件质量)。

这些条件有助于定义:

•

热应力可靠性

- 金属限定连接盘帮助避免焊球塌陷时出现应力裂纹的可能。

•

机械应力可靠性

– SMD 阻焊膜连接盘帮助连接盘附着在层压板上。

除了连接盘设计,我们还应该注意到 BGA 的内排引脚要额外的互连层。增加引脚(导通孔)数会因为布线通

道减少而影响层数,层数的增加意味着印制板制造成本的增加。

1992 年,BGA 和柱栅阵列(CGA)已标准化,其节距为 1.5mm、1.27mm 和 1mm。FBGA 封装标准规定的节

距为 1mm、0.8mm、0.75mm、0.65mm 和 0.5mm,有一些节距甚至已经减小到 0.4mm、0.3mm 及 0.25mm。尽

A

HJ K

MLN

OP

B

CDE

FG

IPC-7095d-3-1-cn

A– 开始

B– 已知合格晶片

C– 晶片连接

D– 金属线键合

E– 模压封装

F– 使用倒装芯片工艺进行芯片连接

G– 芯片底部填充

H– 在 BGA 基板连接盘上施加阻焊剂或焊膏

J– BGA 基板连接盘上植球

K– BGA 基板连接盘上焊球再流

L– 进行 AOI 检测

M– 进行电气测试

N– 检验

O– 包装

P– 出货

IPC-7095D-WAM1 CN2019 年 1 月

5

管 BGA 及其相关连接盘图形存在标准配置(如 IPC-7351 描述),为了改善在元器件基板上的互连能力,一些

元器件制造商修改了标准配置。当改变标准的几何图形时,核对制造商的技术规范以确定节距、焊球尺寸以及

焊球空缺(焊球去除)等精确特征显得很重要。

使用这些极其复杂的元器件会涉及到印制板设计和组装问题。设计关注的是正确地互连所有引线并有足够的空

间来布线,而组装关注的是要连接所有引线到安装结构并保证焊点良率,避免焊点开路(枕头效应(HoP)和

不润湿开路(NWO))或短路(相邻焊点间的焊料桥连)。

3.3.2 技术比较

3.3.2.1 多芯片模块(MCM)和系统级封装(SiP)

小型的、手持式便携式系统(如手机)导致需要彼此叠

装在芯片的顶部。将单个芯片安装到有机载体封装中的原理也可用于将多个芯片连接在一起,这种技术被称为

多芯片模块(MCM)或系统级封装(SiP)。焊球尺寸和节距依然是单个元器件或包含一个以上半导体芯片的

那些元器件的主要工艺因素。表 3-1 显示的案例试图定义包含多于一个芯片的 MCM 模块。最早的芯片安装于

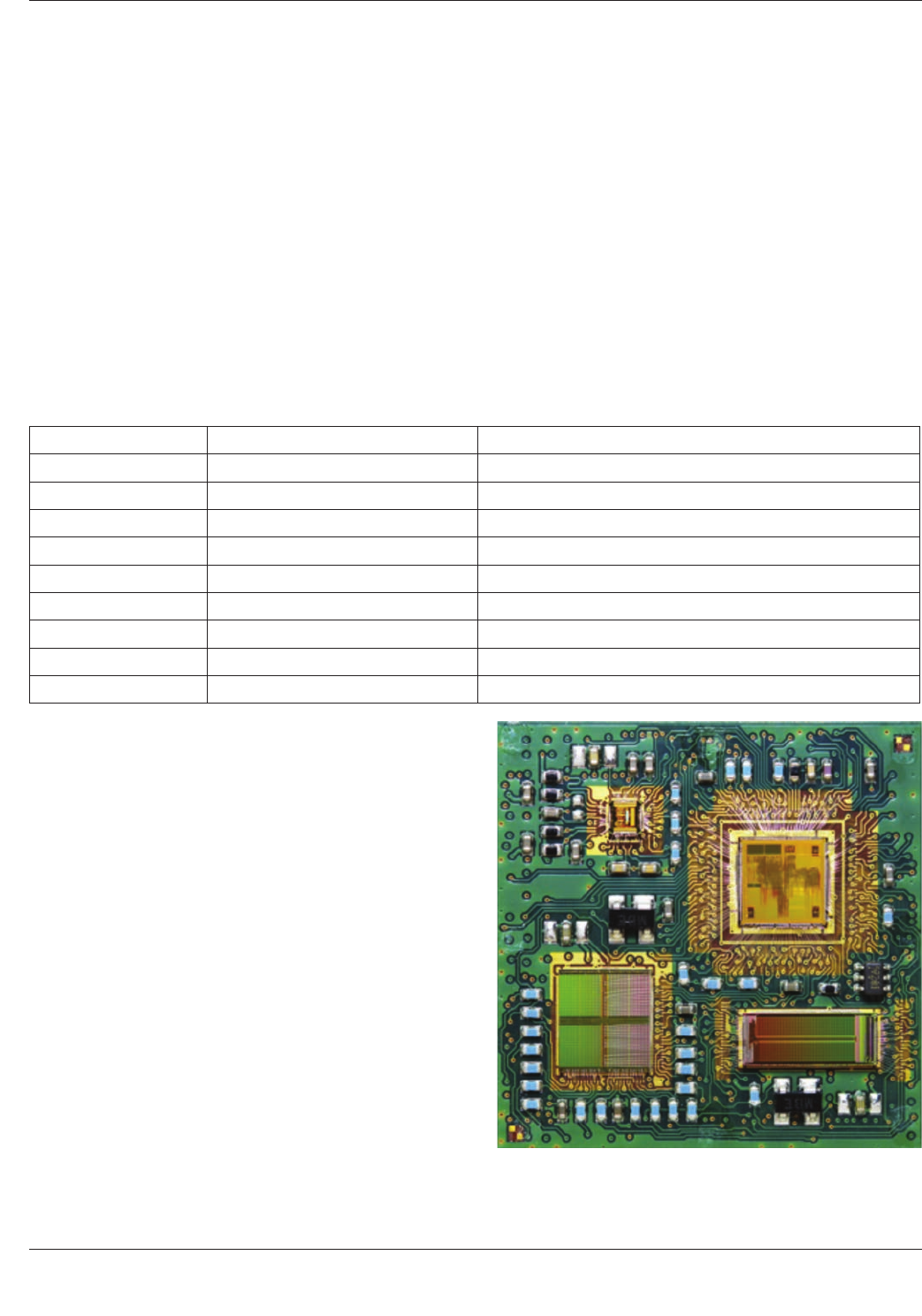

同一表面(水平)。图 3-2 是运用面阵列概念进行互连的这类产品的案例。

表 3-1 多芯片模块(MCM)定义

MCM 所用技术描述 属性

类型 1 常用技术封装 多个同种芯片,共面

类型 1S 常用技术封装 多个同种芯片,层叠

类型 1F 常用技术封装 多个同种芯片,折叠

类型 2 混合技术封装 混装集成电路技术封装,共面

类型 2S 混合技术封装 混装集成电路技术封装,层叠

类型 2F 混合技术封装 混装集成电路技术封装,折叠

类型 3 系统技术封装 混合集成电路和分立器件,共面

类型 3S 系统技术封装 混合集成电路和分立器件,层叠

类型 4 光电系统封装 光电混装技术

3.3.2.2 微处理器

微处理器通常有 40%-60% 的 I/O

端口专门用作电源和接地。举例来说,I/O 端口总数在

1,300-1,400 的封装,其中的信号端口数在 600 至 700 之

间。专用集成电路(ASICS)可能会有不同的 I/O 端口

分配方式。

I/O 信号端口的逸出布线并与其它高 I/O 数封装互连,

也将需要高密度互连技术(HDI)。随着芯片 I/O 端口数

进一步的增加,单个芯片的尺寸可能会大到无法接受,

此时就需要对整体封装方案作重新评估,包括考虑多芯

片模块封装作为替代方案。

高性能 BGA 的 I/O 信号端口数大致为 2.5 倍于普通手

持设备所用 BGA 的 I/O 信号端口数。互连密度的要求

与每个封装的信号端口数成正比,而与相邻封装间中心

至中心的节距成反比。I/O 信号端口数从 500 变化到 1,300

有 2.5 倍的增加,在封装间距相同的情况下,要求印制

板布线密度也有 2.5 倍的增加,层间导通孔或镀覆孔

(PTH)密度也会成比例的增加。因此有可能需要减少 PTH/ 导通孔的节距,同时增加印制板上的信号层数。

图 3-2 多芯片模块 (MCM) 类型 2S-L-WB