IPC-7095D-CHINESE NP 2019 - 第28页

IPC-7095D-W AM1 CN 2019 年 1 月 12 焊盘坑裂最早是在无铅焊料转化期间观察到的。为了满足无铅焊料的高温要求,配方了新的层压板树脂系统, 它比用于锡铅焊料的层压板更硬、更脆。由于更容易开裂,在生产印制板组件期间如 ICT 、分板和连接器插入 等操作时受到高动态诱发的机械应力作用下,这些层压板会失效。运输过程和产品现场使用中受到冲击和振动 应力的作用,它们也会失效。 图 3-7 焊盘坑裂示例 BGA 焊点有若干可…

IPC-7095D-WAM1 CN2019 年 1 月

11

3.7.4 返工

尽管 BGA 并不像密节距引线框架器件那样有很多的返工,但返工 BGA 器件可能是困难的。

BGA 返工工具和技术包括手动和自动技术,对 BGA 植球和对连接盘进行图形修复。在返工操作时必须考虑一

些因素,它们是:

• 热循环次数

• 植球时焊球塌陷

• 不损伤 BGA 载板上的焊盘

• 恰当修复连接盘,不损伤印制板上的连接盘

• 基于所用的合金,再连接时采用合适的再流焊温度

• 除非使用免清洗助焊剂,否则适当地清洗以去除助焊剂残留

• 去除底部填充或角落施加的粘合剂(如果有)

• 确定返工 BGA 和 / 或板组件的成本是否值得

BGA 维修和返工的具体信息参见章节 7.9。

3.7.5 成本

BGA 相比密节距外围封装还是有些许成本差异的。然而竞争方面的压力使得 BGA 成本持续下降

以满足新的目标。随着 BGA 所需的印制板层数的增加而产生更多的成本,但采用 BGA 会带来互连概念和性

能特性方面的许多优点。

下面是 BGA 封装成本较高的一些关键原因:

• 基材成本更高(细线宽 / 间距)

• 高 Tg 值的双马来酰亚胺三嗪(BT)树脂

• 散热增强

• 电气性能增强

• 极密外部节距

• 薄外形高度

• 单一封装内多个芯片

• 采用增强板以缓解动态封装翘曲

这些问题已在业界不断得到解决并且取得了相当大的进步。

因为目前还没有建立 BGA 引脚数的设计标准,每个芯片都有不同的要求,每个封装 / 芯片组合都是独特的;

因此,制造商在外围引线封装上的规模经济不一定在面阵列器件上看得到。

3.7.6 BGA中的空洞

许多厂商采用边界扫描,在线测试(ICT)、自 动 X射线检验(AXI)和自动光学检测(AOI)

的单独或组合使用来改善对 BGA 焊点的工艺控制。有些厂商通过 X 射线来寻找空洞(见 7.3),按照接收 / 拒

收限值来识别或或验证缺陷,任何类型的焊点都不可避免地出现某种程度的空洞。热应力和机械应力下空洞数

量与可靠性性能没有相关性。其它因素如间隙高度、阻焊膜开孔、连接盘设计等对可靠性的影响更具主导性。

空洞通常是在材料和工艺的影响下,在 SMT 再流焊过程中产生的。这样的空洞被称为工艺空洞或大空洞。

但是,除了 SMT 制程之外,还有许多其它的空洞来源。这些来源将在 7.5 中详细讨论。

分别建立于 J-STD-001 和 IPC-A-610 中的要求和接受 / 拒收标准,代表了基于最佳实践的共识。设计引发的空

洞(例如,连接盘上未填充的微导通孔)可能导致高于标准限值。在这种情况下,制造商和用户在考虑最终使

用环境的基础上,建立其它的接受标准。在没有设计原因引起空洞的情况下,正常预期的空洞水平应不大于

30%。附录 A 为建立过程改进目标提供帮助。

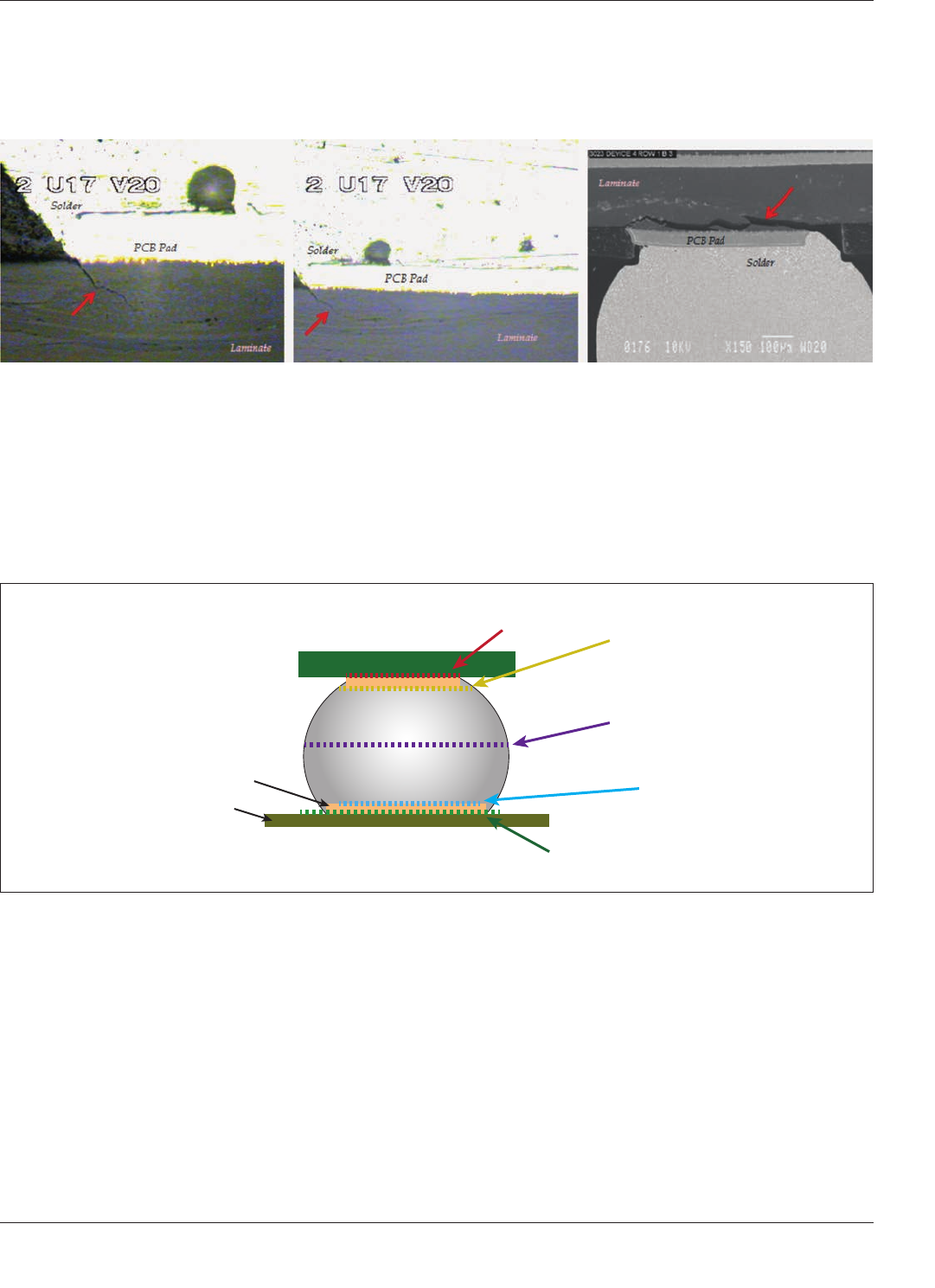

3.7.7 焊盘坑裂

焊盘坑裂是指焊盘与印制板树脂 /

编织复合物或直接与焊盘相邻的复合物的内部分离,它也

被称为“层压板裂纹”。焊盘坑裂的图例可见图 3-7(红色箭头)所示的 BGA 焊点切片图像。

IPC-7095D-WAM1 CN 2019 年 1 月

12

焊盘坑裂最早是在无铅焊料转化期间观察到的。为了满足无铅焊料的高温要求,配方了新的层压板树脂系统,

它比用于锡铅焊料的层压板更硬、更脆。由于更容易开裂,在生产印制板组件期间如 ICT、分板和连接器插入

等操作时受到高动态诱发的机械应力作用下,这些层压板会失效。运输过程和产品现场使用中受到冲击和振动

应力的作用,它们也会失效。

图 3-7 焊盘坑裂示例

BGA 焊点有若干可能的失效模式。图 3-8 强调了焊盘坑裂位置与其它形式焊点失效位置之间的关系。焊盘坑

裂失效通常发生于位置 5(图例中J),位于焊盘与印制板层压板之间。处于元器件基材与元器件焊盘之间(位

置 1)的失效模式与焊盘坑裂十分类似,但是这种失效模式通常归因于元器件封装工艺而非印制板组装工艺,

位置 1 的失效通常会在元器件可靠性评估或 3.7.2 节中提到的湿度分级处理时被发现

关于印制板互连的焊盘坑裂倾向性的特性和评估,表 3-3 列出了与此相关的 IPC 标准。

B

C

D

E

F

G

H

J

A

IPC-7095d-3-8-cn

图 3-8 BGA 焊点各种可能的失效模式

A– 焊球

B– 元器件基板

C– 连接盘

D– 印制板

E– 元器件基板与焊盘之间的失效 (位置 1)

F– 基板焊盘与焊球之间的失效 (位置 2)

G– 焊料内部失效,通常热循环后可见 (位置 3)

H– 焊球与焊盘之间的失效 (位置 4)

J– 焊盘与印制板之间的失效 (焊盘坑裂) (位置 5)

IPC-7095D-WAM1 CN2019 年 1 月

13

表 3-3 焊盘坑裂相关的 IPC 标准清单

标准编号 描述

IPC/JEDEC-9702 表征元器件板级互连的断裂强度。

IPC/JEDEC-9703 从元器件到系统级,评估印制板组件焊点可靠性的机械冲击测试指南。

IPC/JEDEC-9704 规定应变片放置及随后采用应变片对印制板进行测试的方法。该方法描述了印制板制造过程

包括组装、测试、系统集成和可能引起印制板挠曲的其它操作中,对印制板应变片测试的具

体指南。

IPC/JEDEC-9706 对于机械冲击或跌落事件,建立以电气方式并可靠侦测倒装芯片,BGA 和 SMT 板组件中焊点

开路的量测指南

IPC/JEDEC-9707 表征 SMT 器件板级互连在挠曲负载下能承受的最大可接受应变。

IPC-9708 提供测试方法以评估印制板组件材料和 SMT 焊盘下粘性电介质失效设计的敏感性。测试方法

可用于对不同印制板材料和设计参数进行比较和排序,但它们并不定义验收标准。

IPC-9709 建立一种声发射的方法来评估在机械负载下电子组件的表贴连接的性能和可靠性。

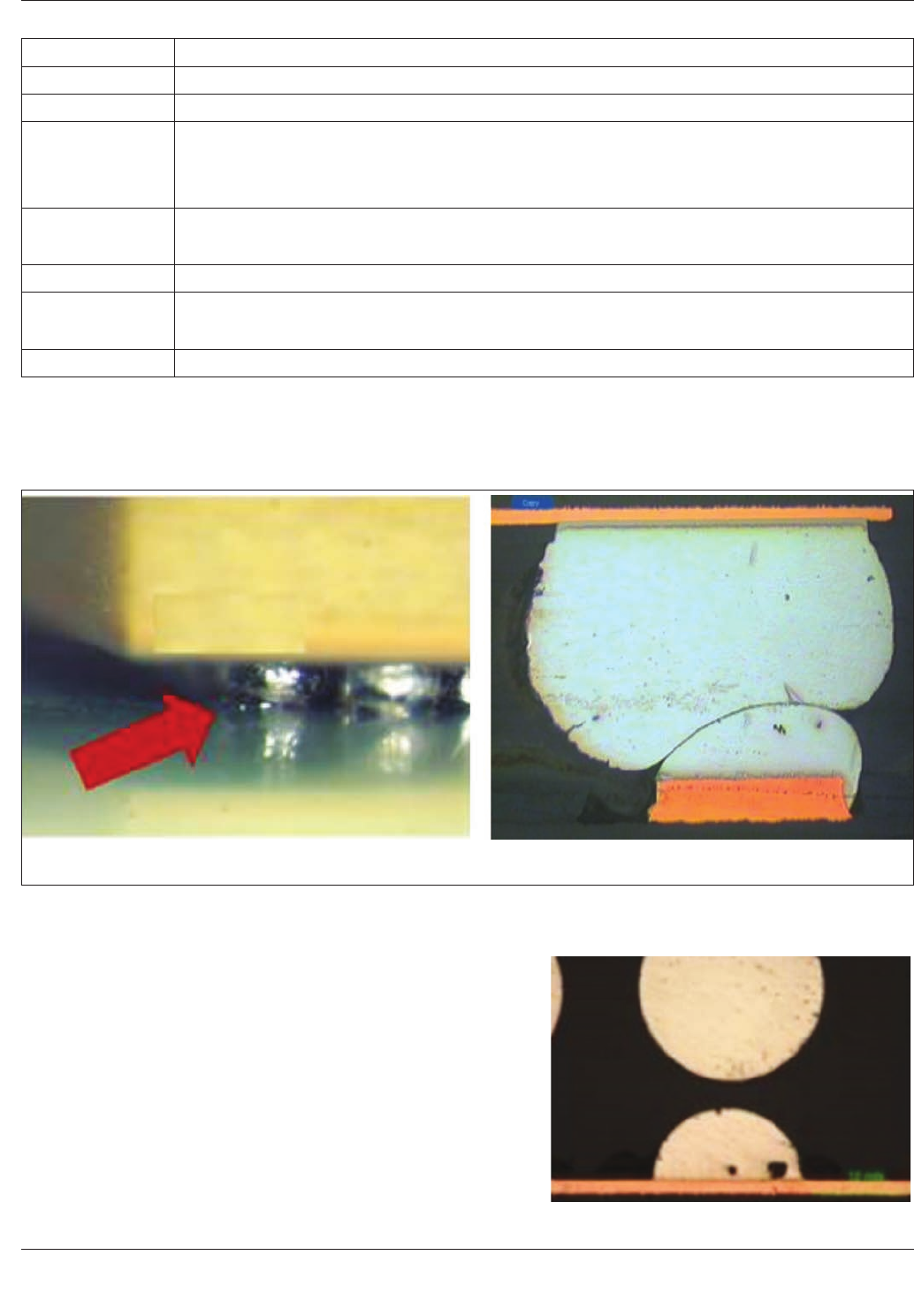

3.7.8 枕头效应(HoP)缺 陷

HoP 缺陷定义为包含两个明显冶金块的焊点,由 BGA 焊球与已再流的焊膏形成,

它们之间不完全或没有熔融在一起。此缺陷也被称作,head-in-pillow、ball-in-cup、ball-in-socket 以及 hidden

pillow。图 3-9 显示了 HoP 缺陷的两个视图。

AB

图 3-9 枕头效应(HoP)焊点缺陷的角视图(左)和切片图(右)

A– 角视图 B– 切片图

如图 3-9 中的切片图所示,两个焊料块接触但没有熔融成一体。

该缺陷可能不会导致电气开路,因为在 BGA 封装上有一定的

压力,两冶金块之间的接触电阻可能足够低会通过 ICT 测试

要求。如果两个焊料块被空隙隔开,缺陷被称为 HoP 开路。

图 3-10 显示了 HoP 开路缺陷的示例。这一缺陷将导致 ICT 测

试不良。

图 3-10 枕头效应 (HoP) 开路缺陷的切片图