IPC-7095D-CHINESE NP 2019 - 第31页

IPC-7095D-W AM1 CN 2019 年 1 月 15 元器件可靠性问题可以通过将芯片适当安装到载板而得到缓解。金属导线键合技术为人熟知,通常十分纯熟, 具有很高的良率。另一较普遍的技术是将裸芯片正面向下以倒装芯片方式安装在载板上。采用倒装芯片工艺需 要严格控制载板上的连接盘位置,使连接盘能够与裸芯片的键合位置正确地对齐。此外,如果载板的材质为有 机材料,连接工艺需要底部填充以最大限度的减小由于硅芯片和载板的 CTE 不匹配而…

IPC-7095D-WAM1 CN 2019 年 1 月

14

HoP 的根本原因是熔融焊料球和连接盘上熔融焊膏沉积物之间形成间隙。如果再流焊接时不形成该间隙,HoP

缺陷就不会形成,除非焊料球上有污染物或过度氧化。

以下是一些缓解 HoP 的解决方案:

• 通过增大模板开孔来增加印刷到连接盘上的焊膏量。

• 使用能维持活性到再流焊过程后期的焊膏,以促进焊球和焊料块的熔融,即使当印制板组件从峰值再流温区

冷却下来也能维持活性。

• 再流焊时 BGA 所有焊球的温度达到均衡。

• 再流时使用氮气氛围。

• 再流过程中使用载具使板翘曲最小化,翘曲会导致间隙的形成。

也参见 7.8.5。

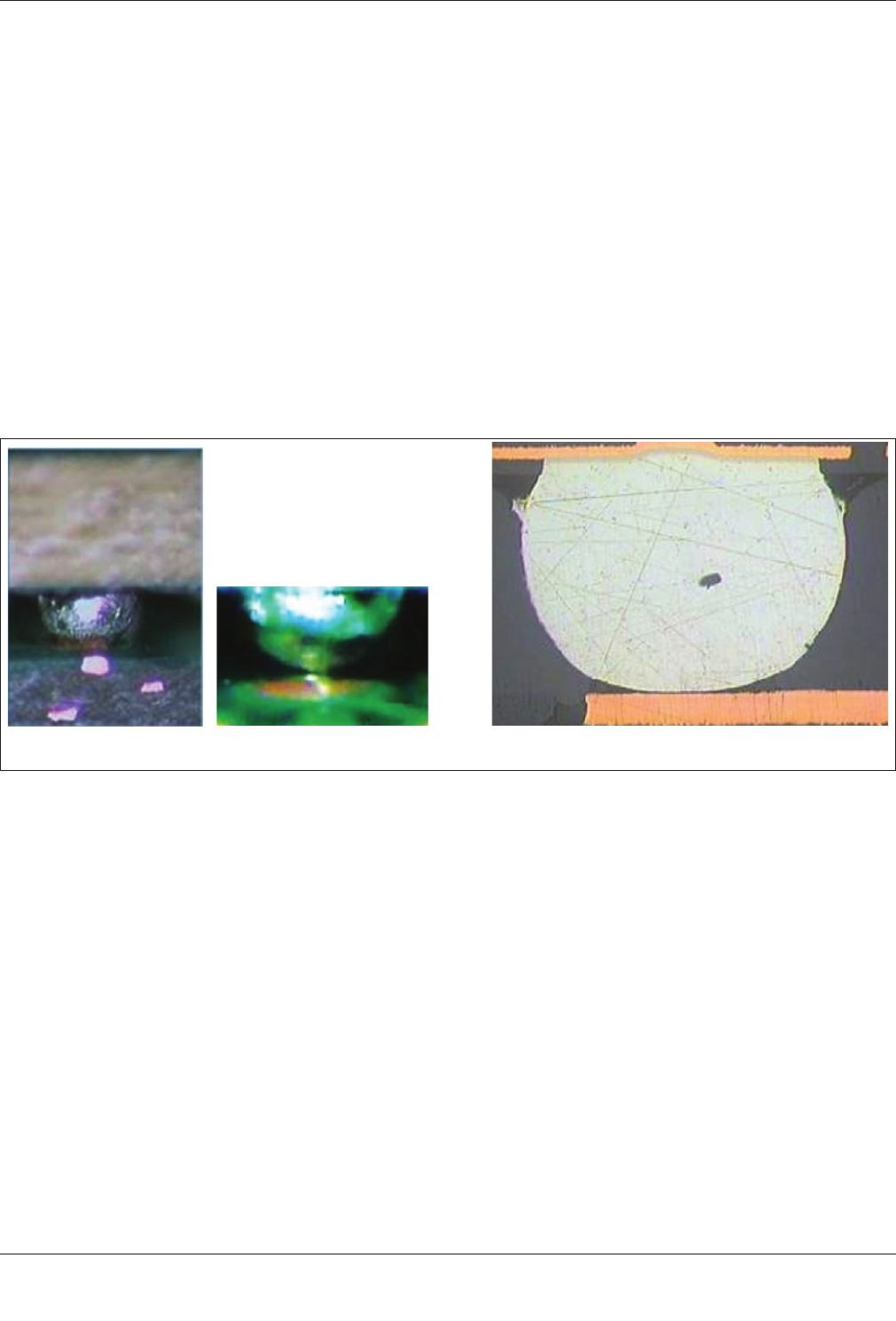

3.7.9 不润湿开路(NWO)

NWO 是由 BGA 焊球和再流的焊料(或助焊剂)之间润湿不完全或未润湿形成

一个冶金块的连接。这一缺陷也被称作未润湿、悬球、焊盘上焊球和连接盘上焊球。图 3-11 显示了 NWO 缺

陷的各种视图。

AB

图 3-11 不润湿开路 (NWO) 缺陷的侧视和切片视图示例

A– 侧视图 B– 切片视图

NWO 有很多根本原因:

• 模板开孔在焊膏印刷时堵塞,连接盘上只留下少量焊膏或没有焊膏。

• 连接盘上的污染物,会阻止融化的焊料润湿连接盘。

• 再流时 BGA 封装的翘曲会抬高焊球,焊膏粘附于焊球、抬高并脱离连接盘。在炉中的再流区域,这些焊膏

会和焊球熔融形成一个不润湿连接盘的冶金块。

由封装翘曲导致的 NWO 缺陷可以通过采用与缓解 HoP 类似的方法来减少或消除:

• 改变焊膏配方使其在再流过程中对连接盘的附着比对焊球的更强。

• 在连接盘上印刷更多的焊膏以增强焊膏对连接盘的附着力。在再流过程中采用载具来减少印制板的翘曲,并

降低焊球从连接盘分离的风险。

也参见 7.8.6。

3.7.10 可靠性问题

总的来说,焊接的可靠性可通过研究并全面了解产品的操作使用环境以及遵循 IPC-D-279

列出的可靠性设计(DfR)指南来优化。本章涵盖了 BGA 元器件特定的可靠性问题。这些问题可分为 BGA 元

器件可靠性以及 BGA 焊接到互连基板(通常为有机印制板)的可靠性。

IPC-7095D-WAM1 CN2019 年 1 月

15

元器件可靠性问题可以通过将芯片适当安装到载板而得到缓解。金属导线键合技术为人熟知,通常十分纯熟,

具有很高的良率。另一较普遍的技术是将裸芯片正面向下以倒装芯片方式安装在载板上。采用倒装芯片工艺需

要严格控制载板上的连接盘位置,使连接盘能够与裸芯片的键合位置正确地对齐。此外,如果载板的材质为有

机材料,连接工艺需要底部填充以最大限度的减小由于硅芯片和载板的 CTE 不匹配而导致的疲劳损伤

在封装基板和印制板的 CTE 不匹配最小化的情况下,板级组件的 BGA 焊点的疲劳会减轻。BGA 封装的角落

和芯片下方投影区的焊点疲劳风险最大,因为这些位置的 CTE 不匹配最严重。增加封装的间隙高度是最小化

焊点疲劳风险的一种方法。另一种方法是采用板级的底部填充,与硅晶片与有机封装基板之间的初级互连采用

的方法类似。底部填充具体内容见 7.2.2。

在机械冲击和跌落应力作用下的焊点的脆性断裂也可以通过使用板级底部填充来减轻。然而,由于底部填充的

施加过程可能花费大量的时间,对容易发生冲击和跌落的细分市场的产品中使用角落键合和边缘键合工艺。在

角落和边缘键合工艺中,粘合剂仅施加于 BGA 器件基板的角落或边缘然后固化。关于角落和边缘键合的具体

内容参见 7.2.2.2。

在选择表面处理方式时,应该考虑锡晶须和金脆所带来的风险。应该尽量避免使用厚金表面处理(厚度大于

0.25

μ

m),以减轻焊接时金脆所带来的风险,过厚的其它贵金属表面处理也应尽量避免使用。表面处理的具体

信息参见 5.3。

4 元器件考量

4.1 半导体封装的比较及驱动因素

集成电路的封装形式有许多种,就端子形状而言却只有四种:

1) 成排(单列或双列)引脚

2) 插针网格阵列(PGA)和 BGA

3) J 型引线

4) 鸥翼型引线

就 SMT 的塑封集成电路而言,最普遍的引线布局形式是 J 型引线和鸥翼型引线。在这两者之中,鸥翼型引线

形式在塑封集成电路中使用的最为广泛。随着引线数目的增加,密节距鸥翼型引线最大的问题之一是它们的脆

弱性,其后果是引线易遭受损坏(如共面性、引脚弯曲、歪斜等)。引线损伤是密节距鸥翼型有引线封装缺陷

的主要原因之一。尽管鸥翼型器件在低 /高引线数封装中使用最为普遍,BGA 封装器件仍然凭借其物理稳健性、

引脚间密度增加、小尺寸的可能性以及电气性能的增加获得了广泛的认可。

就性能而言,BGA 的信号路径要比密节距鸥翼型引线封装的信号路径要短得多,这在高速电路应用中有优势。

由于在再流焊接时能自动对齐,BGA 封装集成电路也已经展现出很高的板级装配制程良率。因为其阵列格式

可以小形状因素按比例容纳高数量的 I/O 端口,已证明 BGA 是针对高引脚数封装可行的解决方案。

4.1.1 封装特点比较

从简单的焊球连接至封装基板连接盘,面阵列元器件的端子设计和布局已得到了很大的

变化。BGA 布局是最基础和最为广泛使用的面阵列封装端子设计。焊球通过助焊剂或者焊膏再流焊接至封装

基板的连接盘上。焊球在底部的这种封装可用标准 SMT 再流工艺焊接至印制板上,当形成焊点时焊球会充分

融化并塌陷。

焊料栅阵列端子设计分配焊球,只是将焊膏印刷在封装连接盘上。产生的焊料凸点通过标准 SMT 工艺焊接至

印制板上以形成焊点。

另一种技术是采用陶瓷载板来生产栅阵列封装。陶瓷球栅阵列(CBGA)端子设计与球栅阵列 BGA 设计类似,

但采用此概念的焊球(通常为 PbSn10)在组装中并不会完全融化和塌陷。由于陶瓷基板和环氧树脂型层压板

的热膨胀系数严重不匹配,需要保持较高的间隙高度为焊点提供足够的可靠性。也有非塌陷型无铅(以前是高

铅)焊球可满足这个要求。

IPC-7095D-WAM1 CN 2019 年 1 月

16

为了解决陶瓷封装贴装在有机印制板并能适应各自 CTE 不同的需求,柱状焊料会被用作连接端子。陶瓷柱栅

阵列(CCGA)端子设计是陶瓷球栅阵列(CBGA)的延伸。CCGA 使用 PbSn10 铸型柱或 PbSn20 铜缠绕型焊

料而不是高熔焊球,以形成更高的间隙高度以及更柔性的互连,也使得可靠性显著增加。在禁止使用铅的应用

中,这种高铅合金也已经被无铅合金所取代。

一些封装采用了一种铜柱 Pillar(

μ

PILR)来减少 Z 轴 - 高度方向的膨胀,另外,有些连接器采用了一种填充

增强端子(Solder Charge)为焊料润湿提供更大的区域。

端子类型示例见图 4-1。

4.1.2 BGA 封装影响因素

强调更快、更小、更轻的电子系统使得元器件、印制板以及系统封装变得更加复杂。

组装复杂度增加的部分原因是由于小外形 SMT 封装的广泛使用,这是电子产品小型化的关键。器件触点节距

也对制造工艺的复杂性有着重要的影响。比如,随着采用越来越小的触点节距,各组装工序(如贴片、焊膏印

刷以及再流焊)所要求的精度会越来越高,检验、返工以及维修也需要越来越精密。

在选择 BGA 元器件封装时需解决的关键问题是:

• 热性能和电气性能

• 空间的限制

• 成本

不同类型系统的元器件封装要求也不相同。举例来说,高端微处理器运行频率较高,因此需要热性能和电气性

能优异的封装。

增强散热的方法有:

• 散热块

• 散热片

• 散热器

• 肋片风扇(安装在散热片上的风扇)

电气性能增强包括:

• 多层封装

• 高引脚数封装

• 封装内置电容

气密性陶瓷封装通常用于封装内置电容的应用。

4.1.3 成本关注

引线框架集成电路一直保持着相对低的制造成本。这是因为大量产品采用有限的封装布局,

使得制造商对多样的客户应用采用通用模具和成型工艺。然而,阵列封装的格式更多的是为特定的产品应用设

计和开发的。

引线数少于 200 的 BGA 器件的初始成本就很有可能超过引线框架,造成成本上升的部分原因在于其独特的单

基板应用设计以及额外的封装组装工艺步骤。在 I/O 数为 200 及以上时,引线框架集成电路和球栅阵列的成本

通常是持平的。

4.1.4 元器件操作

BGA 可用托盘载体或卷带进行包装。EIA-481 标准压花卷带包装格式通常规定在集成电

路元器件相对较小和 / 或需求产量较大时使用。JEDEC 注册过的托盘载体需要满足业界开发的设计指南(见

JEDEC 95 号出版物,章节 4.9 和 4.10)所要求的固定长度、宽度和厚度。塑封集成电路,包括 BGA,容易受

潮而在再流焊时引起封装失效。为了使器件不过度与湿气接触或暴露于湿气中,装有 BGA 的托盘需要放置于

防静电(ESD)和抽真空防潮袋内,在板级组装前应该保持托盘的密封状态(见 4.8.5))。