IPC-7095D-CHINESE NP 2019 - 第34页

IPC-7095D-W AM1 CN 2019 年 1 月 18 用户应该规定塑封 BGA 以托盘形式而非卷带形式包装。托盘载体可适应器件吸潮后潜在的烘烤要求。举例来 说,如果塑封 BGA 暴露于周边环境中的时间超过其车间寿命,它们可能需要在组装之前进行烘烤 。用于烘烤 的塑料托盘额定能承受 125 ° C 。卷带材料暴露在超过 50 ° C 的环境下会损坏载带,因此烘烤以卷带形式放置的 湿敏 BGA 可能需要花费很多天的时间。 4.1…

IPC-7095D-WAM1 CN2019 年 1 月

17

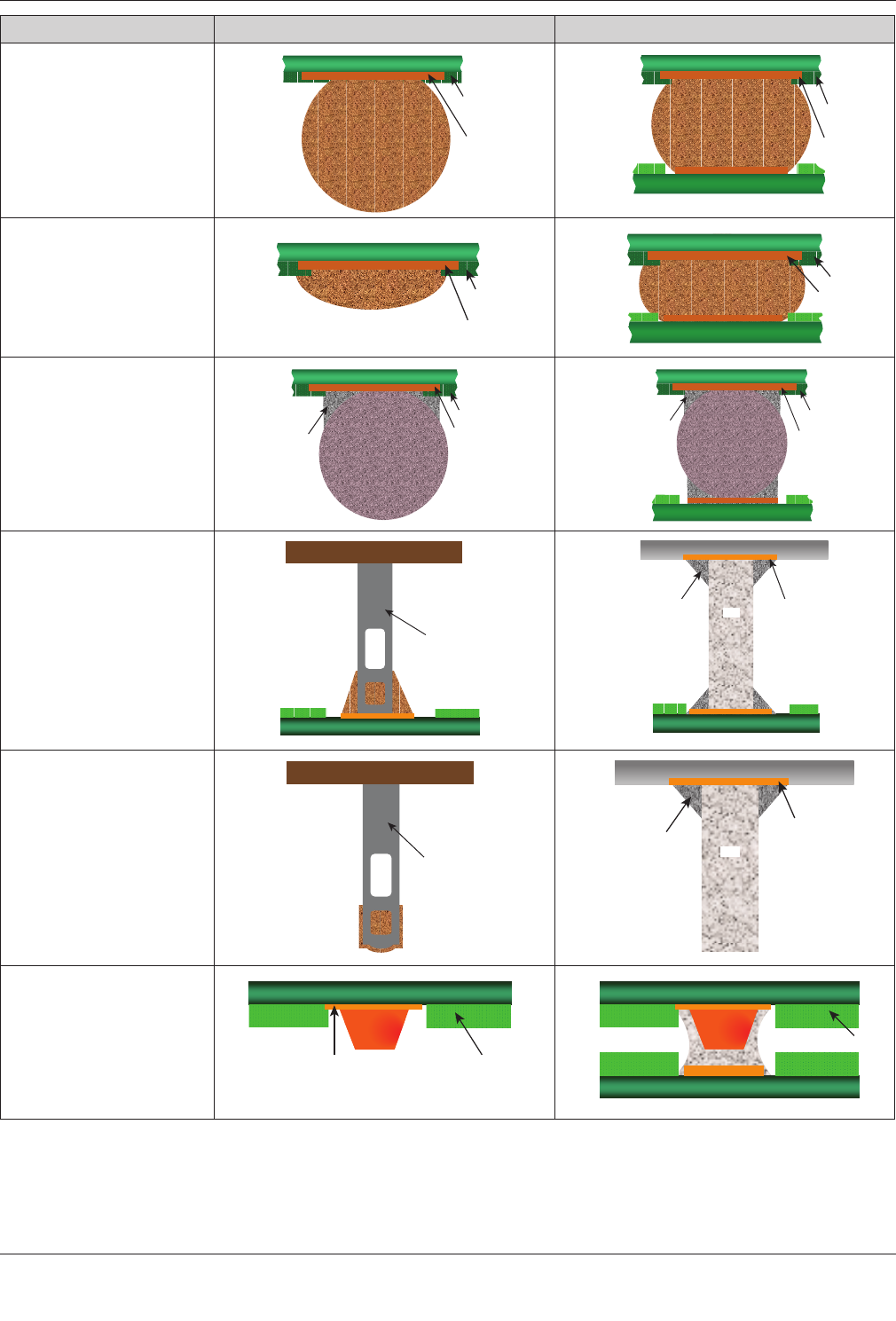

封装类型 再流焊前的端子剖面 再流焊后的端子剖面

BGA 球栅阵列

SGA 焊料栅阵列

CBGA 陶瓷球栅阵列

CCGA 陶瓷柱栅阵列

Solder Charge SMT

μ

PILR

图 4-1 面阵列封装的端子类型

B

D

C

A

B

E

D

C

A

F

A

D

C

G

A

D

C

E

Package Substrate

J

H

C

D

A

G

H

A

E

D

C

N

G

E

M

D

E

H

L

K

N

O

M

D

H

L

K

µPLR

C

A

D

µPLR

C

A

E

A– 封装基板

B– 焊球

C– 阻焊层

D– 连接盘

E– 印制板

F– 焊料凸点

G– 焊点

H– 填充

J– 高铅焊球

K– 陶瓷封装基板

L– 柱

M– 插座本体

N– 插座端子

O– 预置焊料

IPC-7095D-WAM1 CN 2019 年 1 月

18

用户应该规定塑封 BGA 以托盘形式而非卷带形式包装。托盘载体可适应器件吸潮后潜在的烘烤要求。举例来

说,如果塑封 BGA 暴露于周边环境中的时间超过其车间寿命,它们可能需要在组装之前进行烘烤。用于烘烤

的塑料托盘额定能承受 125°C。卷带材料暴露在超过 50°C 的环境下会损坏载带,因此烘烤以卷带形式放置的

湿敏 BGA 可能需要花费很多天的时间。

4.1.5 热性能

持续改善的微处理器性能和主频速度的提高已导致功率上升。当代半导体工艺使晶体管特征尺

寸减小而使芯片缩小成为可能,加之电源供电电压有降低的趋势,较高的功耗问题得以减轻(随着器件尺寸的

缩小,电场强度会增加,促使降低供电电压以避免击穿损坏)。

由于比塑料封装提供的导热性好,CBGA 通常用于高功率封装。而通过集成整块金属散热片,热加强的塑料封

装也可以满足高达 30W 的运行功率。

4.1.6 空间限制

空间限制是元器件封装尺寸减小的重要驱动力之一。这已使得 SMT 器件的广泛使用,SMT

器件不仅因为尺寸小,并且在印制板两面都能贴装。随着引脚数量的增加,即便是采用 SMT,导体与导体节

距也必须减小以使封装尺寸保持在生产的可行范围之内。

随着 BGA 封装的触点节距的减小,在特定面积下安装更多元器件的机会相应增加。印制板空间在单位面积内

可以支持更多的功能,但诸如密节距 BGA 等元器件互连时可能需要更窄的导体和更密的导体间距。对于元器

件密度较高的组件,需要较多数量的导电层来保持较小形状因素。

4.1.7 电气性能

随着频率的提高,改善阻抗控制以及封装插入损耗最小化的需求将是个问题。当进行阻抗控

制时,人们必须要考虑到端子防止或抑制反射的需要。如果这些端子与临界信号的源点和/或负载点并联连

接,会使得功率消耗增加。

电气性能驱动因素包括:

• 信号完整性

• 工作频率

• 功率

• 引脚数量

高频运行的功耗按频率的平方上升。已增加对低功率半导体的研发以试图减少复杂数字集成电路的平均功耗。

幸运的是,由于集成电路工艺已经相当成熟,每个逻辑运算单元的功率会随着器件外形尺寸减小而减少。对于

陶瓷封装的情况,即使随着高速器件的键合连接盘的增加,也可利用内在的高封装电容值以及采用封装内置的

旁路电容,使得电源和接地分布所需的引脚数量增长需求保持最小。

4.1.8 机械性能

也应该评估由机械冲击、振动和 / 或弯曲导致的 BGA 组件其它失效模式的耐受性。IPC/

JEDEC-9702、IPC/JEDEC-9703、IPC/JEDEC-9704、IPC/JEDEC-9707 以及 IPC-9708 中描述的程序为完成诸

如机械冲击、弯曲测试之类的评估以及用于现场的持续评价法提供了指南。由这些暴露类型所引发的互连失效

模式已超出焊点失效模式。通过机械试验观察到的另一个失效模式为连接盘坑裂,具体表现为 BGA 焊盘下面

的印制板树脂层的断裂。这些裂纹起始于 BGA 连接盘边缘,之后可能持续扩张穿过下面的树脂层。该断裂模

式会有各种路径,可能是在铜连接盘及其下方的树脂之间粘合失效,也可能是由于内部树脂层或穿过一个连接

线条的整体断裂导致的粘合失效。

当连接 BGA 连接盘的线路断裂时会发生电气失效。取决于机械荷载的位置,导线断裂会发生在 BGA 底部的

连接盘坑裂扩张之前或之后。这种现象会导致潜在缺陷的风险,产生长期可靠性问题。连接盘坑裂最初可能出

现于组装过程的机械操作,但此时的测试可能无法探测到电气失效。

IPC-7095D-WAM1 CN2019 年 1 月

19

后续的热 - 机械作用暴露可能会导致裂纹扩张贯穿导体,之后在现场运行中引发电气失效。即使导体没有裂纹,

层压板裂纹也可能会使更多的湿气进入,从而导致阳极导电丝(CAF)的形成。

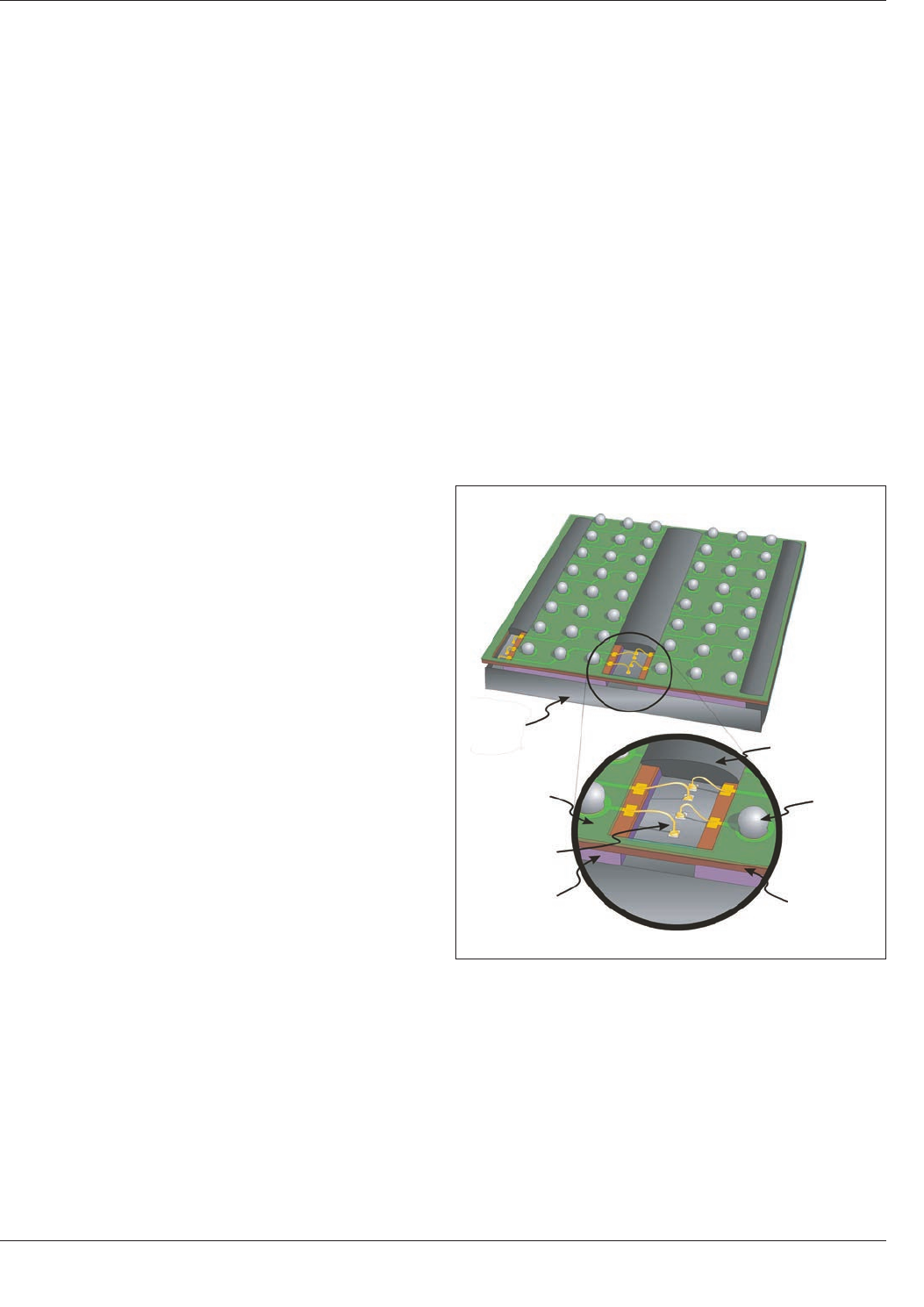

4.2 BGA 封装中的芯片安装

BGA 中的芯片有许多安装方式。根据芯片至焊球阵列信号传输的介质的不同,

有三种主要变化。这三种最基本设计中,信号分别通过导线、导电材料(倒装芯片)或导电带状引线传递。基

板材质可以是陶瓷或有机材料。封装的性质取决于基板材料的性质及其尺寸参数。本章节描述了芯片至封装组

装较为常用的方法。

4.2.1 金属线键合

BGA 金属线键合有两种主要形式:

1)板上芯片直装(COB)-芯片主表面背对基板

2)芯片上基板(BOC)-芯片主表面向上正对基板

对于这两种结构,芯片上的键合焊盘都布置在外围部分,键合线通常从芯片的周围连接到围绕芯片的基板连接

盘上。

芯片可用导电或非导电的粘合剂与基板相连。当芯片背面需要电气连接时规定必须使用导电粘合剂。但缺点是

当封装内电路布线时,无法使基板面积小于或等于芯片大小。如果芯片不需要背面的电气连接,在基板上安装

芯片时可以使用非导电粘合剂进行连接。在这种情况下,芯片下方的区域可以用作信号布线。

连接芯片所选用的粘合剂必须保证不能对线条的机械

完整性以及电气信号的完整性有负面影响。芯片连接

和粘合剂固化后,芯片就可以与基板进行电气连接

了。芯片上的键合焊盘与基板上的键合焊盘通过金线

或铝线(可行时)进行电气连接。基板上的导线通过

镀覆通孔将信号由导线键合焊盘传递至基板底部的

BGA 焊球。按照引线键合工艺,芯片与键合区域通常

采用密封保护,用密封材料顶部包封或对其进行模压

成型。密封的一种替代方法是组装后粘接一个预成型

的上盖。

在 BOC(芯片正面向下结构)中,芯片上的键合焊盘

可布置于芯片周围或成一排或成多排的形式布置于芯

片中心。基板设计有一个窄槽以容纳芯片的一排或多

排键合焊盘,用于芯片连接至基板的粘合剂放置在键

合焊盘的左侧和右侧。粘合剂可以膏状或膜状施加。

芯片的主表面(电路面)面向下到带有沟槽的基板,

裸露出芯片上的键合焊盘,典型的如图 4-2 所示。

图 4-2 芯片上基板 (BOC) BGA 结构

A – 硅片

B – 粘合剂

C – 金属线键合

D – 阻焊层

E – 密封材料

F – 焊球

G– 聚酰亚胺薄膜

A

B

C

D

E

F

G

IPC-7095d-4-2-cn