IPC-7095D-CHINESE NP 2019 - 第37页

IPC-7095D-W AM1 CN 2019 年 1 月 21 BGA 植球设备供应商推荐了一种烘烤工艺(见 J-STD-033 ) 。预成形的阵列提供了按预期阵列配置的优选合金 球。有许多阵列布局可用,且因其极少的模具成本,少量生产的成本不高。预成型阵列使用水溶性纸或临时聚 合物载体,以便细小焊球再流焊接到 BGA 时保持其位置。 这种植球方法需要随后的元器件清洁和使用前再次烘烤 BGA 。 台式返工和维修系统确保了除球和植球的效率…

IPC-7095D-WAM1 CN 2019 年 1 月

20

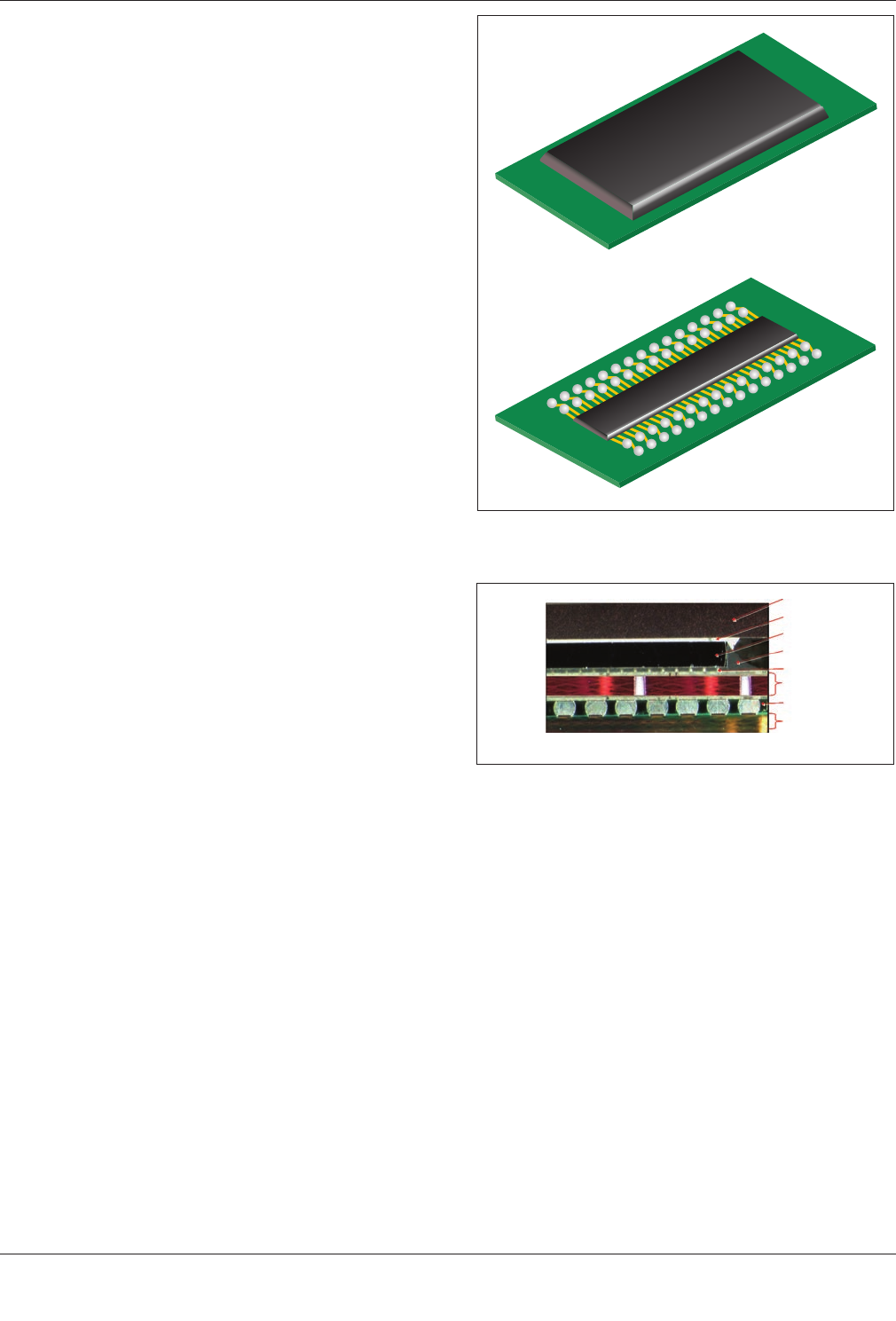

芯片连接和粘合剂固化,芯片上的键合焊盘以金属线键

合至基板上沟槽周围的相应焊盘。在金属线键合之后,

导线和裸露的芯片表面进行灌封保护。值得注意的是此

时需要空缺一行或几行网格阵列以容纳用于线键合到芯

片的基板中的沟槽。同时也需注意的是金属线键合是在

芯片中央完成的,因此芯片周围并不需要额外的外围区

域作为芯片和基板的界面。图 4-3 展示了模封 BGA 封

装的顶部和底部。

4.2.2 倒装芯片

倒装芯片(或芯片直连)消除了金属

线和芯片连接的需要。在这项设计中,预置凸点芯片的

电路面倒置向下,然后芯片电路面的连接盘通过焊料或

者导电粘合剂与基板上的相应连接盘接触相连。然而芯

片键合焊盘并不会立即与焊料或导电粘合剂连接工艺兼

容。在芯片晶圆被分割开之前,形成与凸点合金成分兼

容的焊料凸点是最常见的程序之一。要选择焊接材料以

及凸点焊盘结构材料以优化电气和机械连接,典型地如

图 4-4 所示。

导电粘合剂或聚合物连接也可适用;然而,芯片凸触

点需采用贵金属合金以便与粘合剂中的导电合金颗粒

相兼容。这种合金凸点或焊球可以通过电镀或焊球键合

工艺施加于芯片键合焊盘。如果使用焊料或各向同性导

电粘合剂,芯片与基板的间隙需要用环氧树脂进行底部

填充以确保芯片与基板界面的机械完整性。采用各向异

性导电材料去除了额外底部填充的需求。在基板与芯片

相连接之后,芯片通常会以灌封、涂覆或模封的方式进

行保护。

4.2.3 改变 BGA 端子材料

大多数商用阵列布局元

器件配置了富锡、无铅焊球触点,以符合有害物质

(RoHS)法规的限制。一些电子细分市场仍然豁免对

无铅限制的要求,特别是在恶劣环境下运行和 / 或具有

生命关键功能性的产品。虽然这些细分市场可以使用有铅焊料,但采购到不符合 RoHS 标准的商用 BGA 元

器件的难度在增加。当 BGA 元器件配置的特定合金与相应的 SMT 工艺不兼容时,制造商可以通过改变 BGA

端子合金来降低风险。这涉及到移除现有的触点(除球)并用首选合金替换(植球)。

4.2.3.1 除球

对于少量的应用,可以使用焊料芯吸或热风脱焊工具去除原始焊球。焊料芯吸效果很好,但执

行任务的技术人员必须避免刮伤或使元器件上的连接盘起翘。作为一种替代方案,可以采用为 BGA 返工特定

开发的热风脱焊系统。当大量元器件需要植球时,自动波峰焊脱球系统、机器人热风挖除或焊料浸渍工艺被证

明更为有效。无论采用何种方法,连接盘越清洁,植球获得的效果越好。

4.2.3.2 植球

植球更为复杂。必须预先烘烤元器件,以确保必须先去除从环境空气中可能吸收的任何湿气。

截留在 BGA 内的湿气在植球过程中会变成气态,这会导致严重的结构失效。

A

B

IPC-7095d-4-3-cn

图 4-3 BOC 类 BGA 模封后的顶部

A– 顶部 B– 底部

图 4-4 BGA 基板上的倒装芯片(带凸点芯片)

A– 散热片 E– 倒装芯片焊球

B– 导热膏

F– 封装基板

C– 芯片

G–BGA 焊球

D– 底部填充

H– 印制板

A

B

E

F

G

H

I

D

C

IPC-7095d-4-4-cn

IPC-7095D-WAM1 CN2019 年 1 月

21

BGA 植球设备供应商推荐了一种烘烤工艺(见 J-STD-033)。预成形的阵列提供了按预期阵列配置的优选合金

球。有许多阵列布局可用,且因其极少的模具成本,少量生产的成本不高。预成型阵列使用水溶性纸或临时聚

合物载体,以便细小焊球再流焊接到 BGA 时保持其位置。

这种植球方法需要随后的元器件清洁和使用前再次烘烤 BGA。台式返工和维修系统确保了除球和植球的效率,

但操作人员的技能将会是关键。全自动 BGA 植球系统,由于其成本高,大都仅适用于量很大或持续使用的应

用场合。

如果遵循严格的流程(包括再流焊的次数),植球工艺被证明是可靠的。使用重新植球 BGA 的优点是该元器

件对锡铅焊接工艺是兼容的。然而,缺点是元器件植球所需的成本和时间,以及元器件暴露于过高温度下引起

的潜在封装翘曲。此外,封装翘曲增加了 HoP 焊接工艺缺陷的可能。

需要注意,植球过程破坏了元器件的可追溯性,并废除了通常由原始制造商提供的关于元器件使用和储存的常

规或延长的质保期。咨询原始制造商,以确定是否有关于额外再流焊和 BGA 端子重新处理的一些限制。

如果改变焊锡球合金的工艺超出了公司的能力,可以考虑已有的一系列服务行业的解决方案。

4.2.4 非植球 BGA 的选择

植球的缺点可能促使制造商评估不含有该工艺中的选项。本章节介绍了无铅 BGA

用于锡铅焊接工艺中的一种选项。

4.2.4.1 两阶段工艺

在两阶段组装工艺中,采用一个标准的锡铅再流工艺对无铅元器件外的所有元器件进行

组装,无铅元器件则在第二阶段组装。

阶段 1:焊膏印刷到印制板的连接盘图形,随后贴装无铅 BGA 以外的所有元器件。然后将该组件采用传统的

锡铅再流焊工艺(峰值温度 210°C 至 220°C)加工。

阶段 2:在 BGA 区域选择性的施加助焊剂(而非焊膏)。然后贴装无铅 BGA 并采用标准无铅工艺温度曲线选

择性的焊接(峰值温度 240°C 至 245°C)。选择性焊接采用热风或激光辅助工艺完成,意味着只选择性地加热

无铅 BGA。

两阶段组装工艺的主要优点是锡铅和无铅元器件的完整性和可靠性保持完好,因为它们只经受了为其设计的温

度曲线。而这种方法的缺点是:

• 一些元器件制造商可能会取消对其元器件的保证

• 加工将需要额外的资源

• 总体制程交付周期会延长

• 组装厂内部需要有选择性焊接的能力(热风维修工具或选择性激光焊接系统)

此外,也要考虑较高的加工温度对印制板和相邻元器件的潜在影响。

4.2.4.2 混装共晶和亚共晶焊料加工

植球的另一种替代方法是在锡铅焊接过程中使用较高温(折衷)再流温

度曲线,来生成混合冶金焊点。这个工艺可能会形成一个完全混合(匀质的)或金相分隔的焊点,这取决于再

流温度曲线参数和焊料合金的相对用量。锡铅焊膏材料通常是共晶的,需要最大约 220°C 温度熔融并完成连

接过程。而典型的无铅再流焊要求温度范围为 235°C 至 245°C,以确保均匀的合金熔融,远高于锡铅焊料工艺

再流温度曲线 220°C 的限制。一些高性能的产品设计团队已经进行了测试,并与他们的元器件制造商合作开

发了不会导致元器件完整性问题的可接受的增温再流温度曲线。

虽然元器件材料通常足够稳健能承受扩展的温度峰值,但如果组装过程中温度超过 220°C,一些元器件制造商

可能会取消对其元器件的保证。

使用增温曲线的优点是工艺参数变化最小化和对周期时间影响低。而使用增温曲线的缺点是时间成本和与额外

的尽职可靠性测试相关的成本,以及为证实元器件 / 焊点完整性是否可接受而要费力生成再流焊炉温曲线。

IPC-7095D-WAM1 CN 2019 年 1 月

22

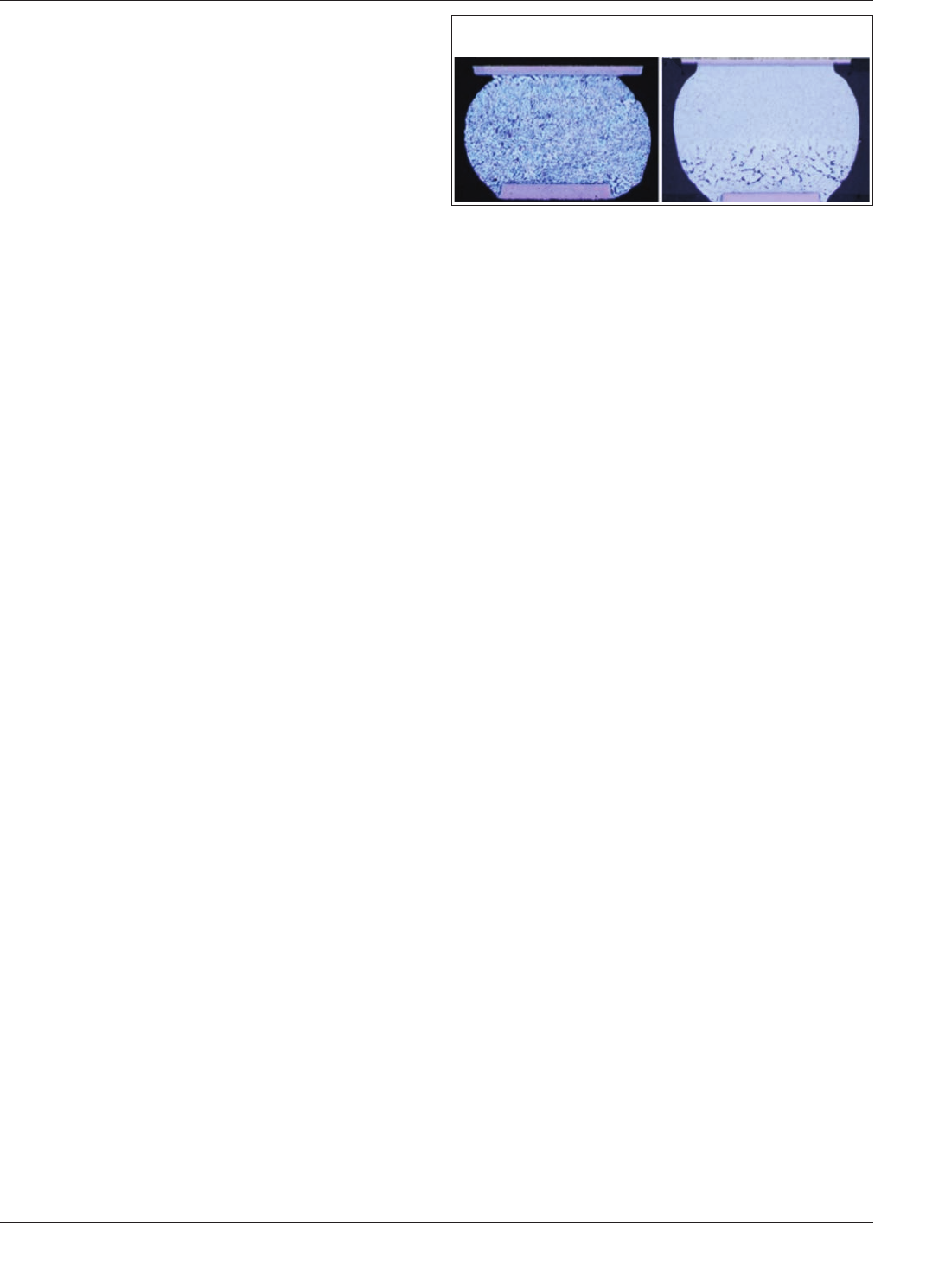

图 4-5A 显示了一个典型的具有一致微观结构的 SnPb

共晶焊点。图 4B 显示了一个具有混合冶金微观结构的

无铅焊点,展现了无铅与锡铅焊料的隔离区。

隔离的混合合金微观结构的主要缺点是焊点会受到损

害,可能需要使用底部填充材料来物理增强封装至印

制板焊点界面。

4.2.4.3 混合合金焊接的底部填充

底部填充是对采用

锡铅焊球组装无铅 BGA 元器件进行增强的一种方法。

通过将 BGA 元器件直接耦合至印制板,底部填充材料

还降低了应力不匹配(由于 CTE 差别)对焊点的影响。

采用底部填充的优势在于成本降低和标准无铅配置的 BGA 较易的可获得性。而采用底部填充的劣势在于材料

成本以及与填充材料分配并固化所消耗的时间。而且,如果底部填充材料的配方是无法返工的,印制板组件就

无法维修(见 IPC-SM-817 和 J-STD-030 作为指导)。

4.3 标准

4.3.1 BGA 行业标准

BGA 封装的标准化要考虑一些物理变量,包括每个焊球的直径以及元器件轮廓内与实

际位置相关的焊球定位精度。

对于更多封装变化的细节,包括机械特征尺寸和允许的物理公差,可参考 4.3.1.1 至 4.3.1.4 描述的 JEDEC BGA

封装指南。

4.3.1.1 BGA 封装

JEP95,章 节 4.14 定义了 BGA 和 CGA 系列。BGA 或 CGA 是封装底部分布有金属球或柱、

节距为 1.5mm、1.27mm 和 1mm 以下的正方形或长方形封装,封装的主体有施加于介电结构的金属化电路图形。

半导体芯片连接到封装本体顶面或底面。在介电结构底部的金属化球 / 柱状阵列图形形成了从封装本体与配接

特征(如印制板)之间的机械或电气连接。包含有芯片的表面可以用各种技术进行灌封以保护半导体。

4.3.1.2 密节距 BGA(FBGA)封装

JEP95,章节 4.5 把 FBGA 定义为节距减小后(小于 1mm)版本的

BGA 封装。封装载体有施加于介电结构的金属化电路图形。一个或多个半导体器件连接于介电载体的顶面或

底面。

介电载体的下方是金属球阵列图形,它形成了从封装本体到配接特征(如,印制板)的机械和电气连接。含有

芯片一面可以用各种技术进行灌封以保护半导体。对于方形 FBGA封装系列的要求,允许有三种触点节距选项:

(0.5mm、0.65mm 以及 0.8mm)及定义了四种器件外形(高度)变化。此外,0.75mm 触点节距已被归纳入芯

片级尺寸 BGA(DSBGA)封装指南,因此对于芯片级尺寸器件系列共提供了四种节距。

FBGA 总外形高度(从元器件底座面至顶部量测)大于 1.70mm。低外形密节距 BGA(LFBGA)是 FBGA 外

形高度降低后的版本。由元器件底座面至其顶部测得的 LFBGA 的总外形高度不大于 1.2mm。薄外形密节距

BGA(TFBGA)也是 FBGA

外形高度降低后的版本,由元器件底座面至其顶部测得的总外形高度不会超过

1mm。超薄外形密节距 BGA(VFBGA)也是 FBGA 外形高度降低后的版本,由元器件底座面至其顶部测得的

总外形高度不大于 0.8mm。

随着焊球触点中心间距或节距的增加,JEDEC 关于 FBGA 设计指南中允许制造商增加焊球直径的选择(如

表 4-1 所示)。JEDEC 提供的 FBGA 和 FRBGA(密节距矩形 BGA)设计指南并不支持 0.75mm 的节距;然而,

业界已注册了一些节距不一致的器件,它们并不是 JEDEC 封装。

图 4-5 采用锡铅的 BGA 焊点

(A)混合冶金(B)用锡铅工艺的无铅合金,锡铅部分混合于

SAC焊球中

AB