IPC-7095D-CHINESE NP 2019 - 第39页

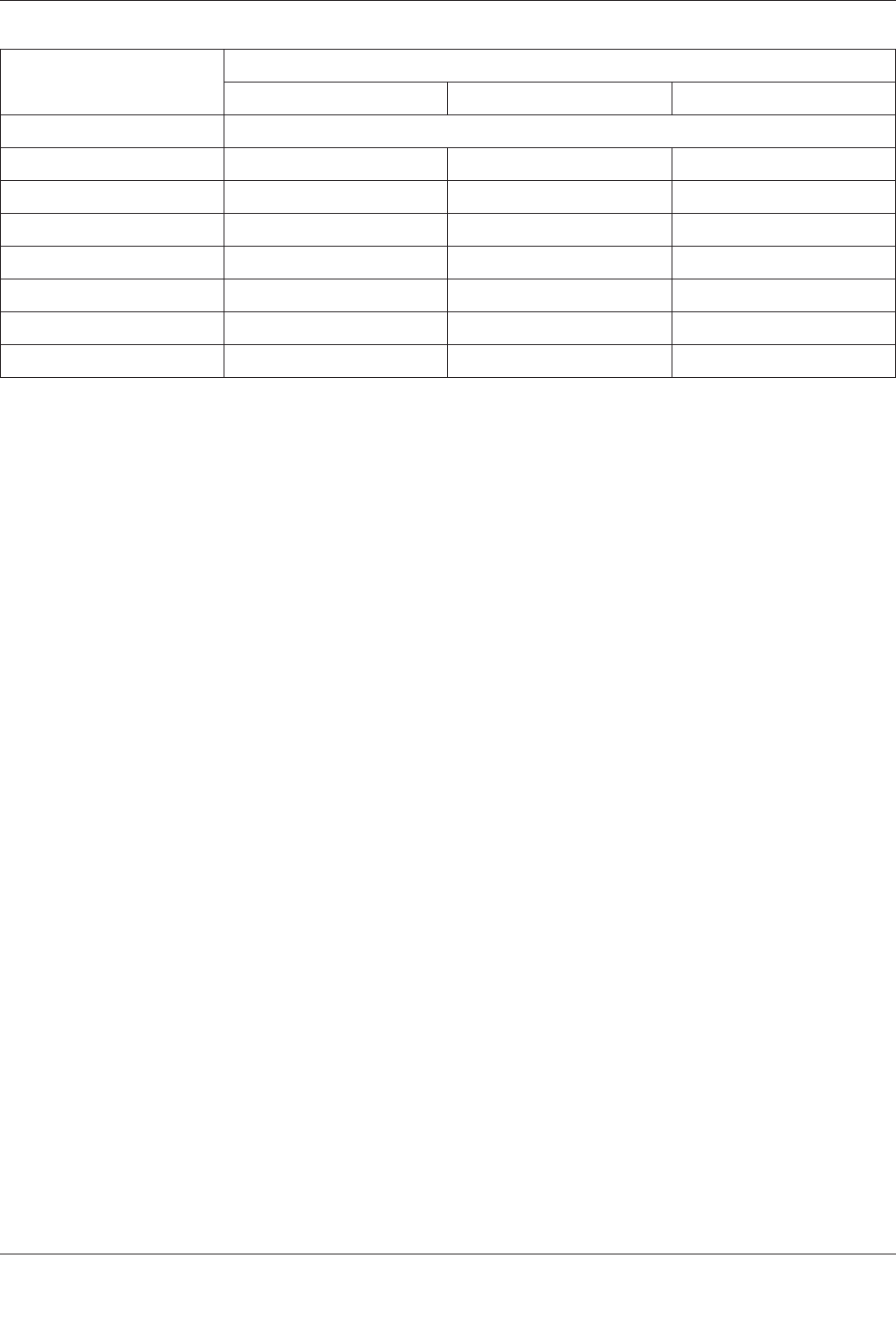

IPC-7095D-W AM1 CN 2019 年 1 月 23 表 4-1 JEDEC 标准 JEP95-1/5 允许的 FBGA 的焊球直径变化 焊球节距( mm ) 焊球直径( mm ) 最小 标称 最大 0.30 JEP95-1/5 中未定义 0.40 0.20 0.25 0.30 0.50 0.25 0.30 0.35 0.65 0.25 0.30 0.35 0.65 0.35 0.40 0.45 0.80 0.25 0.30…

IPC-7095D-WAM1 CN 2019 年 1 月

22

图 4-5A 显示了一个典型的具有一致微观结构的 SnPb

共晶焊点。图 4B 显示了一个具有混合冶金微观结构的

无铅焊点,展现了无铅与锡铅焊料的隔离区。

隔离的混合合金微观结构的主要缺点是焊点会受到损

害,可能需要使用底部填充材料来物理增强封装至印

制板焊点界面。

4.2.4.3 混合合金焊接的底部填充

底部填充是对采用

锡铅焊球组装无铅 BGA 元器件进行增强的一种方法。

通过将 BGA 元器件直接耦合至印制板,底部填充材料

还降低了应力不匹配(由于 CTE 差别)对焊点的影响。

采用底部填充的优势在于成本降低和标准无铅配置的 BGA 较易的可获得性。而采用底部填充的劣势在于材料

成本以及与填充材料分配并固化所消耗的时间。而且,如果底部填充材料的配方是无法返工的,印制板组件就

无法维修(见 IPC-SM-817 和 J-STD-030 作为指导)。

4.3 标准

4.3.1 BGA 行业标准

BGA 封装的标准化要考虑一些物理变量,包括每个焊球的直径以及元器件轮廓内与实

际位置相关的焊球定位精度。

对于更多封装变化的细节,包括机械特征尺寸和允许的物理公差,可参考 4.3.1.1 至 4.3.1.4 描述的 JEDEC BGA

封装指南。

4.3.1.1 BGA 封装

JEP95,章 节 4.14 定义了 BGA 和 CGA 系列。BGA 或 CGA 是封装底部分布有金属球或柱、

节距为 1.5mm、1.27mm 和 1mm 以下的正方形或长方形封装,封装的主体有施加于介电结构的金属化电路图形。

半导体芯片连接到封装本体顶面或底面。在介电结构底部的金属化球 / 柱状阵列图形形成了从封装本体与配接

特征(如印制板)之间的机械或电气连接。包含有芯片的表面可以用各种技术进行灌封以保护半导体。

4.3.1.2 密节距 BGA(FBGA)封装

JEP95,章节 4.5 把 FBGA 定义为节距减小后(小于 1mm)版本的

BGA 封装。封装载体有施加于介电结构的金属化电路图形。一个或多个半导体器件连接于介电载体的顶面或

底面。

介电载体的下方是金属球阵列图形,它形成了从封装本体到配接特征(如,印制板)的机械和电气连接。含有

芯片一面可以用各种技术进行灌封以保护半导体。对于方形 FBGA封装系列的要求,允许有三种触点节距选项:

(0.5mm、0.65mm 以及 0.8mm)及定义了四种器件外形(高度)变化。此外,0.75mm 触点节距已被归纳入芯

片级尺寸 BGA(DSBGA)封装指南,因此对于芯片级尺寸器件系列共提供了四种节距。

FBGA 总外形高度(从元器件底座面至顶部量测)大于 1.70mm。低外形密节距 BGA(LFBGA)是 FBGA 外

形高度降低后的版本。由元器件底座面至其顶部测得的 LFBGA 的总外形高度不大于 1.2mm。薄外形密节距

BGA(TFBGA)也是 FBGA

外形高度降低后的版本,由元器件底座面至其顶部测得的总外形高度不会超过

1mm。超薄外形密节距 BGA(VFBGA)也是 FBGA 外形高度降低后的版本,由元器件底座面至其顶部测得的

总外形高度不大于 0.8mm。

随着焊球触点中心间距或节距的增加,JEDEC 关于 FBGA 设计指南中允许制造商增加焊球直径的选择(如

表 4-1 所示)。JEDEC 提供的 FBGA 和 FRBGA(密节距矩形 BGA)设计指南并不支持 0.75mm 的节距;然而,

业界已注册了一些节距不一致的器件,它们并不是 JEDEC 封装。

图 4-5 采用锡铅的 BGA 焊点

(A)混合冶金(B)用锡铅工艺的无铅合金,锡铅部分混合于

SAC焊球中

AB

IPC-7095D-WAM1 CN2019 年 1 月

23

表 4-1 JEDEC 标准 JEP95-1/5 允许的 FBGA 的焊球直径变化

焊球节距(mm)

焊球直径(mm)

最小 标称 最大

0.30 JEP95-1/5 中未定义

0.40 0.20 0.25 0.30

0.50 0.25 0.30 0.35

0.65 0.25 0.30 0.35

0.65 0.35 0.40 0.45

0.80 0.25 0.30 0.35

0.80 0.35 0.40 0.45

0.80 0.45 0.50 0.55

已允许选择较大直径的焊球以适应刚性载板封装。较大直径的焊球可以在某种程度上弥补硅芯片和刚性印制板

结构之间 CTE 较大的不匹配。

4.3.1.3 密节距矩形 BGA(FRBGA)封装

JEP95,第 4.6 章定义了在封装底部有金属球阵列的 FRBGA。封

装载体或基板为矩形,在其介电结构的单面或双面施加有金属化电路图形。按照 JEP95,第 4.5 章相同通用术

语的表述,FRBGA 本体尺寸用 D 尺寸和 E 尺寸来定义。D 尺寸是平行于封装主轴所量出的尺寸,而 E 尺寸是

平行于次轴所量出的尺寸。因此,对于矩形封装,D 尺寸的值会比 E 尺寸大。

4.3.1.4 芯片尺寸 BGA(DSBGA)封装

JEDEC 出版物 JEP95,第 4.7 章中定义了 DSBGA。DSBGA 在封装

底部有一组金属化焊球阵列。封装的基板或载体在介电结构的单面或者双面施加有方形或矩形金属化电路图

形。半导体芯片与介电载体的上表面相连接。

在绝缘结构的底部,金属化焊球阵列图形为封装本体连接到下一级元件(如,印制板)提供了机械和电气连接。

连接芯片的表面用各种技术灌封以保护半导体。基板或载体的尺寸尽可能接近芯片尺寸。

DSBGA 是本体尺寸与特定芯片尺寸尽可能接近的一种 BGA 封装类型。这种封装也被称为真正芯片尺寸 BGA

或芯片级封装(CSP),封装本体的尺寸仅适合特定大小的芯片组装,这些封装本体的尺寸会因芯片大小变化

而变化。封装的外形可以是方形或者矩形;当给定封装为了适应新的芯片尺寸而进行重新设计时,长宽比可能

也会发生变化。功能相同但来自于多个供应商的器件可能有不同的长宽比。DSBGA 封装标准化的控制因子是

球阵列的大小和长宽比。

D 尺寸和 E 尺寸定义了 DSBGA 封装的本体大小。对于带有矩形焊球阵列的封装,阵列决定了维度的方向。D

尺寸是平行于焊球阵列主轴测得的尺寸,而 E 尺寸是平行于焊球阵列次轴测得的尺寸。对于矩形封装,没有

必要如 JEDEC JEP95,4.6 章节对 FRBGA 要求的那样,D 尺寸大于 E 尺寸。具有方形焊球阵列的 DSBGA 封

装应遵循通常的“D 尺寸大于 E 尺寸

”的 JEDEC 惯例。在 JEDEC 出版物 95 里,D 尺寸和 E 尺寸的最大值定

义用 0.5mm 作为递增步长,这个数值是通过将 DSBGA 的实际尺寸向上取整而获得(下一个 0.5mm 的边界)。

因此当采用该程序时,D 尺寸和 E 尺寸的形式通常写为 y.00 或者 y.50。

DSBGA 封装的阵列节距没有必要与 D 或 E 阵列尺寸相同。当节距不相同的情况下,相关封装的尺寸和公差由

较小节距的焊球尺寸和公差来主导。DSBGA 封装焊球阵列的控制节距总是小于 1mm。JEP95,章节 4.7 中所

描述的 DSBGA 触点节距为 0.8mm、0.75mm、0.65mm 以及 0.5mm。

IPC-7095D-WAM1 CN 2019 年 1 月

24

4.3.2 BGA 封装节距

BGA 的节距主要可分为两组。第一组包括塑料和陶瓷封装外形,其触点节距为 1.5mm、

1.27mm 或 1mm。第二组为密节距或芯片尺寸 BGA,密节距焊球触点节距为 0.8mm、0.75mm、0.65mm、0.5mm、

0.4mm、0.3 mm,对于 DSBGA 而言,节距还有 0.25mm。由于需要将 BGA 尽量做小以应对形状因数方面的压

力,如今很少有制造商还在提供节距为 1.5mm 的器件。尽管允许有节距为 0.4mm 或更小的焊球,但其应用由

于加工困难可能受限于传统 SMT 组装工艺。在确定哪一种焊球直径可用于各种组合中时,节距起到了重要作

用。表 4-2 展示了节距在 0.5mm 至 1.5mm 的塑封 BGA(PBGA)的焊球特征;而表 4-3 展示了 DSBGA 的节距。

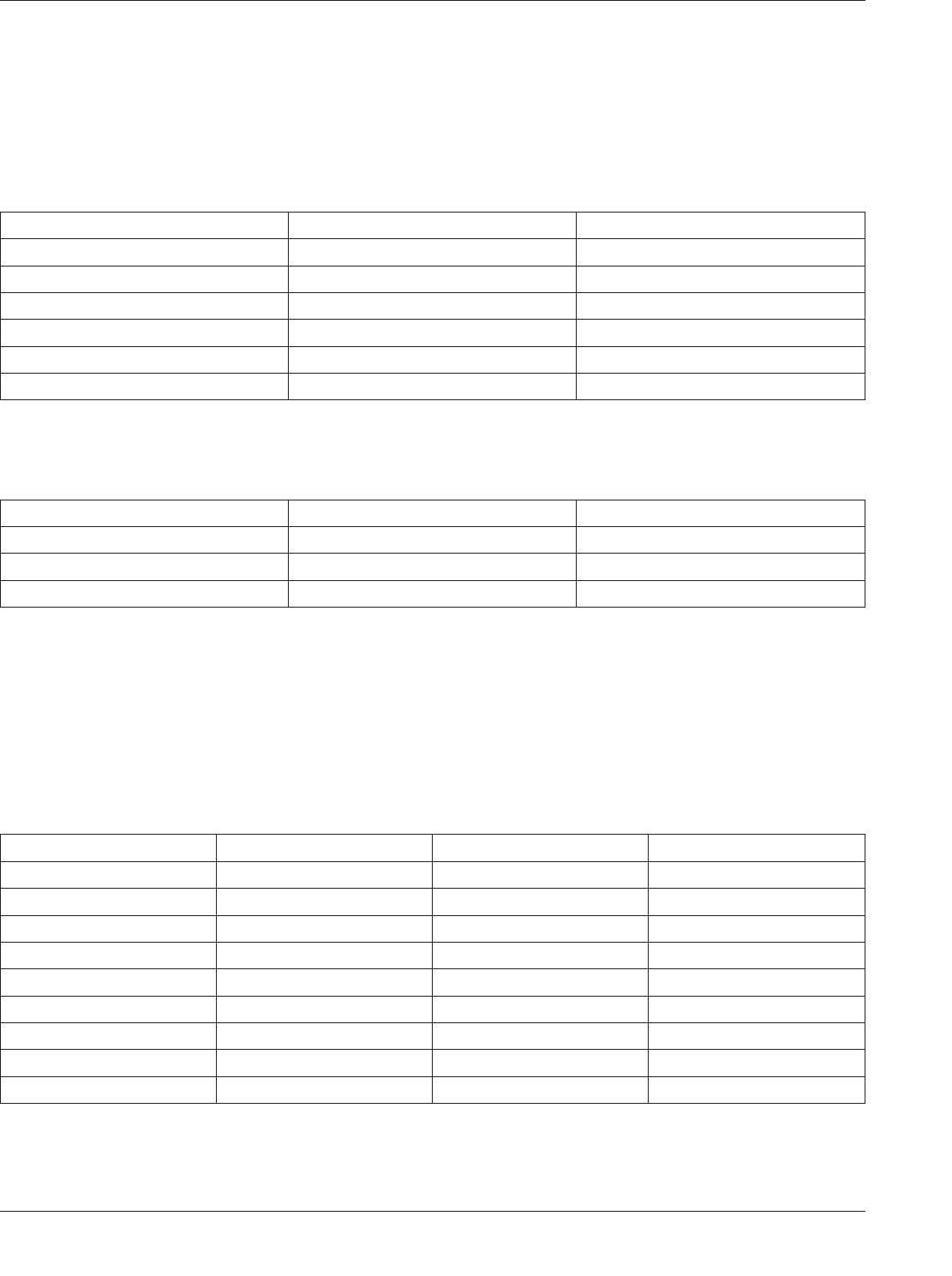

表 4-2 塑封 BGA (PBGA) 的焊球直径

标称焊球直径 (mm) 公差范围 (mm) 节距 (mm)

0.75 0.90 至 0.65 1.5, 1.27

0.60 0.70 至 0.50 1.0

0.50 0.55 至 0.45 1.0, 0.8

0.45 0.50 至 0.40 1.0, 0.8, 0.75

0.40 0.45 至 0.35 0.8, 0.75, 0.65

0.30 0.35 至 0.25 0.8, 0.75, 0.65, 0.5

尽管并非强制,非对称焊球图形使得其在自动化方向检测方面有额外的优势。在原本对称的阵列中去除其中一

个位于角落的焊球为非对称图形的典型例子。

表 4-3 芯片尺寸 BGAs (DSBGAs)焊球直径大小

标称焊球直径 (mm) 公差范围 (mm) 节距 (mm)

0.25 0.28 至 0.22 0.4

0.20 0.22 至 0.18 0.3

0.15 0.17 至 0.13 0.25

4.3.2.1 连接盘图形设计

元器件基板的连接盘图形(用来连接焊球)和安装结构(如印制板)的连接盘图形

就其直径应该越接近越好。元器件制造厂商认为印制板连接盘或元器件上连接盘应该略小于焊球直径。连接盘

尺寸的减少量取决于原始焊球尺寸,这常用来确定连接盘的平均尺寸。在确定标称特征值之间关系时,应确定

连接盘尺寸最大实体条件(MMC)与最小实体条件(LMC)之间的制造余量,即当焊球直径大于等于 0.4mm 时,

制造余量为 0.1mm,当焊球直径小于 0.4mm 时,该余量也应相应减小。

表 4-4 提供了关于 BGA 连接盘图形的数据以及对应 9 种焊球直径的变化。

表 4-4 连接盘图形设计

标称焊球直径 (mm) 缩减 标称连接盘直径 (mm) 连接盘尺寸范围 (mm)

0.75 25 % 0.55 0.60 至 0.50

0.60 25 % 0.45 0.50 至 0.40

0.50 20 % 0.40 0.45 至 0.35

0.45 20 % 0.35 0.40 至 0.30

0.40 20 % 0.30 0.35 至 0.25

0.30 20 % 0.25 0.25 至 0.20

0.25 20 % 0.20 0.20 至 0.17

0.20 15 % 0.15 0.15 至 0.12

0.15 15 % 0.10 0.10 至 0.08

许多元器件制造商使用 SMD 连接盘(见 6.2.2)。在运用这项技术时,连接盘直径的标称值应该加上阻焊膜在

连接盘上的侵入距离(通常约 0.1mm)。阻焊膜开窗大小即为需要连接的焊球直径,不过实际的连接盘尺寸应

略大以适应 SMD 连接盘的概念。应该需要注意的是由于连接盘尺寸变大,布线密度相应地就减小了。