7710PDFA - 第119页

Test Research, Inc. TR7500 SIII Series User G uide – Soft ware 99 - 相對高度標準:設定相 對高度值。對於晶片元件, 相對高度指的是元件不同區域間 所算出高度的相對差異 ;對積體電路元件,相對 高度指的某一導腳 與 同一 排最低導 腳的高度差異。 - 相對高度上限:設定相 對高度值的公差值上限。 - 相對高度下限:設定相 對高度值的公差值下限。 高度上限 (%) :將…

Test Research, Inc.

98 TR7500 SIII Series User Guide – Software

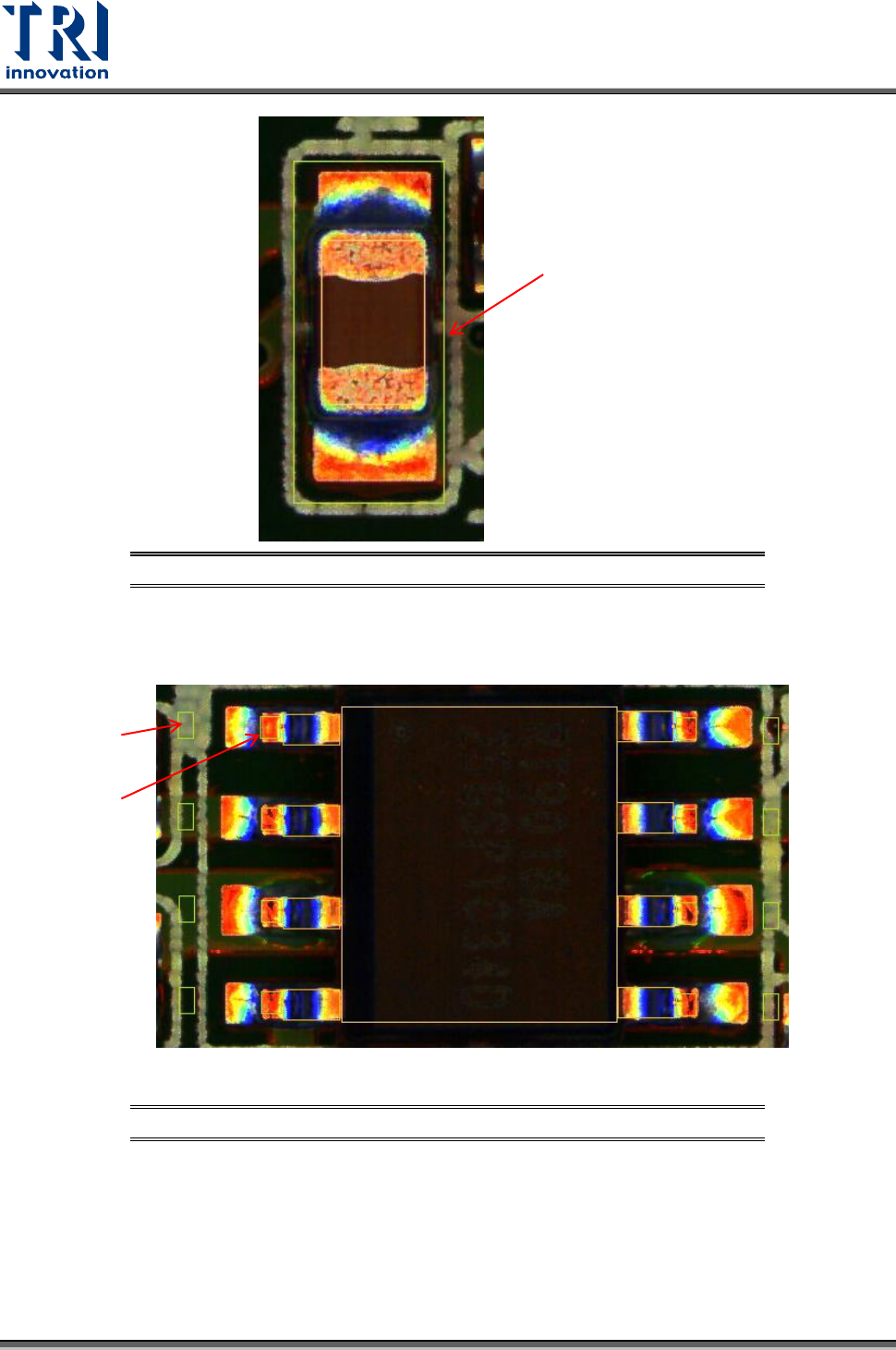

圖 138:Laser3D 框 – Chip 類別檢測框配置示意圖

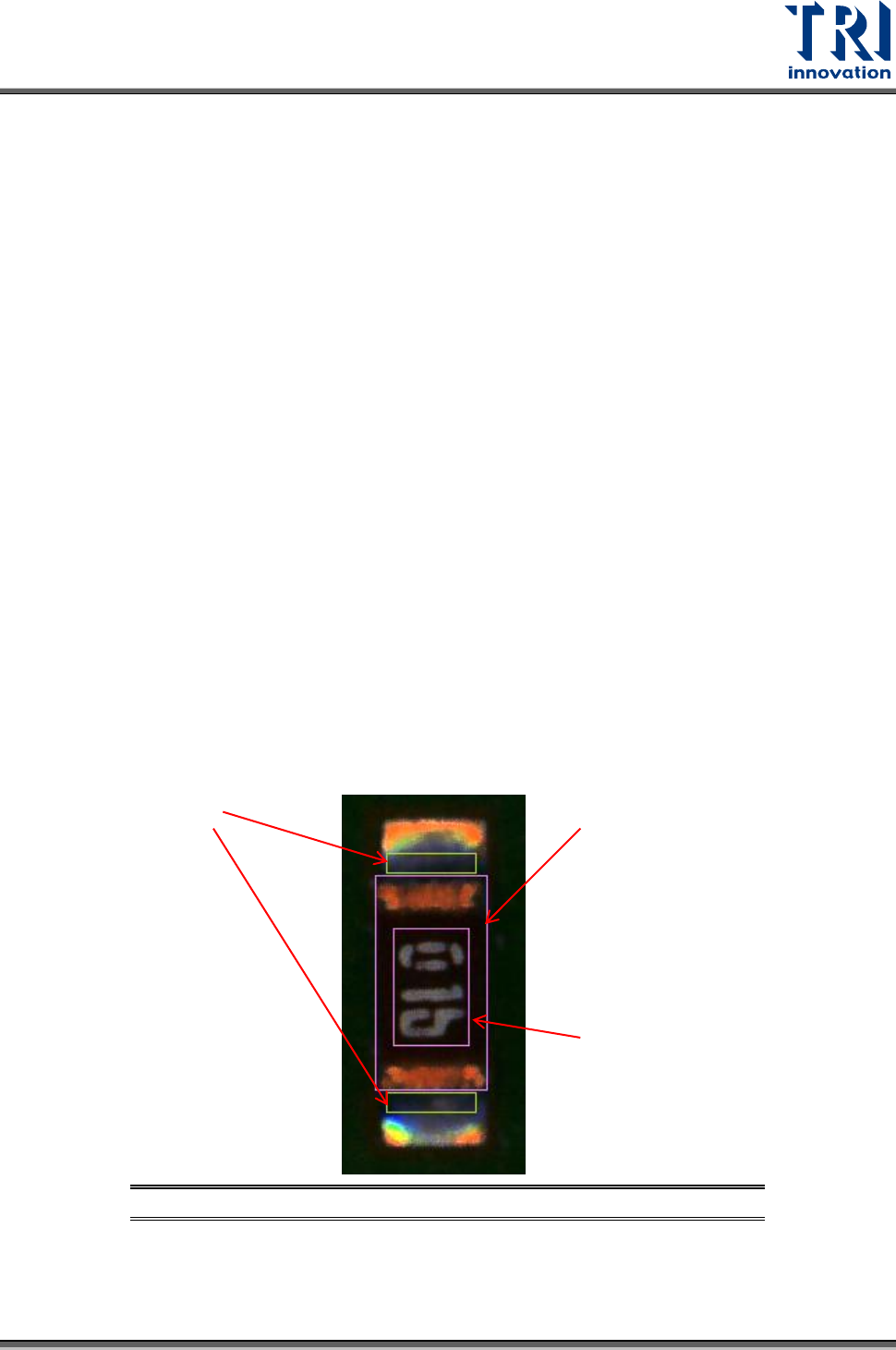

- Lead:僅用於有導腳的元件。檢測框須放置在電路板底板(作為 Base)和導腳尾端位

置(作為 Layer1)。框的位置配置如下圖所示。

圖 139:Laser3D 框 – Lead 類別檢測框配置示意圖

絕對高度:啟動絕對高度的參數檢測。

- 絕對高度標準:設定絕對高度值。絕對高度指的是檢測位置至底板的預期高度。

- 絕對高度上限:設定絕對高度值的公差值上限。

- 絕對高度下限:設定絕對高度值的公差值下限。

相對高度:啟動相對高度的參數檢測。

Layer1

Layer1

Base

Test Research, Inc.

TR7500 SIII Series User Guide – Software 99

- 相對高度標準:設定相對高度值。對於晶片元件,相對高度指的是元件不同區域間

所算出高度的相對差異;對積體電路元件,相對高度指的某一導腳與同一排最低導

腳的高度差異。

- 相對高度上限:設定相對高度值的公差值上限。

- 相對高度下限:設定相對高度值的公差值下限。

高度上限(%):將檢測框內所有位置的高度值畫出常態分佈圖,然後將此值到 100%內

的值濾掉不列入計算。

高度下限(%):將檢測框內所有位置的高度值畫出常態分佈圖,然後將 0 到此值濾掉不

列入計算。

自動學習:自動計算檢測框設定在 1-3 層時的高度。

3.8 常見元件所需的檢測框

在此,我們提供一些常見元件的製作方式,並且說明其檢測框所要檢測的缺陷類別。這些建議

的方式並非唯一的方式,使用者可以依照實際需求來增加或者減少檢測框以達到最佳的檢測品

質。

3.8.1 晶片(Chip)

晶片是一般電路板上最容易看到的元件,其最主要測試的缺陷就是晶片兩端的空焊、缺件和錯

件。因此,一般的情況下,所設定的檢測框如下圖所示。以下範例是電阻晶片,若是電容晶片,

請將中間的 PatMatch 框換成 Void 框(測反件)即可。

*使用者可以依據需求自行增減檢測框。

圖 140:晶片元件所需檢測框說明

演算法:Void 框

用途:檢測空焊

演算法:OCV 框

用途:檢測錯件

演算法:PatMatch、

CorMatch 或 Chip 框

用途:檢測缺件

Test Research, Inc.

100 TR7500 SIII Series User Guide – Software

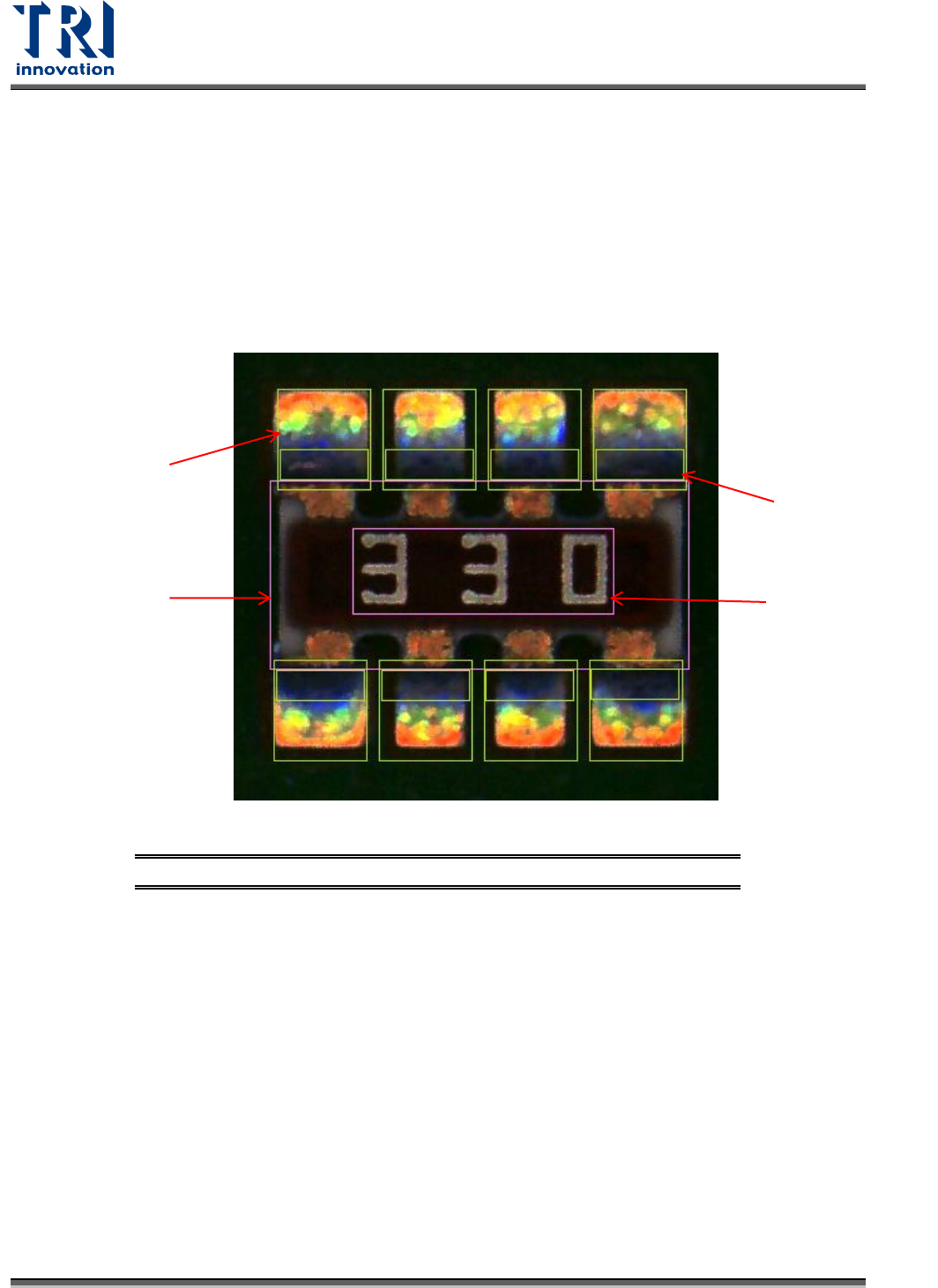

3.8.2 排阻(Array)

排阻也是一般電路板上最容易看到的元件,其最主要測試的缺陷就是缺件、錯件和導腳(Lead)

的空焊與短路(Bridge)。因此,一般的情況下,所設定的檢測框如下圖所示。以下範例是電阻

排阻,若是電容排阻,請將中間的 PatMatch 框換成 Void 框(測反件)即可。

排阻也是一般電路板上最容易看到的元件,其最主要測試的缺陷就是缺件、錯件和導腳(Lead)

的空焊與短路(Bridge)。因此,一般的情況下,所設定的檢測框如下圖所示。以下範例是電阻

排阻,若是電容排阻,請將中間的 PatMatch 框換成 Void 框(測反件)即可。

圖 141:排阻元件所需檢測框說明

演算法:Bridge 框

用途:檢測短路

演算法:PatMatch

或 Chip 框

用途:檢測缺件

演算法:OCV 框

用途:檢測錯件

演算法:Void 框

用途:檢測空焊