Cadence_16.6高速电路板设计与仿真.pdf - 第193页

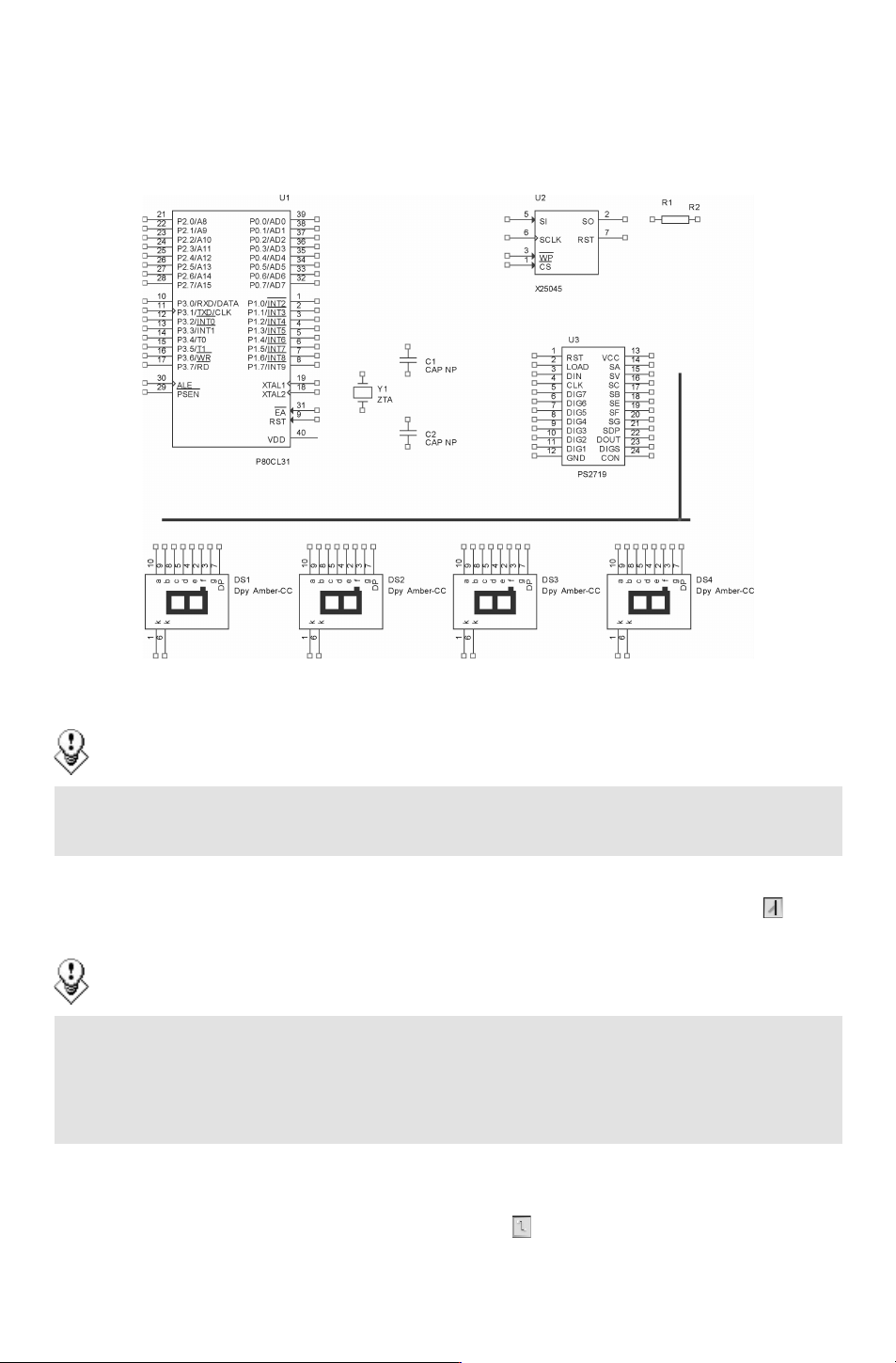

如 图 6 - 2 4 0 所 示 。 图 6 - 2 3 9 放 置 总线 分 支 图 6 - 2 4 0 完 成 布线 9 . 放 置 网络 标 签 选择 菜 单栏 中 的 “ P l a c e ( 放 置) ” → “ N e t A l i a s ( 网络 名 ) ” 命 令, 或 单 击 “ D r a w ( 绘 图) ” 工具 栏中 的 “ P l a c e n e t a l i a s ( 放置 网络 名 ) ”…

作,这时鼠标变成十字形状。单击鼠标确定总线的起点,按住鼠标左键不放,拖动鼠标画出

总线,将

DPY.OLB库中 DpyAmber-CC芯片上的管脚与 PS7219芯片上的引脚连接起来,

如图 6-238所示。

图 6-238 绘制总线

提示:

在绘制总线时,要使总线离芯片针脚有一段距离,这是因为还要放置总线分支,如果

总线放置得过于靠近芯片引脚,则在放置总线分支的时候就会有困难。

2)放置总线分支。选择菜单栏中的 “Place(放置)”

→

“BusEntry(总线分支)” 命

令,或单击 “Draw (绘图)” 工具栏中的 “Placebusentry(放置总线分支)” 按钮 ,用总

线分支将芯片的引脚和总线连接起来,如图 6-239所示。

提示:

在放置总线分支时,总线分支方向有时是不一样的,例如在图 6-171中,左边的总

线分支向右倾斜,而右边的总线分支向左倾斜。在放置时只需要按 〈R〉 键就可以改变总

线分支的朝向,总线分支一端连接总线,另一段不能直接连接元件引脚,需要经过导线

过度。

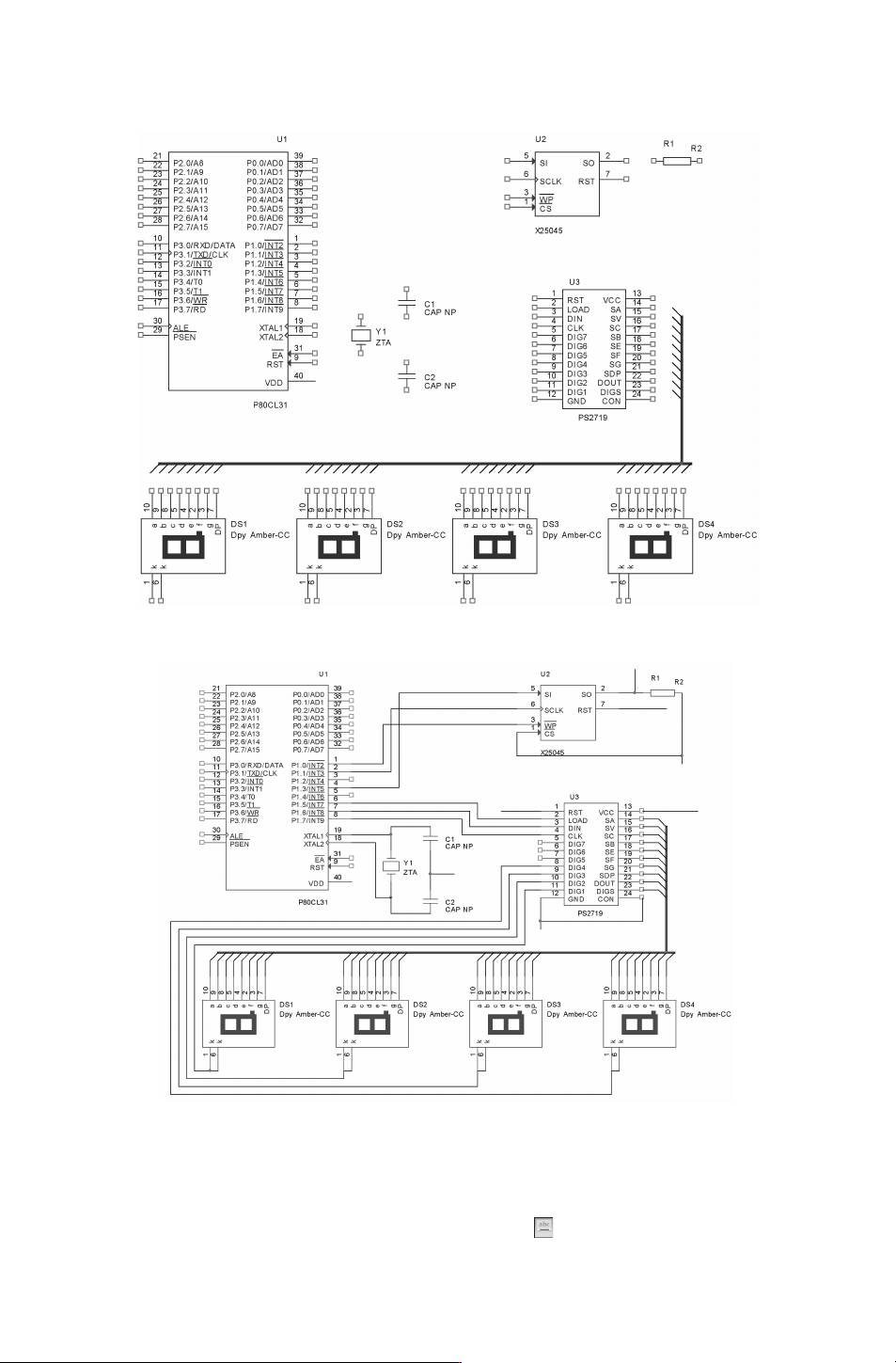

8.绘制导线

选择菜 单 栏 中 的 “Place(放 置)”

→

“Wire(导 线)” 命 令, 或 单 击 “Draw (绘

图)” 工具栏中的 “Placewire(放 置导线)” 按 钮 ,绘制除了 总线之外 的其他导线,

181

如图 6-240所示。

图 6-239 放置总线分支

图 6-240 完成布线

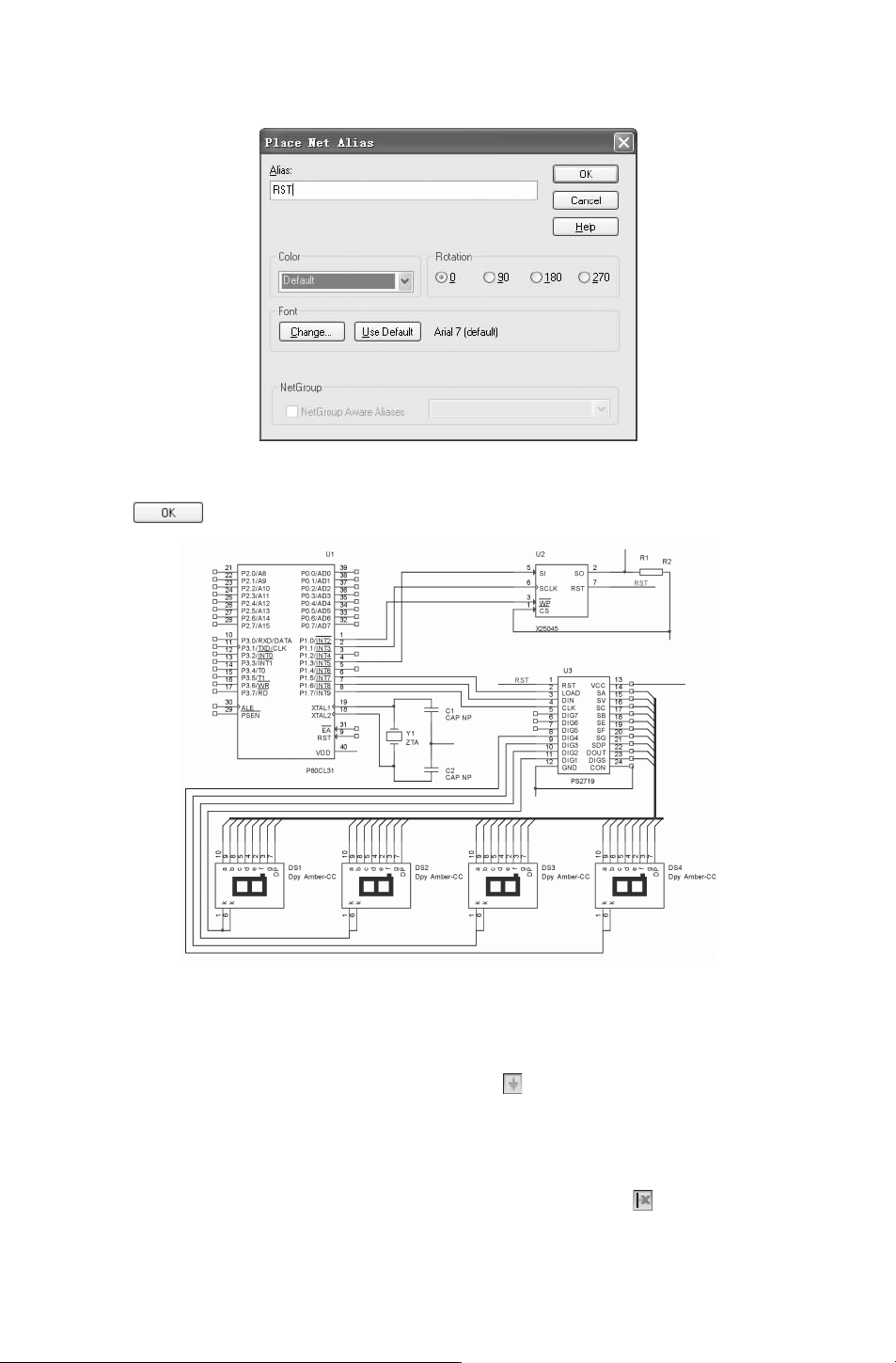

9.放置网络标签

选择菜单栏中的 “Place(放置)”

→

“NetAlias(网络名)” 命令,或单击 “Draw (绘

图)”工具栏中的 “Placenetalias(放置网络名)” 按钮 ,弹出 “PlaceNetAlias(放置网

281

络名)” 对话框,如图 6-241所示。在该对话框中输入标签名称 RST。

图 6-241 编辑网络标签

单击 按钮,将网络标签放置到导线上,结果如图 6-242所示。

图 6-242 完成放置网络标签

10.添加接地、电源符号

选择菜单栏 中 的 “Place(放置)”

→

“Ground (接 地)” 命 令,或 单 击 “Draw (绘

图)”工具栏中的 “Placeground(放置接地)” 按钮 ,在弹出的对话框中选择接地、电源

符号,然后向电路中添加接地、电源符号,如图

6-243所示。

11.放置忽略 ERC检查测试点

选择菜单栏中的 “Place(放置)”

→

“NoConnect(不连接)” 命令,或单击 “Draw

(绘图)”工具栏中的 “Placenoconnect(放置不连接符号)” 按钮 ,放置忽略 ERC检查

测试点,如图 6-244所示。

381