Cadence_16.6高速电路板设计与仿真.pdf - 第208页

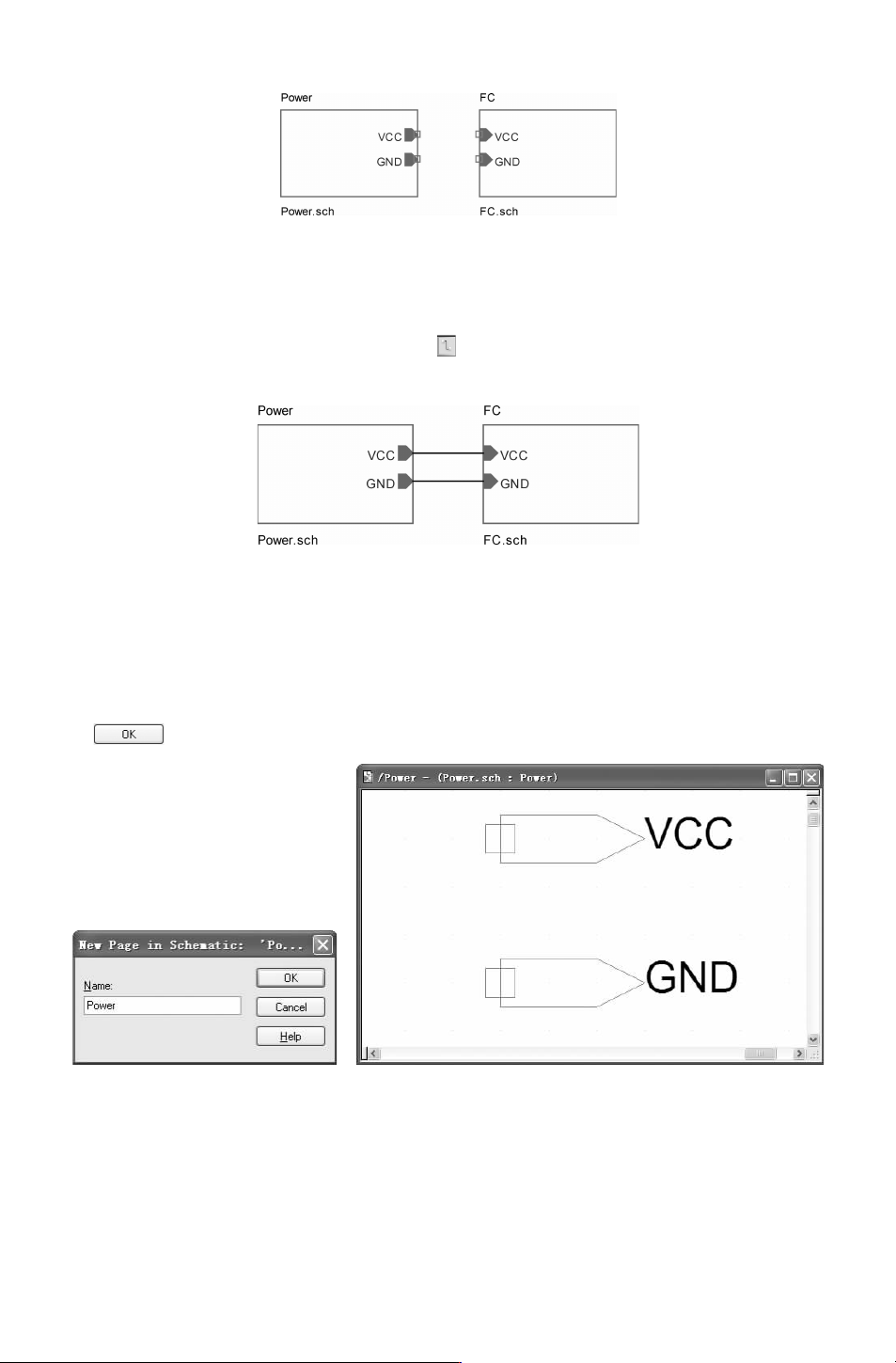

图 6 - 2 7 5 放 置 图样 入 口 3 . 原 理 图设 计 选择 菜 单栏 中 的 “ P l a c e ( 放 置 ) ” → “ W i r e ( 导 线 ) ” 命 令 , 或 单 击 “ D r a w ( 绘 图 ) ” 工具 栏 中的 “ P l a c e w i r e ( 放 置 导 线 ) ” 按 钮 , 对 原 理 图 进 行 布 线 操 作 , 结 果 如 图 6 - 2 7 6 所示 。 图 6…

图 6-275 放置图样入口

3.原理图设计

选择菜单栏中的 “Place(放置)”

→

“Wire(导线)” 命令,或单击 “Draw (绘图)”

工具栏中的 “Placewire(放置导线)” 按钮 ,对原理图进行布线操作,结果如图 6-276

所示。

图 6-276 绘制结果

4.生成子原理图

1)选中 “Power”层次块,右击鼠标,选择 “DescendHierarchy(生成下层电路层)”

命令,弹出如图 6-277所示的对话框,系统会自动创建一个电路原理图文件夹,弹出的对

话框中可以修改创建电路原理图文件夹的名称,在 “

Name(名称)” 栏中输入 “Power”,

单击 按钮,创建层次块 “Power”对应的下层电路,如图 6-278所示。

图 6-277 修改下层电路图名称 图 6-278 Logic层次块对应的下层电路

2)用同样的方法创建层次块 “FC” 对应的子原理图,如图 6-279所示。

3)与此同时,在项目管理器中产生了新的电路图 Power.sch:Power和 FC.sch:FC,如

图 6-280所示。

691

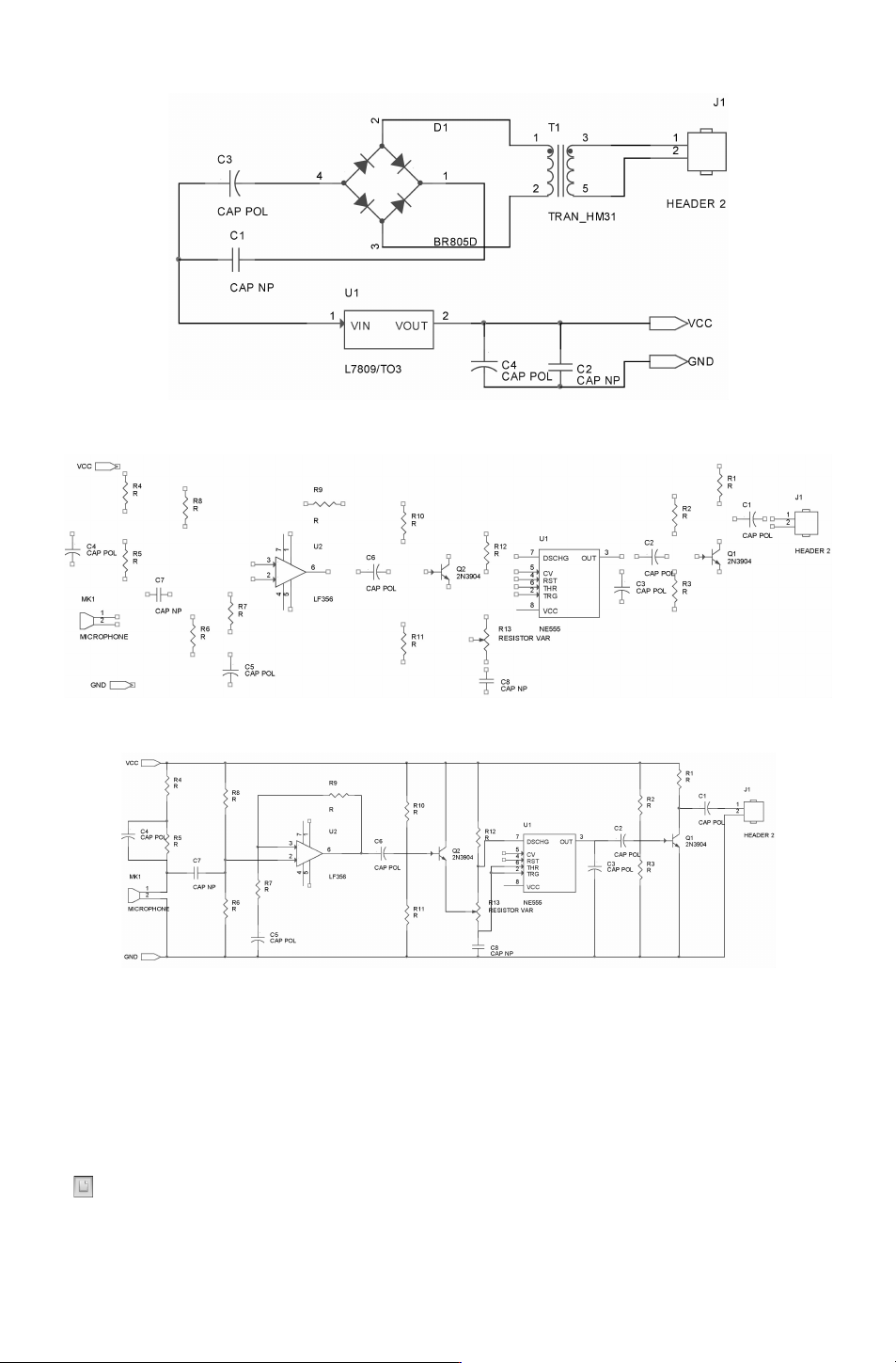

图 6-282 连接电路图

图 6-283 在新建图页 FC上摆放元件

图 6-284 完成图页 “FC” 绘制

6.4.7 扫描特性电路

1.建立工作环境

1)在 Cadence主窗口中,选择菜单栏中的 “Files(文件)”

→

“New” (新 建)

→

“Project(工程)” 命令,或单击 “Capture”工具栏中的 “Createdocument(新建文件)” 按

钮 ,弹出如图 6-285所示 的 “New Project(新 建工程)” 对话框,选择原理 图类型为

“AnalogorMixedA/D”,输入文件名称为 “ScanningProperties”。

891