Cadence_16.6高速电路板设计与仿真.pdf - 第75页

靠相 同 名称 的 页间 连 接符 进 行电 气 连接 。 如果 图 样够 大 ,平 坦 式电 路 也可 以 绘制 在 同一 张 电 路图 上 ,但 电 路图 结 构过 于 复杂 , 不易 理 解, 在 绘制 过 程中 也 容易 出 错。 采 用平 坦 式电 路 虽 然电 路 图不 在 一张 图 页上 , 但相 当 于在 同 一个 电 路图 的 文件 夹 中。 F l a t D e s i g n 即平坦 式 设计 , 在电 路 规模…

文件夹中。

●

“CopyAllReferredFilesPresentOutofProjectFolder”:将所有相关文件保存在工程文

件夹外。

单击 按钮,完成保存设置。

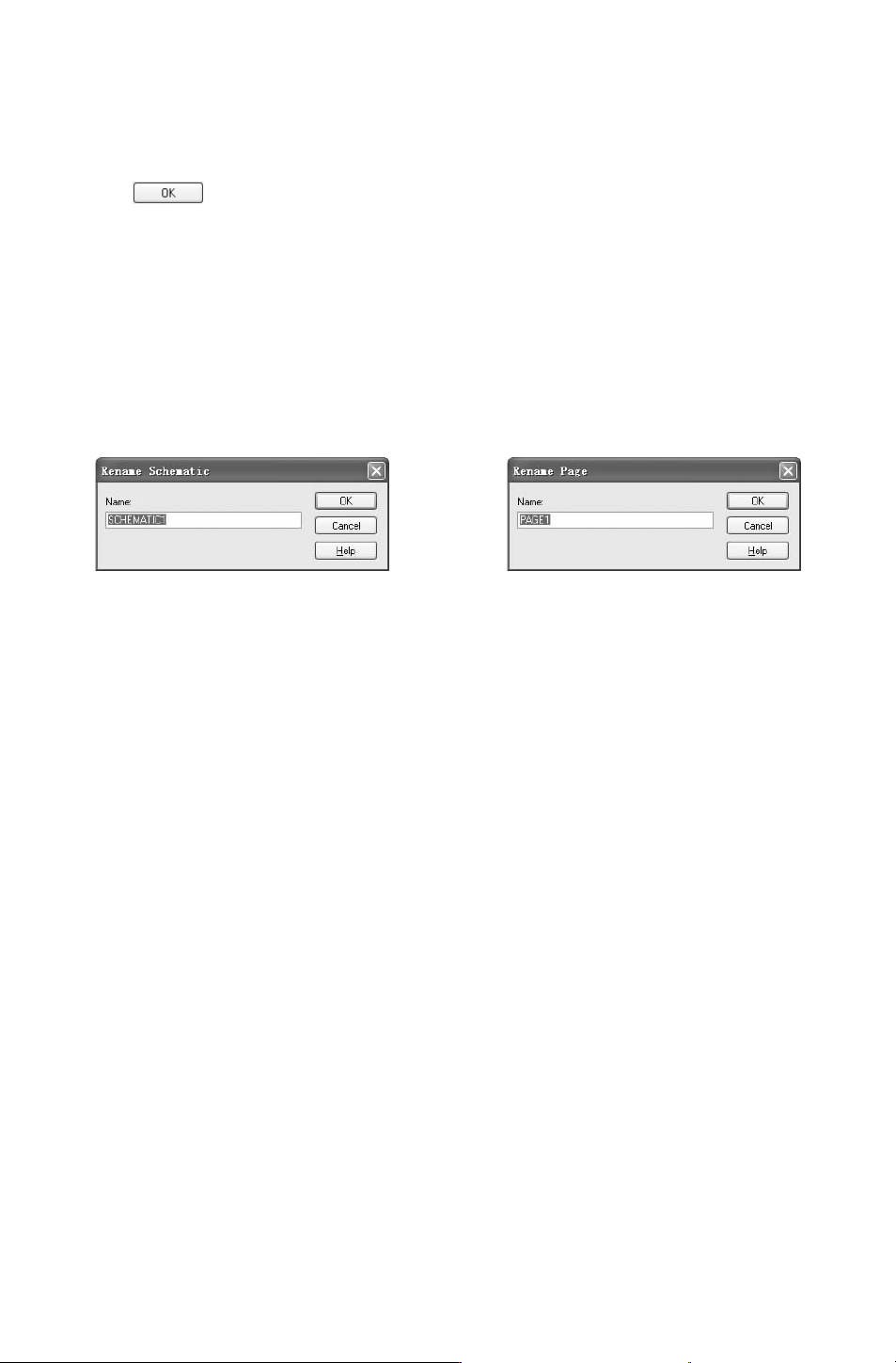

4.原理图文件重命名

在工程管理器中选择要重命名的原理图文件,选择菜单栏中的 “Design(设计)”

→

“Rename(重命名)” 命令,或单击右键选择 “Rename(重命名)” 命令,弹出 “Rename

Schematic(原理图重命名)” 对话框,如图 3-6所示,输入新原理图文件的名称。

5.原理图页重命名

在工程管理 器中选择 要重命名 的图页文件,选 择 菜 单 栏 中 的 “Design(设 计)”

→

“Rename(重命名)” 命令,或单击右键选择 “Rename(重命名)” 命令,弹出 “Rename

Page(图页重命名)”对话框,如图 3-7所示,输入新图页名称。

图 3-6 “RenameSchematic(原理图重命名)”

对话框

图 3-7 “RenamePage(图页重命名)”

对话框

注意,不论原理图是否打开,重命名操作都会立即生效。

6.其他文件重命名

工程文件 .opj只能用另存文件的方式进行重命名,设计文件 .dsn同样适用另存为的方

式重命名文件,这样才能和工程文件保持联系,否则工程文件就找不到数据库了。

3.3 原理图分类

在进行电路原理图设计时,鉴于某些图样过于复杂,无法在一张图样上完成,于是衍生

出两种电路设计方法 (平坦式电路、层次式电路) 来解决这种问题。

原理图设计分类如下:

●

进行简单的电路原理图设计 (只有单张图样构成的)。

●

平坦式电路原理图设计 (由多张图样拼接而成的)。

●

层次式电路原理图设计 (多张图样按一定层次关系构成的)。

平坦式电路中各图页间是左右关系、层次式电路各图页间是上下关系。

按照功能分,原理图又可分为一般电路与仿真电路。

3.3.1 平坦式电路

平坦式电路是相互平行的电路,在空间结构上是在同一个层次上的电路,只是分布在不

同的电路图样上,每张图样通过页间连接符连接起来。

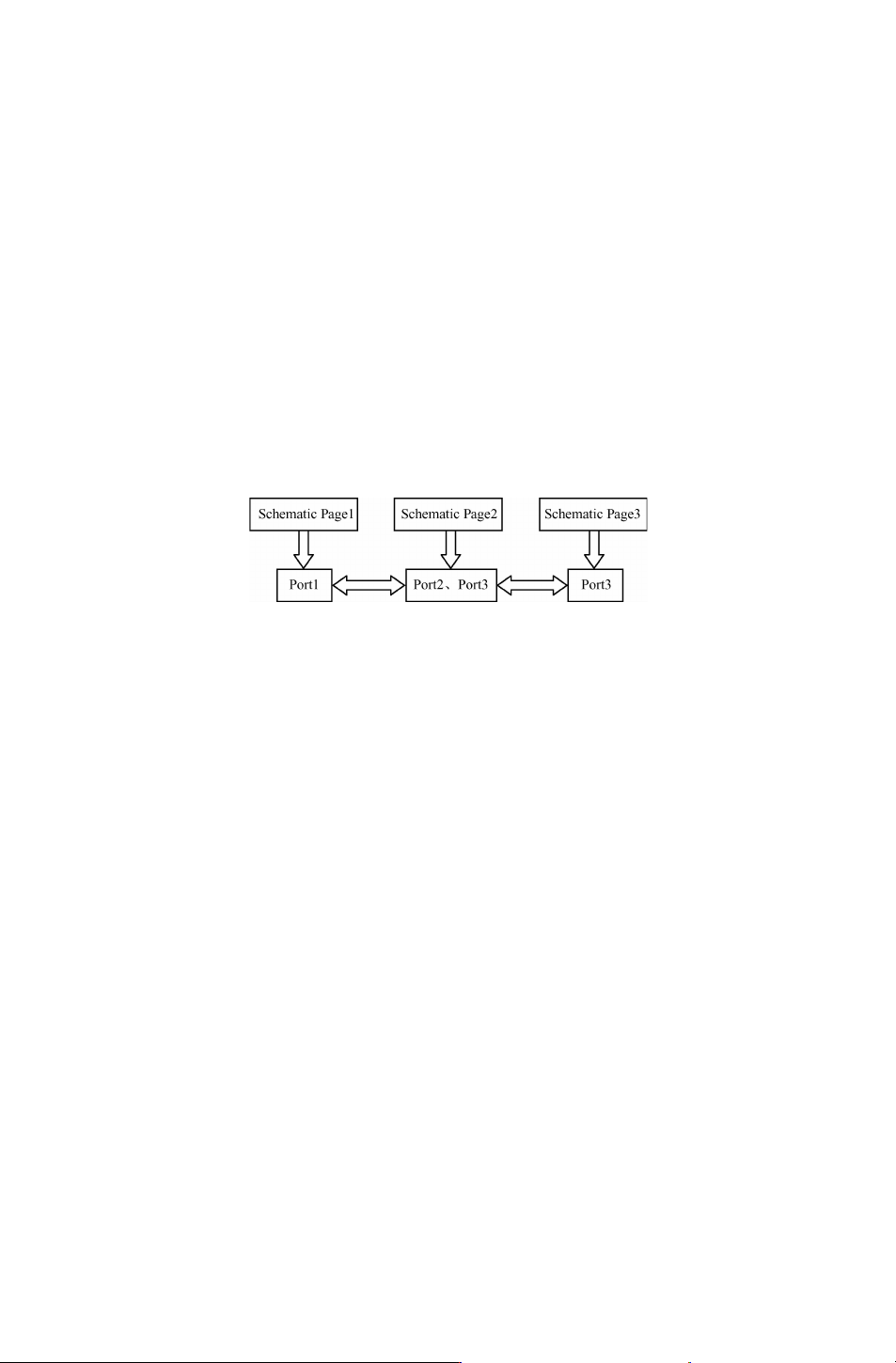

平坦式电路表示不同图页间的电路连接,每张图页上均有页间连接符显示,不同图页依

36

靠相同名称的页间连接符进行电气连接。如果图样够大,平坦式电路也可以绘制在同一张电

路图上,但电路图结构过于复杂,不易理解,在绘制过程中也容易出错。采用平坦式电路虽

然电路图不在一张图页上,但相当于在同一个电路图的文件夹中。

FlatDesign即平坦式设计,在电路规模较大时,将图样按功能分成几部分,每部分绘制

在一页图样上,每张电路图之间的信号连接关系用 “Off-PageConnector(页间连接符)”

表示。

Capture中平坦式电路结构的特点如下:

1.每页电路图上都有 “Off-PageConnector(页间连接器)”,表示不同页面电路间的连

接。不同电路上相同名称的 “Off-PageConnector(页间连接器)” 在电学上是相连的。

2.平坦式电路之间不同页面都属于同一层次,相当于在 1个电路图文件夹中。如图 3-8

所示,3张电路图都位于 1个文件夹下。

平坦式电路从空间结构上看是在同一个层次上的电路,只是整个电路在不同的电路图样

上,每张电路图之间是通过端口连接器连接起来的。

图 3-8 平坦式电路图结构

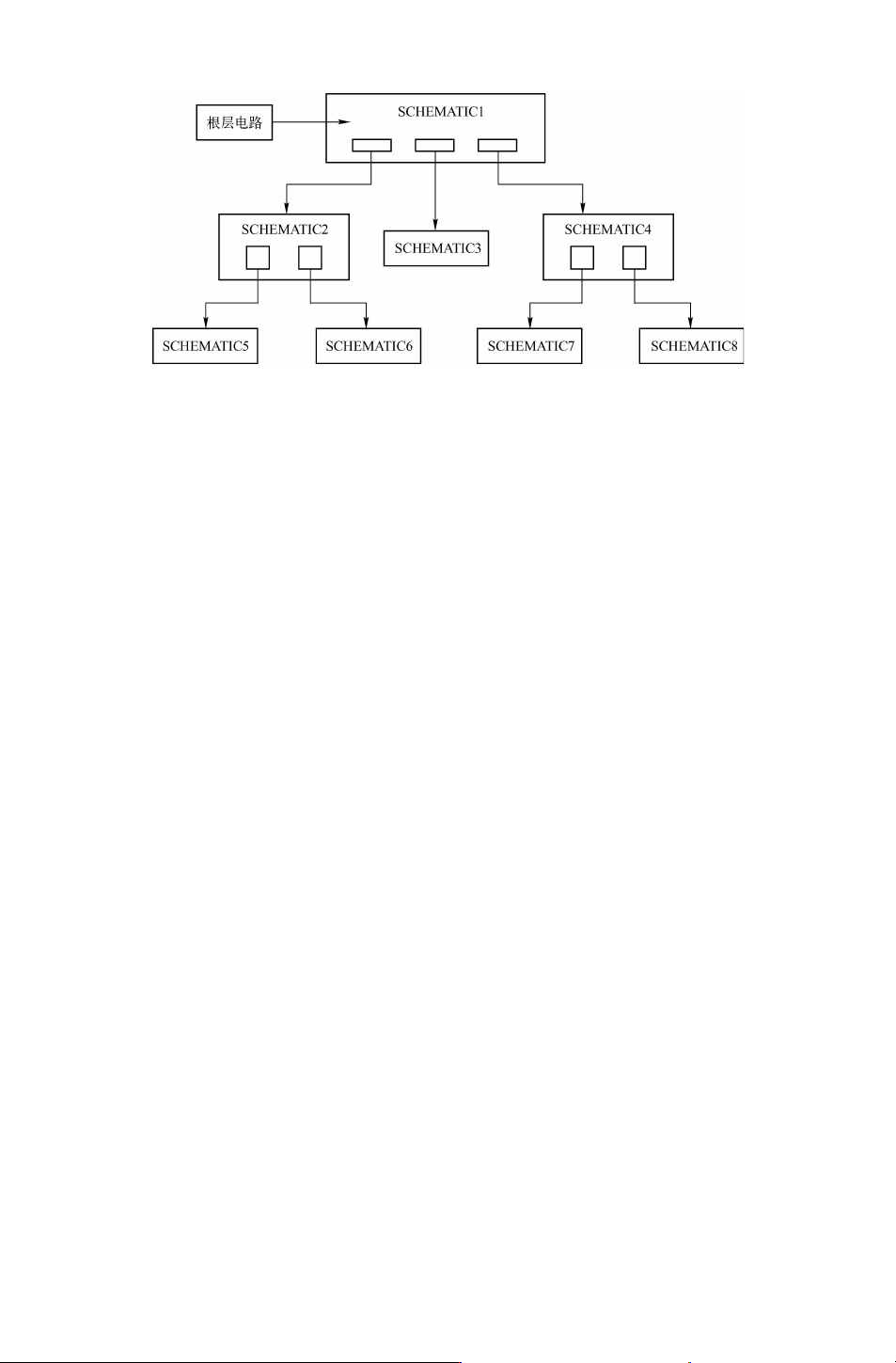

3.3.2 层次电路

层次电路是在空间结构上属于不同层次的,一般是先在一张图样上用框图的形式设置顶

层电路,在另外的图样上设计每个框图所代表的子原理图。

如果电路规模过大,采用幅面最大的页面图样也容纳不下整个电路设计,就必须采用平

坦式或层次式电路结构。但在以下几种情况下,即使电路的规模不是很大,完全可以放置在

一页图样上,也往往采用平坦式或层次式电路结构。

1)将一个复杂的电路设计分为几个部分,分配给几个工程技术人员同时进行设计。

2)按功能将电路设计分成几个部分,让具有不同特长的设计人员负责不同部分的

设计。

3)采用的打印输出设备不支持幅面过大的电路图页面打印。

4)目前自上而下的设计策略已成为电路和系统设计的主流,这种设计策略与层次式电

路结构一致,因此对于相对复杂的电路和系统设计,大多采用层次式结构,使用平坦式电路

结构的情况已相对减少。

对于层次式电路结构,首先在一张图样上用框图的形式设计总体结构,然后在另外一张

图样上设计每个子电路框图代表的结构。在实际设计中,下一层次电路还可以包含有子电路

框图,按层次关系将子电路框图逐级细分,直到最后一层完全为某一个子电路的具体电路

图,不再含有子电路框图。

层次式电路图的基本结构如图

3-9所示。

46

图 3-9 层次式电路结构图

在图 3-9中,每个区域就是已给电路图系 (标志为 Schematic而不是 Page),每个区域

相当于一个数据夹,其中可以只放一张电路图,也可以是几张电路图所拼接而成的平坦式电

路图。

3.3.3 仿真电路

与普通原理图相比,仿真原理图有以下几点要求:

1)调用的器件必须有 PSpice模型,软件本身提供的模型库,库文件存储的路径为 “X:

Capture\Library\pspice”,所有器件都提供 PSpice模型,可以直接调用。

2)使用自行创建的器件,必须保证 “

*

.olb”、 “

*

.lib” 两个文件同时存在,而且器

件属性中必须包含 PSpiceTemplate属性。

3)原理图中至少必须有一条网络名称为 0,即接地。

4)必须有激励源,原理图中的端口符号并不具有电源特性,所有的激励源都存储在

Source和 SourceTM库中。

5)电源两端不允许短路,不允许仅由电源和电感组成回路,也不允许仅由电源和电容

组成的割集。在简单回路中可用电容并联一个大电阻或电感串联一个小电阻。

6)最好不要使用负值电阻、电容和电感,因为它们容易引起电路不收敛。

3.4 创建原理图

不同的原理图类型采用不同的创建方法,下面简单介绍原理图的不同创建方法。

3.4.1 创建平坦式电路

Capture的 Project是用来管理相关文件及属性的。新建 Project的同时,Capture会自动创

建相关的文件,如 DSN、OPJ文件等,根据创建的 Project类型的不同,生成的文件也不尽

相同。

1.新建工程文件

选择菜单栏中的 “File(文件)”

→

“New (新建)” 命令或单击 “Capture”工具栏中

56