Cadence_16.6高速电路板设计与仿真.pdf - 第80页

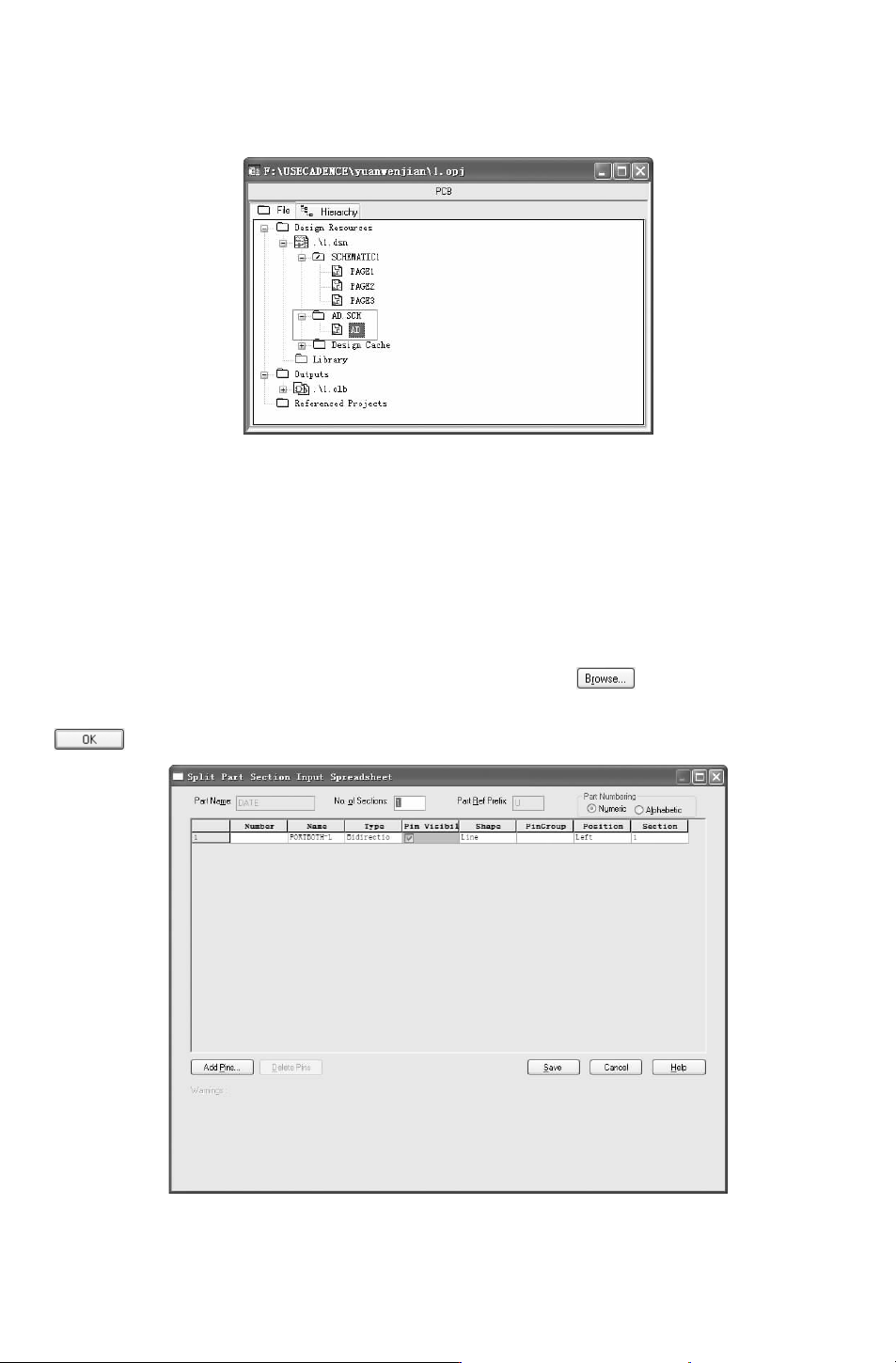

3 ) 同时 ,在 项 目管 理 器中 自 动创 建 一 个 新 的 原 理 图 文 件 夹 A D . S C H , 在 该 文 件 夹 下 显 示创 建 的子 原 理图 A D ,如 图 3 - 2 3 所示 。 图 3 - 2 3 项 目管 理 器窗 口 按照 一 般绘 图 子原 理 图的 方 法, 使 用同 样 的方 法 绘制 其 余模 块 。这 样 ,就 完 成了 自 上而 下绘 制 层次 电 路的 设 计。 2 . 生 成…

3)同时,在项目管理器中自动创建一个新的原理图文件夹 AD.SCH,在该文件夹下显

示创建的子原理图

AD,如图 3-23所示。

图 3-23 项目管理器窗口

按照一般绘图子原理图的方法,使用同样的方法绘制其余模块。这样,就完成了自上而

下绘制层次电路的设计。

2.生成图表符元件

1)首先绘制完成需要转换模块的子原理图,打开项目管理器窗口,选择菜单栏中的

“Tools(工具)”

→

“GeneratePart(生成图表符元件)” 命令,弹出 “GeneratePart(生成

图表符元件)” 对话框,设置要生成的层次块元件参数。

2)单击 “Netlistsourcefiles(资源文件)” 选项右侧的 按钮,选择当前项目文

件,在 “PartName(元 件名 称)” 文 本 框 输 入 层 次块 名 称,其 余 选项 选 择 默 认,单 击

按钮,弹出如图 3-24所示的对话框,设置层次块元件的引脚信息。

图 3-24 “SplitPartSectionInputSpreadsheet”对话框

07