IPC-CM-770D-1996 - 第53页

January 1996 IPC-CM-770 The use of leaded chip carriers generally has the following carriers have a chamfered index comer that is larger than disadvantages when compared to the use of leadless chip that of type C. Anothe…

IPC-CM-770

Januaty

1996

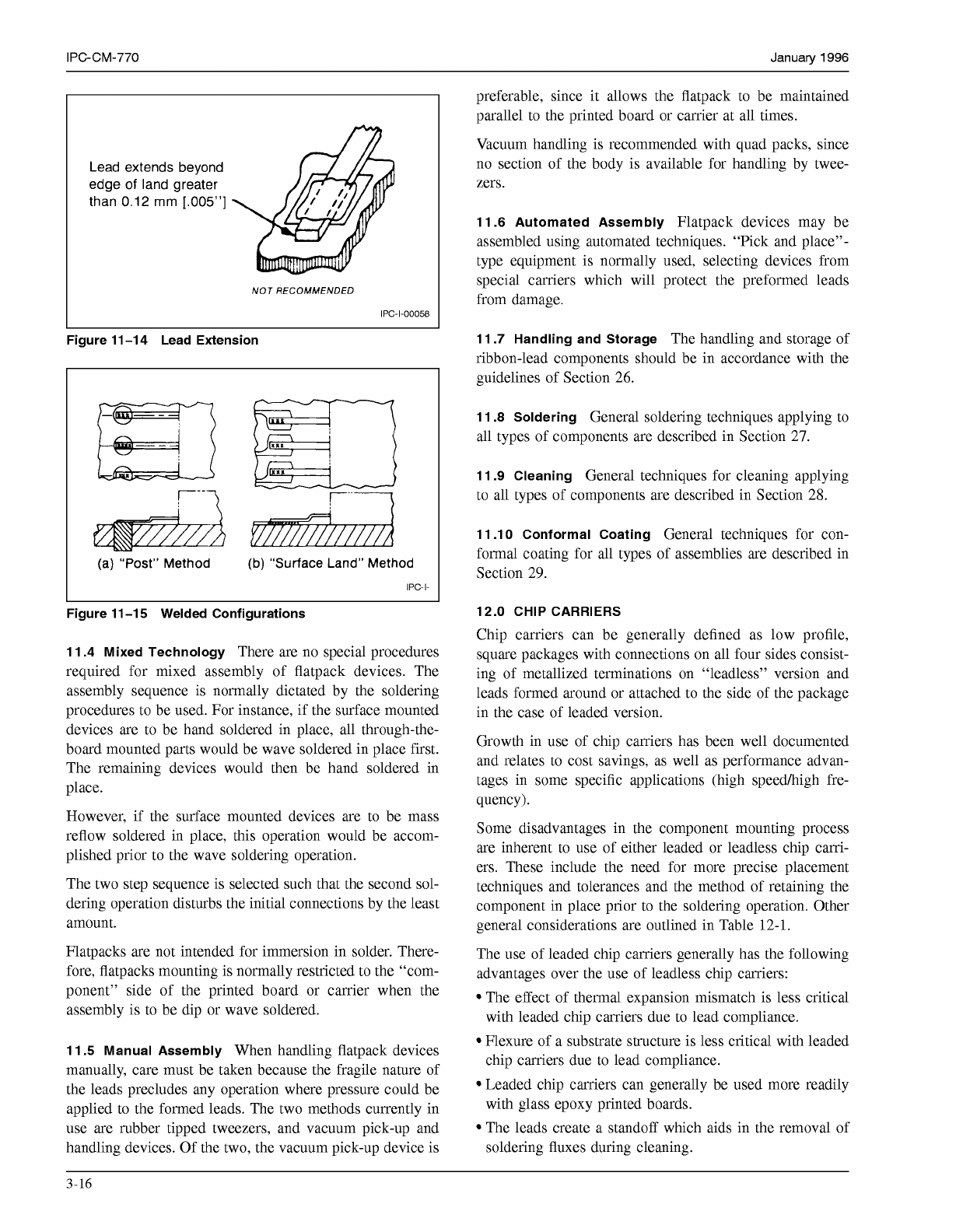

Lead extends beyond

edge

of

land greater

than

0.12

mm

[.005”]

NOT

RECOMMENDED

IPC-I-O0058

Figure 11 -1 4 Lead Extension

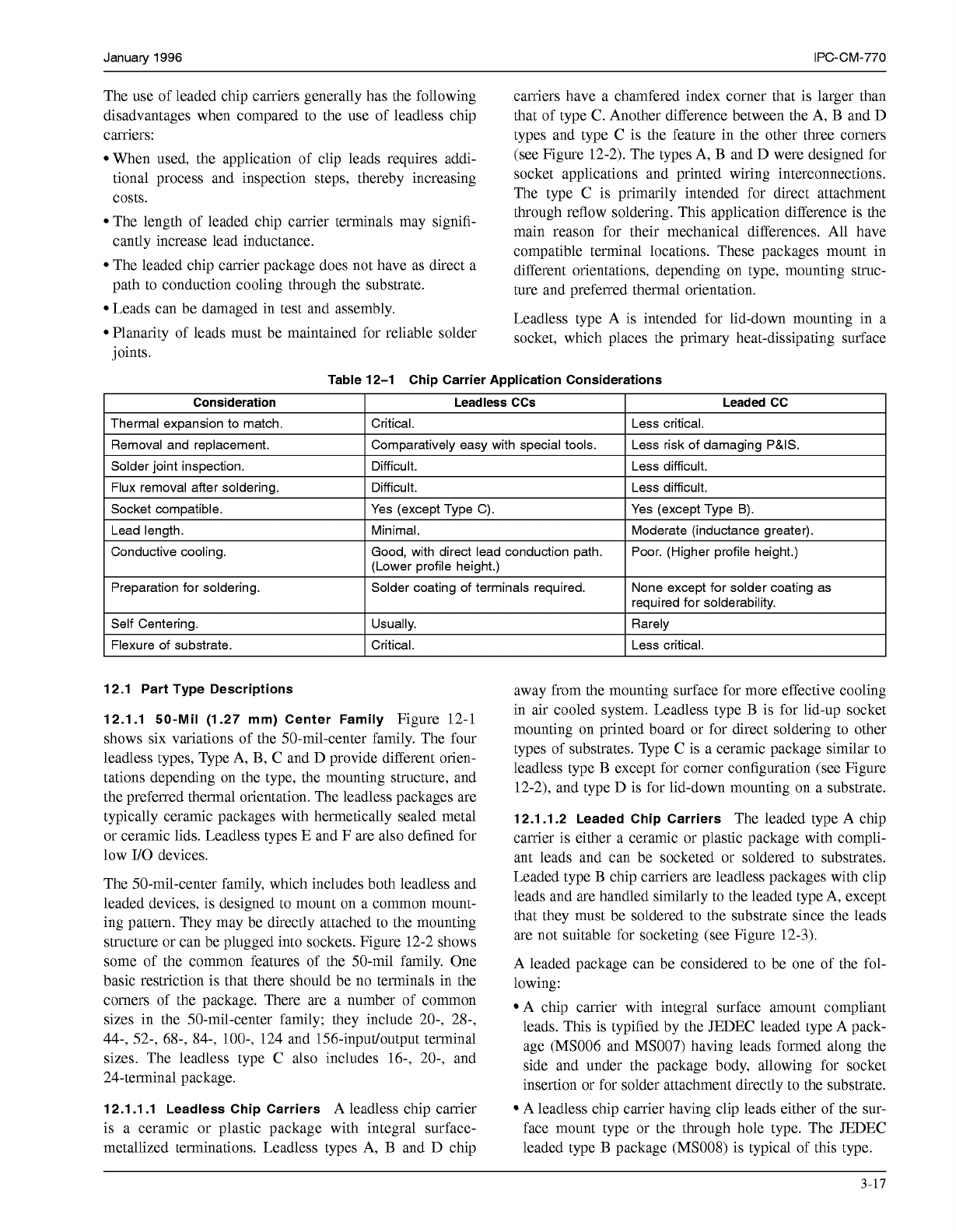

(a)

“Post”

Method

(b)

“Surface Land” Method

IPC-I-

Figure 11-15 Welded Configurations

1 1.4 Mixed Technology

There are no special procedures

required for mixed assembly of flatpack devices. The

assembly sequence is normally dictated by the soldering

procedures to be used. For instance, if the surface mounted

devices are to be hand soldered in place, all through-the-

board mounted parts would be wave soldered in place first.

The remaining devices would then be hand soldered in

place.

However, if the surface mounted devices are to be mass

reflow soldered in place, this operation would be accom-

plished prior to the wave soldering operation.

The two step sequence is selected such that the second sol-

dering operation disturbs the initial connections by the least

amount.

Flatpacks are not intended for immersion in solder. There-

fore, flatpacks mounting is normally restricted to the “com-

ponent” side of the printed board or carrier when the

assembly is to be dip or wave soldered.

11.5 Manual Assembly

When handling flatpack devices

manually, care must be taken because the fragile nature of

the leads precludes any operation where pressure could be

applied to the formed leads. The two methods currently in

use are rubber tipped tweezers, and vacuum pick-up and

handling devices. Of the two, the vacuum pick-up device is

preferable, since it allows the flatpack to be maintained

parallel to the printed board or carrier at all times.

Vacuum handling is recommended with quad packs, since

no section of the body is available for handling by twee-

zers.

11.6 Automated Assembly

Flatpack devices may be

assembled using automated techniques. “Pick and place”-

type equipment is normally used, selecting devices from

special carriers which will protect the preformed leads

from damage.

11.7 Handling and Storage

The handling and storage of

ribbon-lead components should be in accordance with the

guidelines of Section

26.

11.8 Soldering

General soldering techniques applying to

all types of components are described in Section

27.

11.9 Cleaning

General techniques for cleaning applying

to all types of components are described in Section

28.

11.1

O

Conformal Coating

General techniques for con-

formal coating for all types of assemblies are described in

Section

29.

12.0 CHIP CARRIERS

Chip carriers can be generally defined as low profile,

square packages with connections on all four sides consist-

ing of metallized terminations on “leadless” version and

leads formed around or attached to the side of the package

in the case of leaded version.

Growth in use of chip carriers has been well documented

and relates to cost savings, as well as performance advan-

tages in some specific applications (high speedhigh fre-

quency).

Some disadvantages in the component mounting process

are inherent to use of either leaded or leadless chip carri-

ers. These include the need for more precise placement

techniques and tolerances and the method of retaining the

component in place prior to the soldering operation. Other

general considerations are outlined in Table

12-1.

The use of leaded chip carriers generally has the following

advantages over the use of leadless chip carriers:

The effect of thermal expansion mismatch is less critical

with leaded chip carriers due to lead compliance.

Flexure of a substrate structure is less critical with leaded

chip carriers due to lead compliance.

Leaded chip carriers can generally be used more readily

with glass epoxy printed boards.

The leads create a standoff which aids in the removal of

soldering fluxes during cleaning.

3-16

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

January

1996

IPC-CM-770

The use of leaded chip carriers generally has the following carriers have a chamfered index comer that is larger than

disadvantages when compared to the use of leadless chip that of type C. Another difference between the A,

B

and D

carriers: types and type C is the feature in the other three comers

When used, the application of clip leads requires addi-

(see Figure 12-21. The types A,

B

and D were designed for

tional

process

and inspection steps, thereby increasing socket applications and printed wiring interconnections.

through reflow soldering. This application difference is the

main reason for their mechanical differences. All have

compatible terminal locations. These packages mount in

costs. The type C is primarily intended for direct attachment

The length of leaded chip carrier terminals may signifi-

cantly increase lead inductance.

The leaded chip MtTier package does not have as direct a different orientations, depending on type, mounting

strut-

path to conduction cooling through the substrate. ture and preferred thermal orientation.

Leads can be damaged in test and assembly.

Leadless type A is intended for lid-down mounting in a

Planarity of leads must be maintained for reliable solder socket, which places the primary heat-dissipating

surface

joints.

Table 12-1 Chip Carrier Application Considerations

Consideration Leaded CC Leadless CCs

Thermal expansion to match.

I

Critical.

I

Less critical.

I

Removal and replacement.

I

Comparatively easy with special tools.

I

Less risk of damaging P&IS.

I

I

Solder joint inspection.

I

Difficult.

I

Less difficult.

I

I

Flux removal after soldering.

I

Difficult.

I

Less difficult.

I

Socket compatible.

Poor. (Higher profile height.)

Good, with direct lead conduction path. Conductive cooling.

Moderate (inductance greater).

Minimal. Lead length.

Yes (except Type

B).

Yes (except Type C).

Preparation for soldering. Solder coating of terminals required. None except for solder coating as

Self Centering.

Usually. Rarely

(Lower profile height.)

required for solderability.

I

Flexure of substrate.

I

Critical.

I

Less critical.

I

12.1 Part Type Descriptions

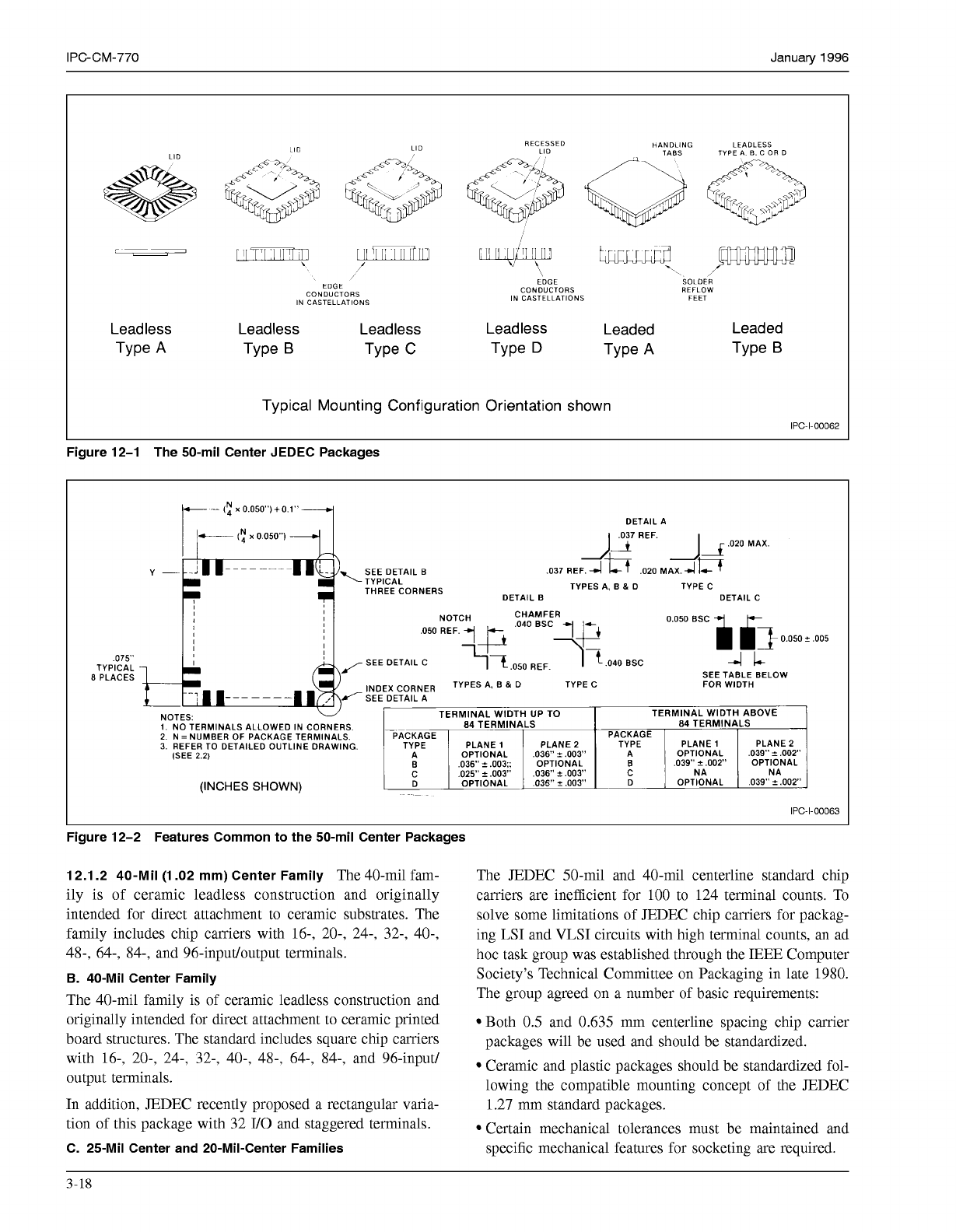

12.1.1 50-Mil (1.27 mm) Center Family

Figure 12-1

shows six variations of the 50-mil-center family. The four

leadless types, Type A,

B,

C and D provide different orien-

tations depending on the type, the mounting structure, and

the preferred thermal orientation. The leadless packages are

typically ceramic packages with hermetically sealed metal

or ceramic lids. Leadless types E and

F

are also defined for

low

I/O

devices.

The 50-mil-center family, which includes both leadless and

leaded devices, is designed to mount on a common mount-

ing pattern. They may be directly attached to the mounting

structure or can be plugged into sockets. Figure 12-2 shows

some of the common features of the 50-mil family. One

basic restriction is that there should be no terminals in the

comers of the package. There are a number of common

sizes in the 50-mil-center family; they include 20-, 28-,

44-, 52-, 68-, 84-,

loo-,

124 and 156-inpudoutput terminal

sizes. The leadless type C also includes 16-, 20-, and

24-terminal package.

12.1.1.1 Leadless Chip Carriers

A leadless chip carrier

is a ceramic or plastic package with integral surface-

metallized terminations. Leadless types A,

B

and D chip

away from the mounting surface for more effective cooling

in air cooled system. Leadless type

B

is for lid-up socket

mounting on printed board or for direct soldering to other

types of substrates. Type C is a ceramic package similar to

leadless type

B

except for comer configuration (see Figure

12-2), and type D is for lid-down mounting on a substrate.

12.1.1.2 Leaded Chip Carriers

The leaded type A chip

carrier is either a ceramic or plastic package with compli-

ant leads and can be socketed or soldered to substrates.

Leaded type

B

chip carriers are leadless packages with clip

leads and are handled similarly to the leaded type A, except

that they must be soldered to the substrate since the leads

are not suitable for socketing (see Figure 12-3).

A leaded package can be considered to be one of the fol-

lowing:

A chip carrier with integral surface amount compliant

leads. This is typified by the JEDEC leaded type A pack-

age (MS006 and

MS007)

having leads formed along the

side and under the package body, allowing for socket

insertion or for solder attachment directly to the substrate.

A leadless chip carrier having clip leads either of the sur-

face mount type or the through hole type. The JEDEC

leaded type

B

package

(MS008)

is typical of this type.

3-17

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

IPC-CM-770

Januaty

1996

LIU

LID

RECESSED

HANDLING

LIU

TABS

TYPE A B.

C

OR

O

LEAOLESS

Leadless Leadless Leadless Leadless Leaded Leaded

Type

A

Type

B

Type

c

Type

D

Type

A

Type

B

Typical Mounting Configuration Orientation shown

IPC-I-O0062

Figure 12-1 The 50-mil Center JEDEC Packages

"

(y

x

0.050')

+

0.1"

DETAIL A

AT

REF.

JA

,020

MAX

SEE DETAIL B

.O37

REF.

4

b

,020

MAX.

4

m

THREE CORNERS

TYPICAL

TYPES A, B

&

D

TYPE

C

DETAIL B

DETAIL C

Ik,

NOTCH

CHAMFER

,050

REF.

yF+

TYPICAL

.075"

8

PLACES

J

SEE

c

llT.050

REF.

,040

ESC

AL

INDEX CORNER

TYPES

B

'

D

SEE TABLE BELOW

TYPE C

FOR

WIDTH

-7

I

-------

,I

J

SEE DETAIL A

NOTES:

PLANE

2

PLANE

1

TYPE

PLANE

2

PLANE

1

TYPE

3.

REFER TO DETAILED OUTLINE DRAWING.

PACKAGE

2.

N

=

NUMBER OF PACKAGE TERMINALS.

84 TERMINALS

1.

NO TERMINALS ALLOWED IN CORNERS.

TERMINAL WIDTH

UP

TO

TERMINAL WIDTH ABOVE

84 TERMINALS

PACKAGE

(SEE

2.2)

A

C

B

.039"?

,002"

OPTIONAL

OPTIONAL

,036"

f

,003;;

B

A

,036"

f

,003''

OPTIONAL

,039''

f.002"

OPTIONAL

D

NA

NA

.035"

,003"

OPTIONAL

D

C

,036'

?

.003"

,025"

f

.003"

OPTIONAL

,039'

?.002"

(INCHES SHOWN)

~~~ ~

IPC-I-O0063

Figure 12-2 Features Common to the 50-mil Center Packages

12.1.2 40-Mil (1 .O2 mm) Center Family

The 40-mil fam-

ily is of ceramic leadless construction and originally

intended for direct attachment to ceramic substrates. The

family includes chip carriers with 16-, 20-, 24-, 32-, 40-,

48-, 64-, 84-, and 96-inpudoutput terminals.

B.

40-Mil Center Family

The 40-mil family is of ceramic leadless construction and

originally intended for direct attachment to ceramic printed

board structures. The standard includes square chip carriers

with 16-, 20-, 24-, 32-, 40-, 48-, 64-, 84-, and 96-inpud

output terminals.

In addition, JEDEC recently proposed a rectangular varia-

tion of this package with 32

Il0

and staggered terminals.

C. 25-Mil Center and 20-Mil-Center Families

The JEDEC 50-mil and 40-mil centerline standard chip

carriers are inefficient for

100

to 124 terminal counts. To

solve some limitations of JEDEC chip carriers for packag-

ing LSI and VLSI circuits with high terminal counts, an ad

hoc task group was established through the IEEE Computer

Society's Technical Committee on Packaging in late 1980.

The group agreed on a number of basic requirements:

Both

0.5

and 0.635 mm centerline spacing chip carrier

packages will be used and should be standardized.

Ceramic and plastic packages should be standardized fol-

lowing the compatible mounting concept of the JEDEC

1.27 mm standard packages.

Certain mechanical tolerances must be maintained and

specific mechanical features for socketing are required.

3-18

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services