IPC-CM-770D-1996 - 第63页

January 1996 IPC-CM-770 O00 % -1 DETAXL *A8 -m 1' 4 B A "i r. 1 I r B6 A I 7 9 Il 131S17192l 8 10 '12141618202 00660000000 iooooreo0.o ooomw~o+ooo mrw~~mooo~~ oomommmommo maommmooooo ~e~oooooooo ooeommomaa…

IPC-CM-770

Januaty

1996

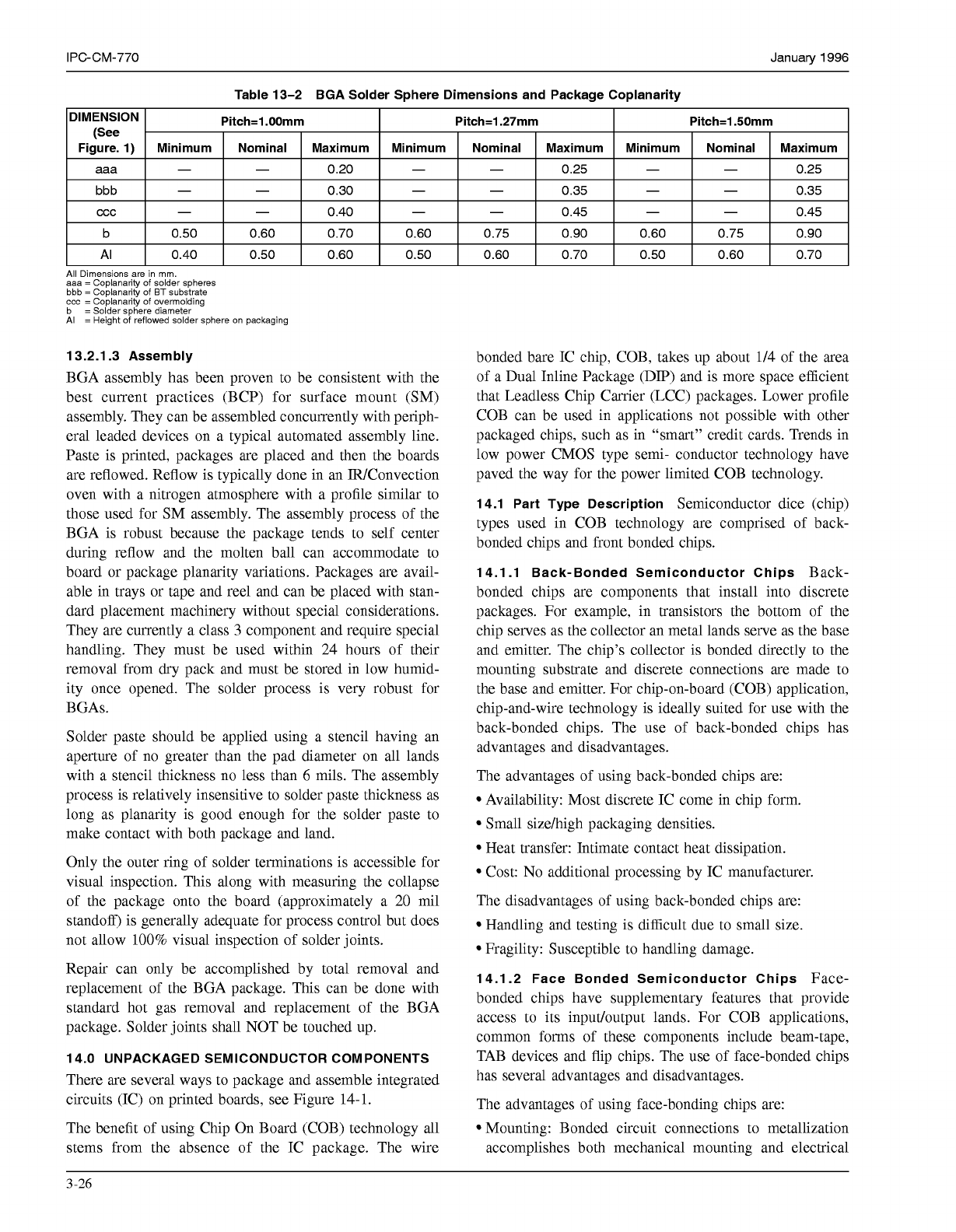

Table 13-2 BGA Solder Sphere Dimensions and Package Coplanarity

All

Dimensions are in mm.

aaa =Coplanarity of solder spheres

bbb =Coplanarity of

BT

substrate

ccc =Coplanarity of overmolding

AI

=

Height of reflowed solder sphere on packaging

b

=

Solder sphere diameter

13.2.1.3 Assembly

BGA assembly has been proven to be consistent with the

best current practices (BCP) for surface mount (SM)

assembly. They can be assembled concurrently with periph-

eral leaded devices on a typical automated assembly line.

Paste is printed, packages are placed and then the boards

are reflowed. Reflow is typically done in an IRIConvection

oven with a nitrogen atmosphere with a profile similar to

those used for SM assembly. The assembly process of the

BGA is robust because the package tends to self center

during reflow and the molten ball can accommodate to

board or package planarity variations. Packages are avail-

able in trays or tape and reel and can be placed with stan-

dard placement machinery without special considerations.

They are currently a class

3

component and require special

handling. They must be used within 24 hours of their

removal from dry pack and must be stored in low humid-

ity once opened. The solder process is very robust for

BGAs.

Solder paste should be applied using a stencil having an

aperture of no greater than the pad diameter on all lands

with a stencil thickness no less than

6

mils. The assembly

process is relatively insensitive to solder paste thickness as

long as planarity is good enough for the solder paste to

make contact with both package and land.

Only the outer ring of solder terminations is accessible for

visual inspection. This along with measuring the collapse

of the package onto the board (approximately a 20 mil

standoff) is generally adequate for process control but does

not allow

100%

visual inspection of solder joints.

Repair can only be accomplished by total removal and

replacement of the BGA package. This can be done with

standard hot gas removal and replacement of the BGA

package. Solder joints shall NOT be touched up.

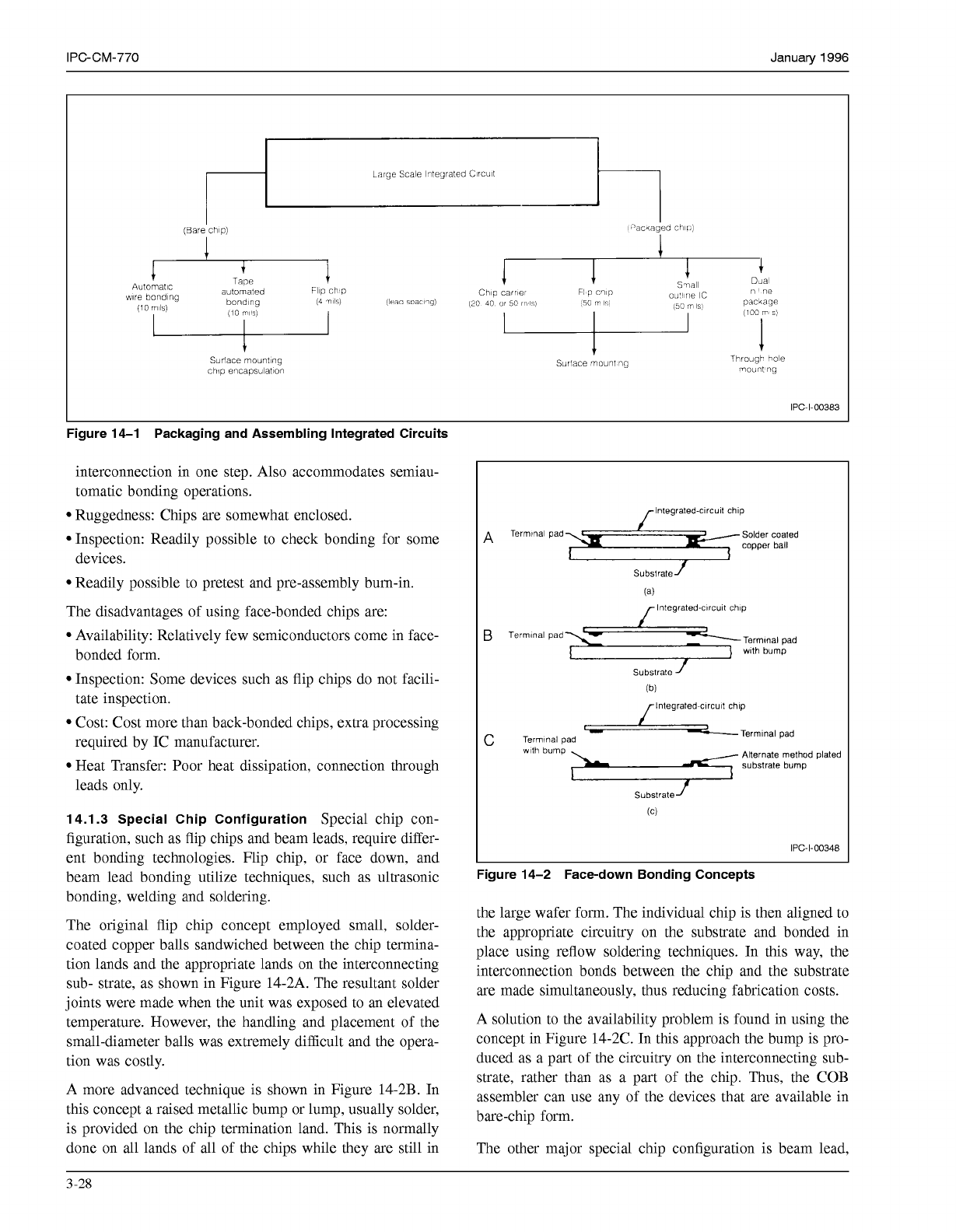

14.0 UNPACKAGED SEMICONDUCTOR COMPONENTS

There are several ways to package and assemble integrated

circuits (IC) on printed boards, see Figure 14-1.

The benefit of using Chip On Board (COB) technology all

stems from the absence of the IC package. The wire

bonded bare IC chip, COB, takes up about 114 of the area

of a Dual Inline Package (DIP) and is more space efficient

that Leadless Chip Carrier (LCC) packages. Lower profile

COB can be used in applications not possible with other

packaged chips, such as in “smart” credit cards. Trends in

low power CMOS type semi- conductor technology have

paved the way for the power limited COB technology.

14.1 Part Type Description

Semiconductor dice (chip)

types used in COB technology are comprised of back-

bonded chips and front bonded chips.

14.1.1 Back-Bonded Semiconductor Chips

Back-

bonded chips are components that install into discrete

packages. For example, in transistors the bottom of the

chip serves as the collector an metal lands serve as the base

and emitter. The chip’s collector is bonded directly to the

mounting substrate and discrete connections are made to

the base and emitter. For chip-on-board (COB) application,

chip-and-wire technology is ideally suited for use with the

back-bonded chips. The use of back-bonded chips has

advantages and disadvantages.

The advantages of using back-bonded chips are:

Availability: Most discrete IC come in chip form.

Small sizelhigh packaging densities.

Heat transfer: Intimate contact heat dissipation.

Cost: No additional processing by IC manufacturer.

The disadvantages of using back-bonded chips are:

Handling and testing is difficult due to small size.

Fragility: Susceptible to handling damage.

14.1.2 Face Bonded Semiconductor Chips

Face-

bonded chips have supplementary features that provide

access to its inputloutput lands. For COB applications,

common forms of these components include beam-tape,

TAB devices and flip chips. The use of face-bonded chips

has several advantages and disadvantages.

The advantages of using face-bonding chips are:

Mounting: Bonded circuit connections to metallization

accomplishes both mechanical mounting and electrical

3-26

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

January

1996

IPC-CM-770

O00

%

-1

DETAXL

*A8

-m

1'

4

B

A

"i

r.

1

I

r

B6

A

I

7

9

Il

131S17192l

8

10

'12141618202

00660000000

iooooreo0.o

ooomw~o+ooo

mrw~~mooo~~

oomommmommo

maommmooooo

~e~oooooooo

ooeommomaao

eo00

0.00

o000

0000

OOOC

o...

0.00

eo00

.OSO

sees

aamm

000.

m...

00eo

00.0

.amo

00.0

OO*O

oooemo

oommoeoooeo

"i

7

'Q

t

IPC-I-

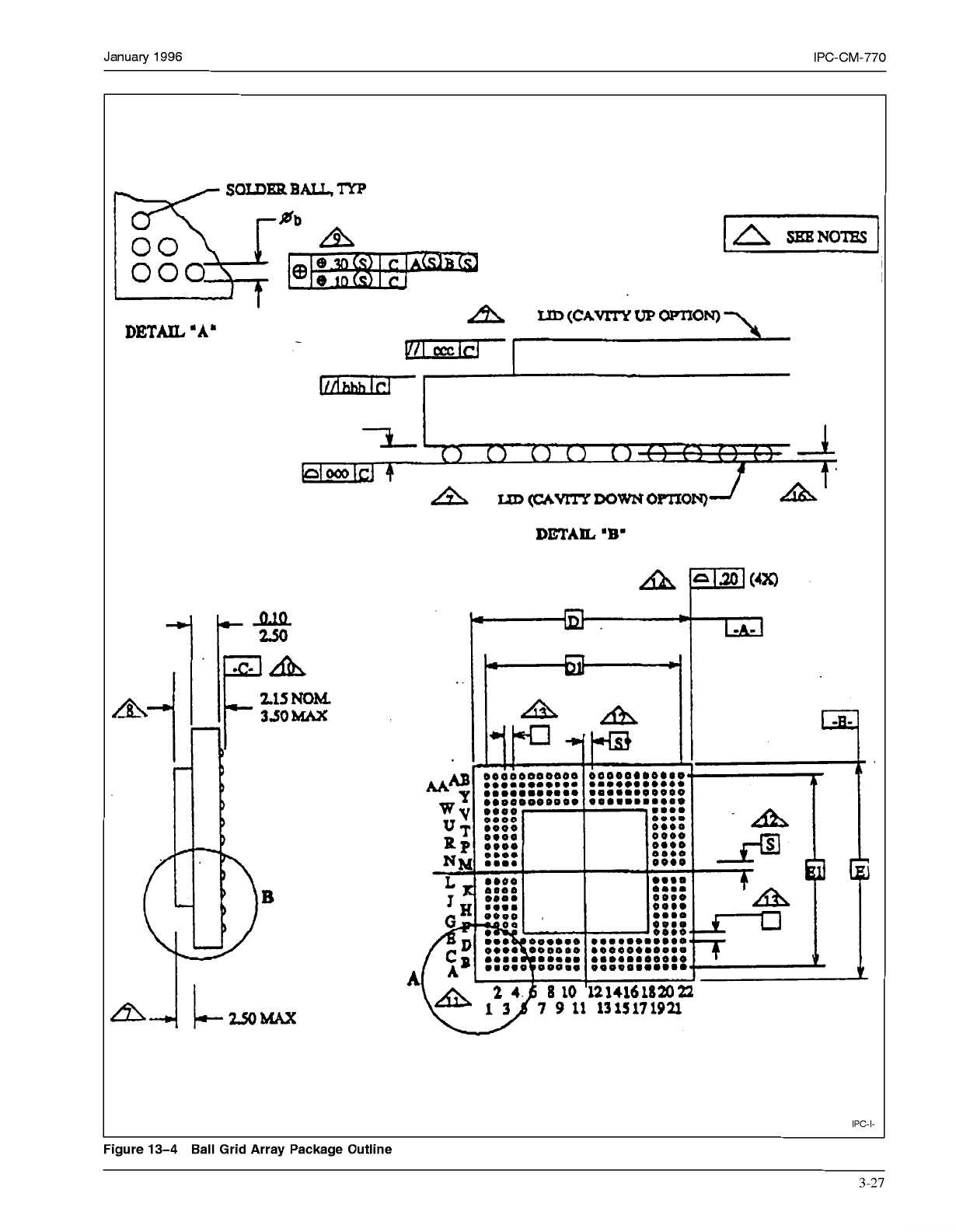

Figure 13-4 Ball Grid Array Package Outline

3-27

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

IPC-CM-770

Januaty

1996

i

*

(Bare chlp)

b'acxnged

chIr:)

1

4

Autornatlc

wlre

bondlng

(10

111llb)

automated Fl~p

ch

p

D&

r

'

ne

bondlng

(10

r,'$

Chlp carrler

(4

TIIS)

FI

p

CIIP

Ilpan snacllg)

(20

40

or

50

1%)

(50

m

158

ouIlrie IC

(53

m

IS1

+

pat:

(100

r's!

chip encapsulatlon

Surface

mountlng

Surface mount

ng

Througi-

bole

mount

ng

IPC-1-00383

Figure 14-1 Packaging and Assembling Integrated Circuits

interconnection in one step. Also accommodates semiau-

tomatic bonding operations.

Ruggedness: Chips are somewhat enclosed.

Inspection: Readily possible to check bonding for some

devices.

Readily possible to pretest and pre-assembly bum-in.

The disadvantages of using face-bonded chips are:

Availability: Relatively few semiconductors come in face-

bonded form.

Inspection: Some devices such as flip chips do not facili-

tate inspection.

Cost: Cost more than back-bonded chips, extra processing

required by IC manufacturer.

Heat Transfer: Poor heat dissipation, connection through

leads only.

14.1.3 Special Chip Configuration

Special chip con-

figuration, such as flip chips and beam leads, require differ-

ent bonding technologies. Flip chip, or face down, and

beam lead bonding utilize techniques, such as ultrasonic

bonding, welding and soldering.

The original flip chip concept employed small, solder-

coated copper balls sandwiched between the chip termina-

tion lands and the appropriate lands on the interconnecting

sub- strate, as shown in Figure 14-2A. The resultant solder

joints were made when the unit was exposed to an elevated

temperature. However, the handling and placement of the

small-diameter balls was extremely difficult and the opera-

tion was costly.

A more advanced technique is shown in Figure 14-2B. In

this concept a raised metallic bump or lump, usually solder,

is provided on the chip termination land. This is normally

done on all lands of all of the chips while they are still in

Integrated-clrcult chlp

A

Termlnal pad

1

Solder coaled

I

v

copper ball

Substrate

(a)

r

Integrated-clrcult chlp

I

Substrate

(b)

lntegrated~clrcult chlp

r

a

c

Terminal pad

C-Termlnal pad

Alternate method plated

substrate bump

IPC-1-00348

gure 14-2 Face-down Bonding Concepts

the large wafer form. The individual chip is then aligned to

the appropriate circuitry on the substrate and bonded in

place using reflow soldering techniques. In this way, the

interconnection bonds between the chip and the substrate

are made simultaneously, thus reducing fabrication costs.

A solution to the availability problem is found in using the

concept in Figure 14-2C. In this approach the bump is pro-

duced as a part of the circuitry on the interconnecting sub-

strate, rather than as a part of the chip. Thus, the COB

assembler can use any of the devices that are available in

bare-chip form.

The other major special chip configuration is beam lead,

3-28

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services