IPC CH-65B CHINESE.pdf - 第62页

•将 1206 片 式 组件 排 列, 同 上。 • 三 极管 封 装, 常 用 于 研究 焊 膏 的 品质 , 乳 胶 掩 膜 剥 离 程 度或者接 触 -上 升 的 焊接操作 。 • 使 用一个 隔 离模具 的单 BGA 测试模 式 ( 测试 BGA 底 部的 残留 ) 。 • 使 用一个 隔 离模具 的单 QFP 测试模 式 ( QFP 底 部的 残留 ) 。 • 单 LCC 测试模 式 ( 测试 低托高高 度 的清洗 效果 ) …

MIL-STD-2000A 在1995年被废除且无替代的标准。然而,为了满足旧的军事合同的要求,B-36测试

工具仍然被使用了几年。虽然MIL-STD-2000在很久之前就已经被废除,美国国防承包商经常由于在

那段时期确立的合同要求坚持执行此标准要求。对于小批量生产而言,当替代需要大量再认证工组

时,符合MIL-STD-2000要求常常是更具成本效益的

选择。

虽然 更新的J-STD-001版本允许其它测试工具,很多美国国防承包商仍然使用B-36测试板评估认

证。为了与边插连接器兼容,板上的接触手指通常采用镀金。其它金属化处理一般采用裸铜,但其

它的表面处理方式也可以。为了保证LCC(有引线芯片载体)有5mil的托高高度,阻焊的用量非常有

限(点或者面)。

阶段2的测试工具

的优点和缺点归纳如下:

优点

•混合工艺板-可以测试焊膏和波峰焊料的影响。

• 有地/防护电路隔离所有的SIR测试图形。

• SMT和通孔都不昂贵。

• 可与其它使用此板的方案比较结果。

• 使用此工具可以得到很多好的制程评估的信息。

• 可用于清洗效果和助焊剂滞留测试。

• 呈现热考验或者热阴影区。

• 在实际产品上6mil的图形更具有代表性。

• 可用于返修或者焊接润湿测试。

缺点

•如果没有SMT加工能力加工将很困难(例如:只有波峰焊接)。

• 阻焊只在非常限制的区域(8点)。

• 一般而言测试更加昂贵(如果考虑连接方式的花费)。

• 一般而言材料和加工都更加昂贵。

• 6mil的梳状图的选择性定位使得裸板的制造产量更小。

后续的测试工具,例如CSL/ Foresite Umpire板或者是IPC-B-52

测试板,都是学习基于IPC-B-36的实

验方案后设计的。考虑到更高级的测试工具在阶段2工作的实用性,不推荐IPC-B-36测试组件作为阶

段2的测试工具。

6.3.1.2 CSL/Foresite Umpire 测试⼯具 这种测试工具最初是污染研究实验室(现在的Foresite)在

1998-99年间,作为一种包含元器件以及能够代表超越从IPC或者Bellcore可获得的简单裸板的改进而

设计的。目的是一种相对便宜的测试工具

可以用于组装过程残留物的检查。评估板的图片如图6-3所

示。

测试图形

• 三种IPC-B-24测试模式。

• 无阻焊(层压板/助焊剂的相互影响),以便与J-STD-004绝缘电阻测试关联。

•条状阻焊(阻焊生长检查和滞留效应)。

• 整板阻焊(助焊剂对阻焊特性的影响)。

•将0805片式组件(1.0兆欧,0.1瓦)排成一行,用于检查其器

件体及粘合特征下的电迁移。

2011年7月 IPC-CH-65B-C

47

Copyright Association Connecting Electronics Industries

Provided by IHS under license with IPC

Not for Resale, 11/27/2015 19:13:55 MST

No reproduction or networking permitted without license from IHS

--`,`,,,,`,`,,,`,,,`,`,`,`,,,```-`-`,,`,,`,`,,`---

•将1206片式组件排列,同上。

• 三极管封装,常用于研究焊膏的品质,乳胶掩膜剥离程度或者接触-上升的焊接操作。

• 使用一个隔离模具的单BGA测试模式(测试BGA底部的残留)。

• 使用一个隔离模具的单QFP测试模式(QFP底部的残留)。

• 单LCC测试模式(测试低托高高度的清洗效果),与IPC-B-36的4D模式一致。

•将DIP封装在通孔焊接

时排成一行(检查圆角的形成)。

• 单PGA插槽,用来检查插座的滞留效应。

• 带有划格掩膜的Bellcore图形的附连板,用于电信组装者按照Bellcore GR-78-CORE标准测试表面绝

缘电阻(SIR)。

• 包含IPC-B-36 D象限图形的附连板,用于军品及IPC 3级用户的J-STD-001认证。

优点

• 作为一种评估组装材料和制程的测试工具,代表

当时对IPC测试板的重大改进。

• 可以供OEM/EMS选用材料。

• 单个附连板可用于MIL-STD-2000A 的相关工作。

• 第二块附连板可以用于电信供应商对Bellcore的研究。

•多数绝缘电阻测试板包括SMT元器件、BGA和连接器作为重要的评估确认点。

• 为绝缘电阻测试设计的板子。

•几个大的OEM厂使用它们自己的评估工具。

缺点

•这种板需要特殊的分立元器件以

选择封装。

• SOT-23元器件不像最初的设计一样工作。

• 设计者遗漏了第一条规则中的增加并联电阻,所以在表面绝缘电阻测试中底面的SMT片式器件看起

来像1兆欧姆电阻。

• 对于那种图形电解电容的容值受信号上升时间的影响将产生“奇数”测量值。

• 测试板的夹具很复杂。

• 在那段时间供应商对标准芯片(包括炸开的晶

片或者菊花链)及分立芯片(内部没有连接)掌握不

到位,使一些组件运行时使用到了坏件从而导致某些图形出现短路。

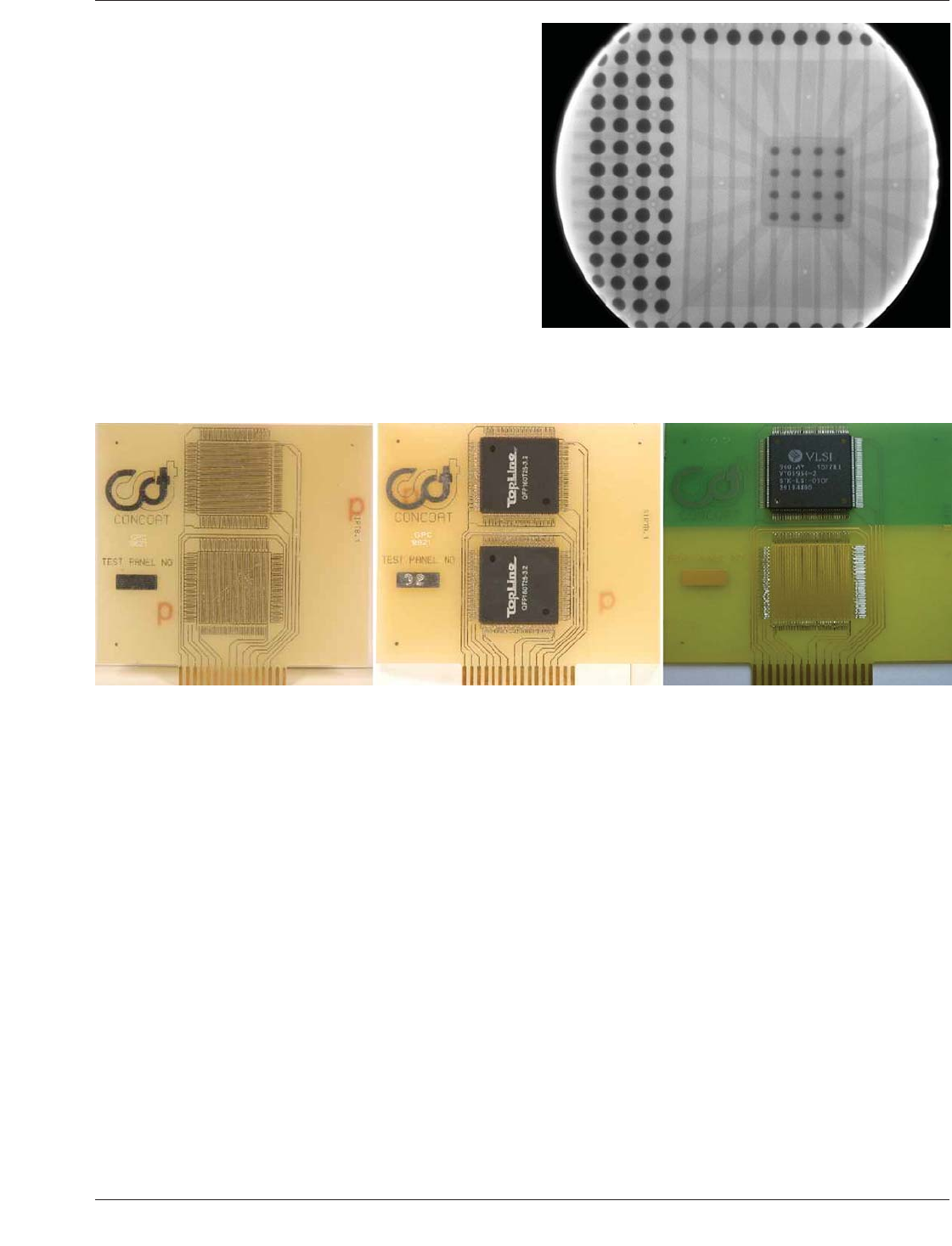

图6-3 Umpire板

IPC-CH-65B-C 2011年7月

48

Copyright Association Connecting Electronics Industries

Provided by IHS under license with IPC

Not for Resale, 11/27/2015 19:13:55 MST

No reproduction or networking permitted without license from IHS

--`,`,,,,`,`,,,`,,,`,`,`,`,,,```-`-`,,`,,`,`,,`---

• BGA封装后 发现有缺陷(见图6-4)。所选择的

BGA封装的中央有16个球,它完全是用于散热

的,所以在封装内部是短路在一起的。内部的短

路引起了板上SIR图形的短路。在组装操作之前

这16个锡球需要被清除。

•如今Umpire板继续用于工艺研究和效果确认。从

这种测试工具学习到的很多经验体现到了IPC-

B-52

的测试工具的设计中。

6.3.1.3 Gen3系统测试样⽚ 这种附连测试板

(图6-5)是英国GE3系统公司(以前的Concoat

系统公司)开发的,作为调查QFP的引脚和元器件

的细节距元器件底部之间的残留物效果的一种小

型的、价格便宜的实验工具。因此,它可用于阶

段1和阶段2类型的分析。

优点

•低成本的测试工具,容易大量生产。

• 组装成本低,可以适用于大量的样本尺寸。

缺点

•

一般不施加阻焊(但是可以采用,如右图所示)。

6.3.1.4 SMTA Saber板 从20世纪90年代开始,表面贴装技术协会(SMTA)saber板(图6-6)就作

为一种进货评估的工具被使用。该测试板是典型的通孔和表面贴装元器件混装的电路板,最常用于

焊接曲线的优化。它有一个单独的SIR测试图形(5段),与Bellcore风格大的方形扁平封装下面的图

形类似

。5分段梳状图的末端引出至表面贴装焊盘,与硬件装置连接。测试图形的末端间隔很小,当

进行导线连接时必须非常小心,以确保助焊剂的施加不使接触的焊盘桥接。测试图形不与任何元器

件的引线连接,所以不需要特殊的元器件。Saber板是价格较低的裸板。该板的Gerber文件可以从许

多供应商获取,因此该板也用

于不同的板材组合制造。如果使用了菊花链元器件,该测试板也可用

于焊点的可靠性研究。应该注意的是,底面和顶面是镜像的,菊花链元器件需在顶面工作,而不是

在底面。

SMTA的Saber板用于制造业研究有很多年,可以从很多供应商获取。在这个组件上有一种专业的SIR

测试图形(在大的QFP下面),所以如果使用硬接线的话,可以在这块板子上进行SIR测试。这块板

图6-4 有缺陷的BGA封装

图6-5 系统附连测试板

2011年7月 IPC-CH-65B-C

49

Copyright Association Connecting Electronics Industries

Provided by IHS under license with IPC

Not for Resale, 11/27/2015 19:13:55 MST

No reproduction or networking permitted without license from IHS

--`,`,,,,`,`,,,`,,,`,`,`,`,,,```-`-`,,`,,`,`,,`---