TR7700QE_Software_ch-v3.0_20180328 - 第105页

Test Research, Inc. TR7700Q E User Gu ide – S o f twar e 82 圖 129 : 3D 框 – Chip 類別檢 測框配置示意圖 - Lead :僅用於有導腳的 元件。計算高度的方式 是以檢測框內部所 有位置的高度進行 平 均。檢測框須放置在導 腳尾端位置 ( 作為 Layer1) 。框的位置配置如 下圖所示。 圖 130 : 3D 框 – Lead 類別檢測框配置示 意圖 絕對…

Test Research, Inc.

TR7700QE User Guide–Software 81

連結:設定 Base 要與哪個 Layer 或 Warp 使用(預設為 All layer)。設定為 Warp 的使用時

機是當元件周圍有多層高度、周圍底層資料太少 Warp 補償有問題或軟板。

ii. 當選擇 Layer 1~4時:

啟用平整度:進行平整度的量測。此為特殊功能,詳細設定請參閱平整度量測文件。

基準模式:選擇使用 Auto Mode 或者 Manual Mode。使用 Auto Mode 的話,系統會依照

條紋光掃描後自動設定基板的高度。若使用 Manual Mode的話,使用者必須手動再新增

一個高度檢測(3D)框並設定層級為 Base。

備註:當有使用頁籤面板[新增]>[整體基底]功能時,板子的基底將優先以整體基底設定的

位置為基底,而不是 Auto Mode或者 Manual Mode 所設定的 Base。

類型(當選擇 Layer 1~4 或 Solder 層時):可選擇 Normal、Chip、Lead 或 Solder。

- Normal:適用於各種手動畫框的情況,計算高度的方式是以檢測框內部所有位置的高

度進行平均。可建立 Base、Layer1、Layer2(視情況)、Layer3(視情況)或 Layer4

(視情況)的 3D 檢測框。框的位置配置如下圖所示。

圖 128:3D 框 – Normal 類別檢測框配置示意圖

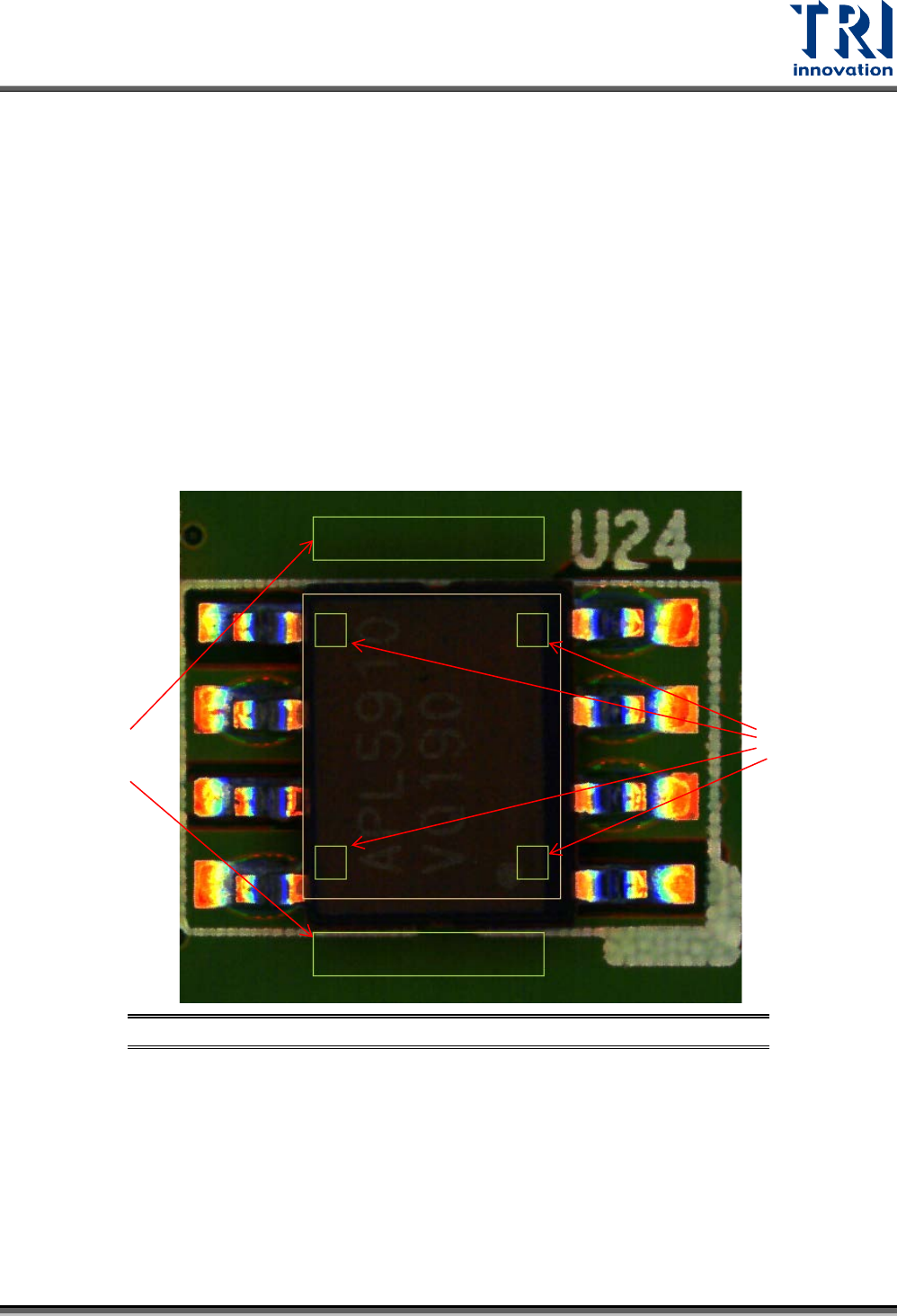

- Chip:僅用於晶片電阻元件,計算高度的方式是以檢測框內部預設四個位置的高度進

行平均。檢測框須包含晶片元件、焊盤和電路板底板,只須建立 Layer1 層的 3D 框。

框的位置配置如下圖所示。

Layer1

Base

Test Research, Inc.

TR7700QE User Guide–Software 82

圖 129:3D 框 – Chip 類別檢測框配置示意圖

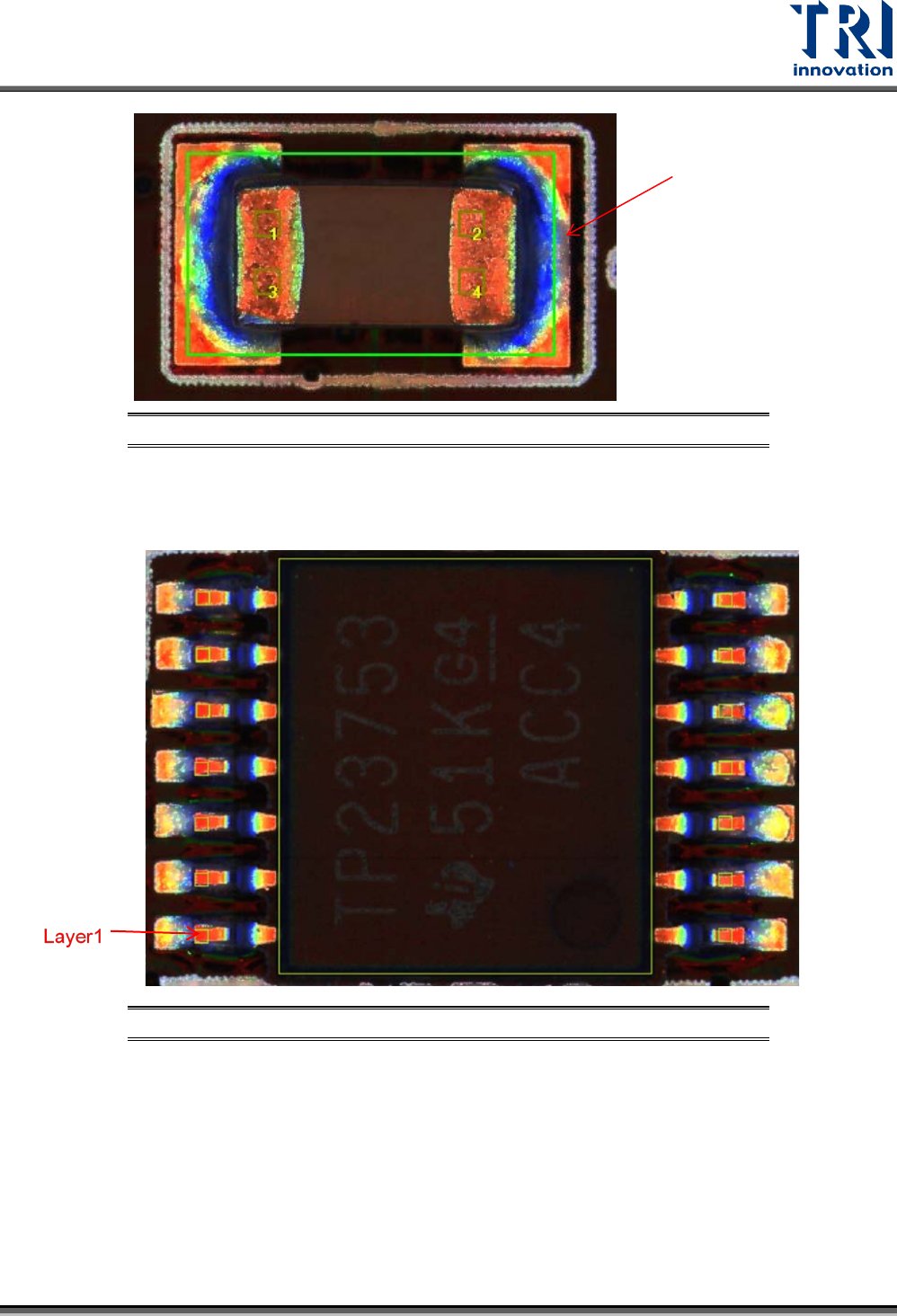

- Lead:僅用於有導腳的元件。計算高度的方式是以檢測框內部所有位置的高度進行平

均。檢測框須放置在導腳尾端位置(作為 Layer1)。框的位置配置如下圖所示。

圖 130:3D 框 – Lead 類別檢測框配置示意圖

絕對高度:絕對高度指的是 Base 到 Layer 的高度。

- 絕對高度標準:設定所測量物體的絕對高度值。

- 絕對高度正允差:設定絕對高度值的上限。

- 絕對高度負允差:設定絕對高度值的下限。

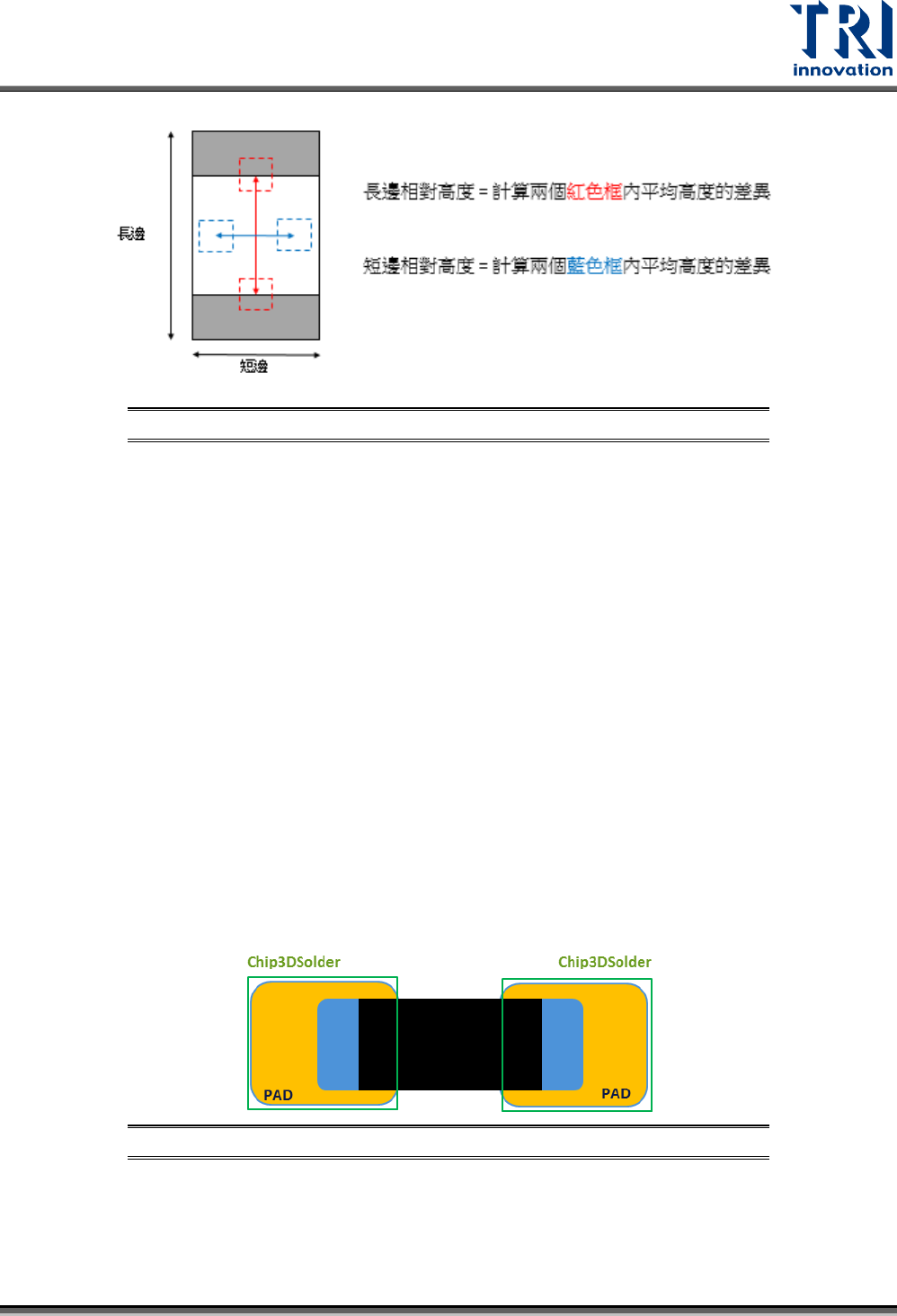

長邊/短邊相對高度:相對高度指的是一個 Layer 內兩個不同區域的高度差異。

- 高度允差:設定長邊兩個區塊內的平均高度差異允差。對於晶片元件,長邊相對高度指

的是元件不同區域間所算出高度的相對差異;對積體電路元件,相對高度指的某一導腳

與同一排最低導腳的高度差異。

Layer1

Test Research, Inc.

TR7700QE User Guide–Software 83

圖 131:3D 框 – 相對高度與確認側立功能差異計算示意圖

夾角量測

- 夾角上限/下限:設定 Base 與 Layer 平面的夾角上下限。

最大/小高度:設定量測高度的上下限。

高度上限(%):將檢測框內所有位置的高度值畫出常態分佈圖,然後將此值到 100%內的

值濾掉不列入計算。

高度下限(%):將檢測框內所有位置的高度值畫出常態分佈圖,然後將 0 到此值濾掉不列

入計算。

進階參數與其相對應的合格標準

距離連結:直接設定父屬性框與子屬性框的中心點相對位置,使子屬性框不受移動影響。

自動套用:自動計算檢測框設定在 1-10 層時的高度。

3.6.2 焊錫高度(3DSolder)框

1) 用途:用來量測元件的爬錫狀態。

2) 檢測原理:利用 3D 高度來量測爬錫狀態。

檢測配置方式:如下圖所示,檢測框位置大小須包含完整的錫墊(略大於焊盤)、元件電極端與元

件本體。

圖 132:焊錫高度框配置方式

3) 參數設定畫面與說明: