(TI)对半导体器件的长期存储评估.pdf - 第8页

Figure 10-1. Solder Stencil in Holder with Solder Figure 10-2. Solder Paste Printed Figure 10-3. Component Placement Equipment Figure 10-4. Component Placement Equipment Figure 10-5. Component Placement Arm Figure 10-6. …

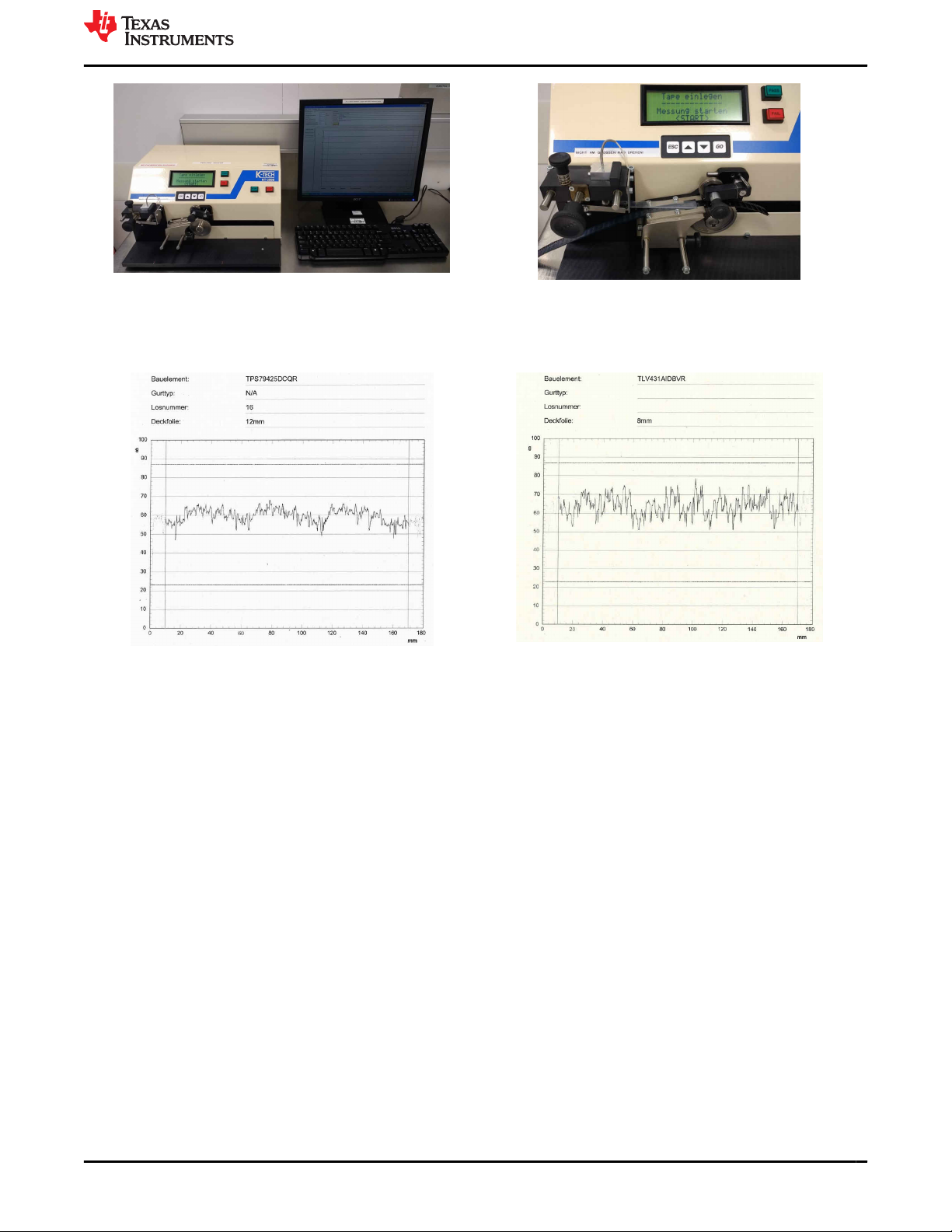

Figure 8-1. Cover Tape Peel Strength Test Setup

Figure 8-2. Cover Tape Peel Strength Test

9 Cover Tape Peel Strength Measurement Results

Figure 9-1. Cover Tape Peel Strength Test Result

for 16 mm Tape. Reel #16 Manufactured September

2005

Figure 9-2. Cover Tape Peel Strength Test Result

for 8 mm Tape. Reel #20 Manufactured December

2000

10 Solderability Evaluation

10.1 Test Description

Samples from each of the selected lots were tested for solderability using the Surface Mount Process Simulation

Test (Test S1 of JEDEC standard J-STD-002E). Lead-free (SnAgCu) solder paste, with no-clean flux, was used

to reflow at ≈240°C peak package temperature in air atmosphere.

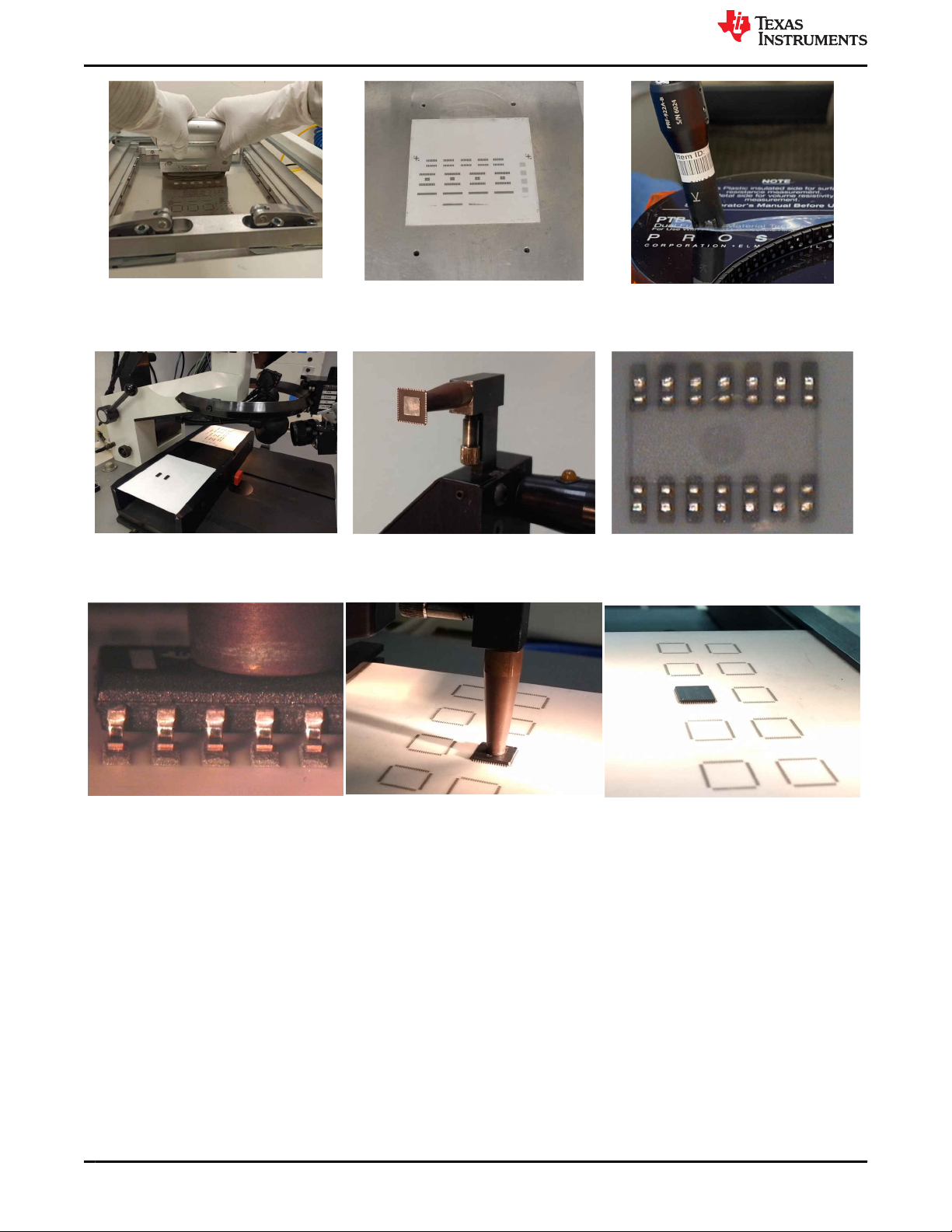

Figure 10-1 shows how solder paste printing is performed on a ceramic substrate using a manual solder stencil

fixture. The solder paste stencils are laser cut and electro polished. After printing the solder paste on the ceramic

plate substrate as shown in Figure 10-2, the substrate is fixed in a movable table under the microscope as

shown in Figure 10-3 to align the solder paste print pattern with the component leads in the holder as shown in

Figure 10-6 through an overlay optical image.

www.ti.com Cover Tape Peel Strength Measurement Results

SLPA019 – SEPTEMBER 2021

Submit Document Feedback

Long Term Storage Evaluation of Semiconductor Devices 7

Copyright © 2021 Texas Instruments Incorporated

Figure 10-1. Solder Stencil in

Holder with Solder

Figure 10-2. Solder Paste Printed

Figure 10-3. Component

Placement Equipment

Figure 10-4. Component

Placement Equipment

Figure 10-5. Component

Placement Arm

Figure 10-6. Overlay Image

Package of Lead and Solder Paste

Figure 10-7. Side Camera View for

Final Placement Height

Figure 10-8. Placement Tool on

Substrate

Figure 10-9. Placed Component

on Substrate

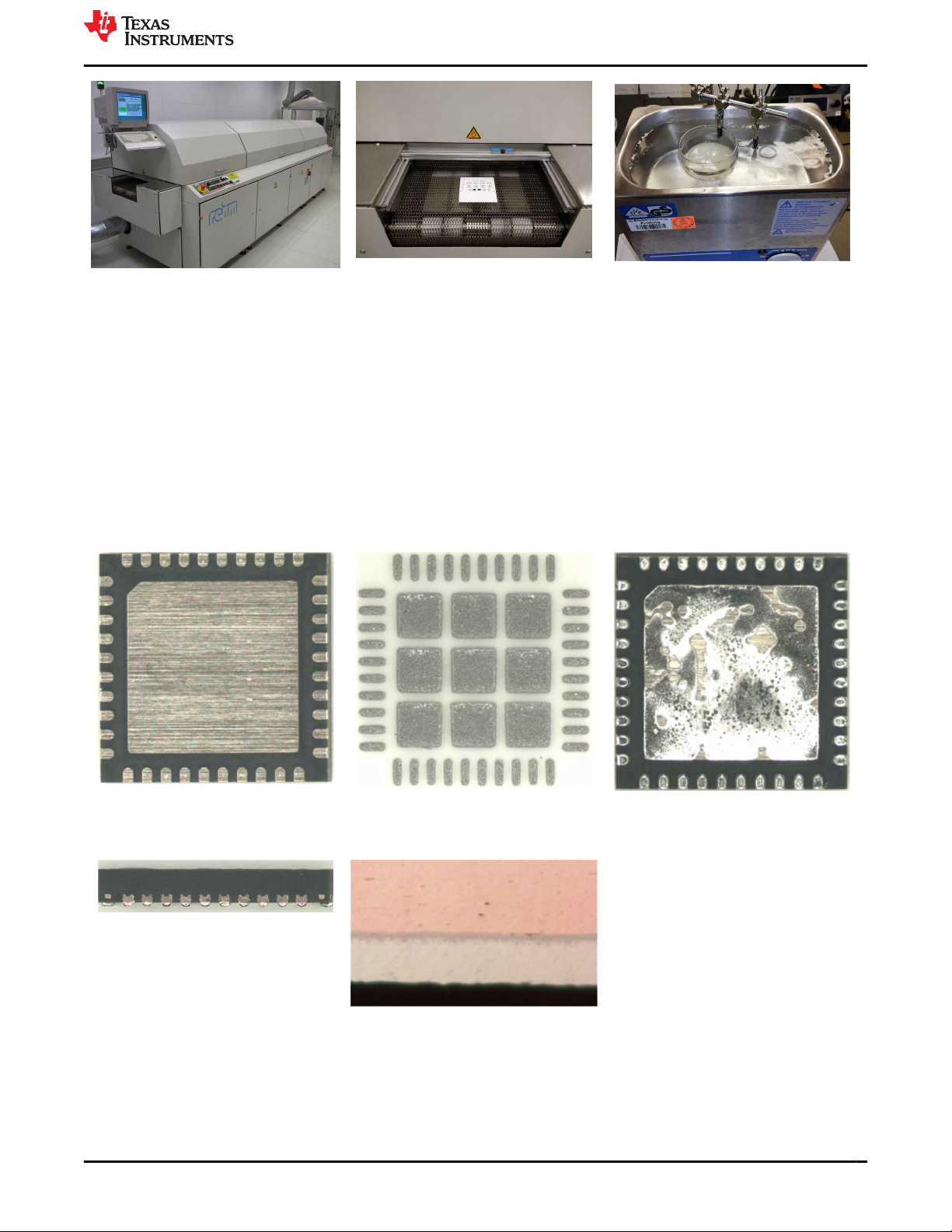

The ceramic substrates were run through the convection reflow oven with a measured package temperature of

≈240°C and air atmosphere (Compressed Dry Air purge).

After reflow, the soldered products were cleaned in an ultrasonic bath with flux removal agent followed by DI

water rinse before the optical inspection of the solder wetting on the package leads.

Solderability Evaluation www.ti.com

8 Long Term Storage Evaluation of Semiconductor Devices SLPA019 – SEPTEMBER 2021

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Figure 10-10. Reflow Oven

Figure 10-11. Substrate on

Transport Belt

Figure 10-12. Ultrasonic Flux

Cleaning

Samples from Table 5-1 were tested for solderability with a typical sample size of 9-10 units per lot. Example

images from the different packages and storage time are shown in the Section 11.1.

The package samples used for solderability testing were picked out of the tape and reel or from tubes baked for

four hours at 155°C in dry air to simulate standard J-STD-002 aging and then placed on the printed solder paste

pattern on the ceramic plate.

11 Solderability Test Results

11.1 Leadless Package

Sample batch #6: 13 years storage, MSL 3, lead finish: NiPdAu

Figure 11-1. Unit After Bake 4Hr/

150°C

Figure 11-2. Solder Paste Print

Patern

Figure 11-3. Bottom View After

Test

Figure 11-4. Side View

Figure 11-5. Cross Section

Through Thermal Pad, Showing

Intermatillic Between Base Ni

Layer on Copper and Solder

www.ti.com Solderability Test Results

SLPA019 – SEPTEMBER 2021

Submit Document Feedback

Long Term Storage Evaluation of Semiconductor Devices 9

Copyright © 2021 Texas Instruments Incorporated