SG_FSE_SiplaceHF_HF3_00193900-05_de - 第89页

1 - 21 S tudent Guide SIPLACE HF/HF3 Ausgabe 09/2005 3 Kommunikation und S teuerung 21 3.3.8.1 CAN-Bus gesteuerte Kopffunkt ionen am TWIN Head Die folgende Übersicht zeigt verschie dene, vo m CAN-System gesteuerte Ko pf …

1 - 20

Student Guide SIPLACE HF/HF3

3 Kommunikation und Steuerung Ausgabe 09/2005

20

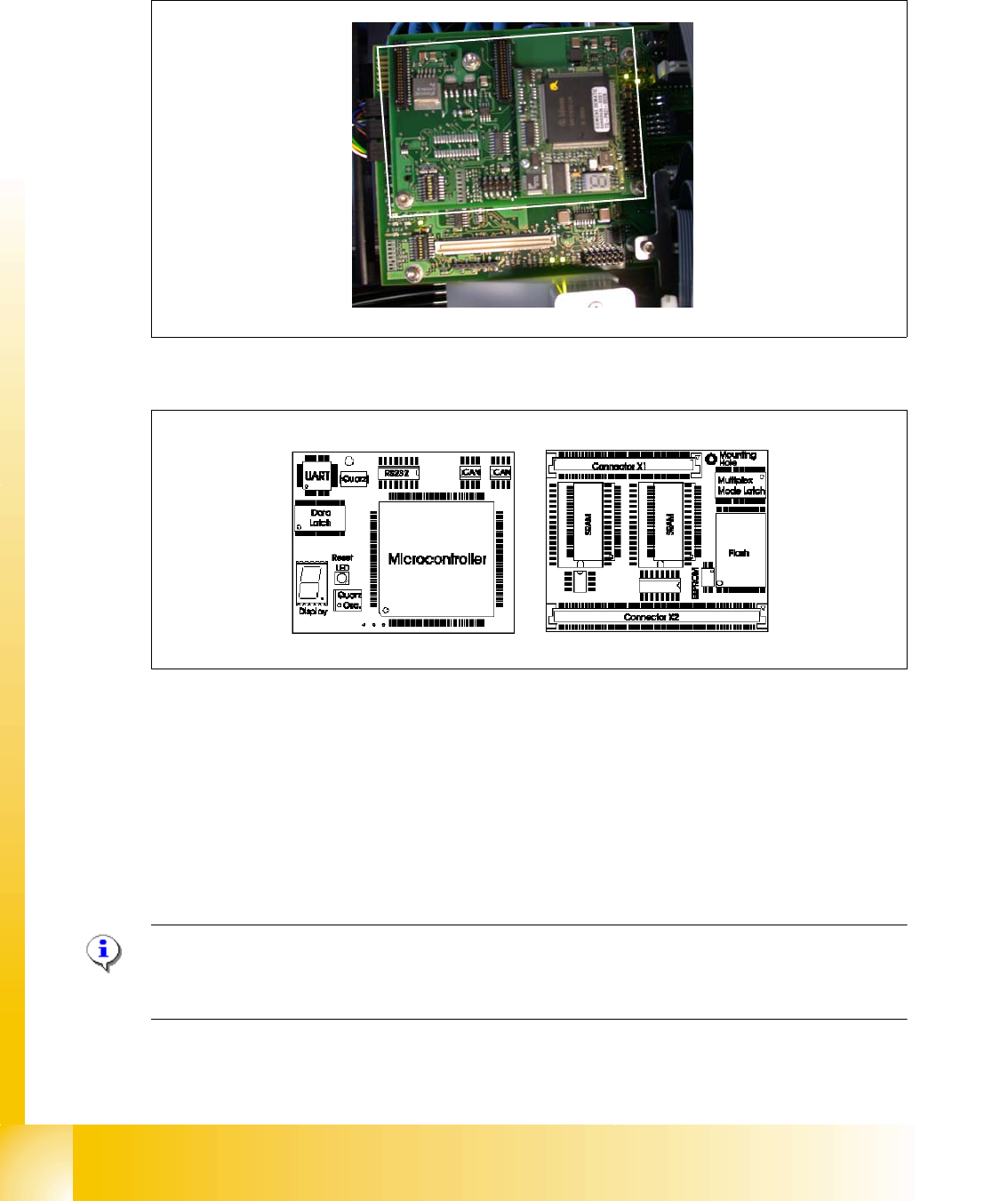

3.3.8 CAN-Bus Prozessorboard Twin Head

Die CAN-Bus Prozessor-Platine verwendet einen 16-Bit Mikrocontroller

Abb. 3.3 - 17 Can Bus Prozessorboard TWIN Head

Abb. 3.3 - 18 CAN-Bus Prozessorboard TWIN Head

Legende

Hinweis:

Über die 7-Segment-Anzeige wird der Status des 16 Bit PROZESSORBOARDS angezeigt.

Normaler Betriebszustand: " . " blinkt. (Beschreibung siehe Kapitel C&P Kopf). 3

(1) 16 Bit Mikroprozessor (2) CAN-Treiber

(3) 7-Segment-Anzeige (siehe Kapitel 8) (4) Reset LED

(5) Quarz für Prozessorfrequenz (6) Flash-Memory

(7) SRAM

2

1

4

5

3

6

7

1 - 21

Student Guide SIPLACE HF/HF3

Ausgabe 09/2005 3 Kommunikation und Steuerung

21

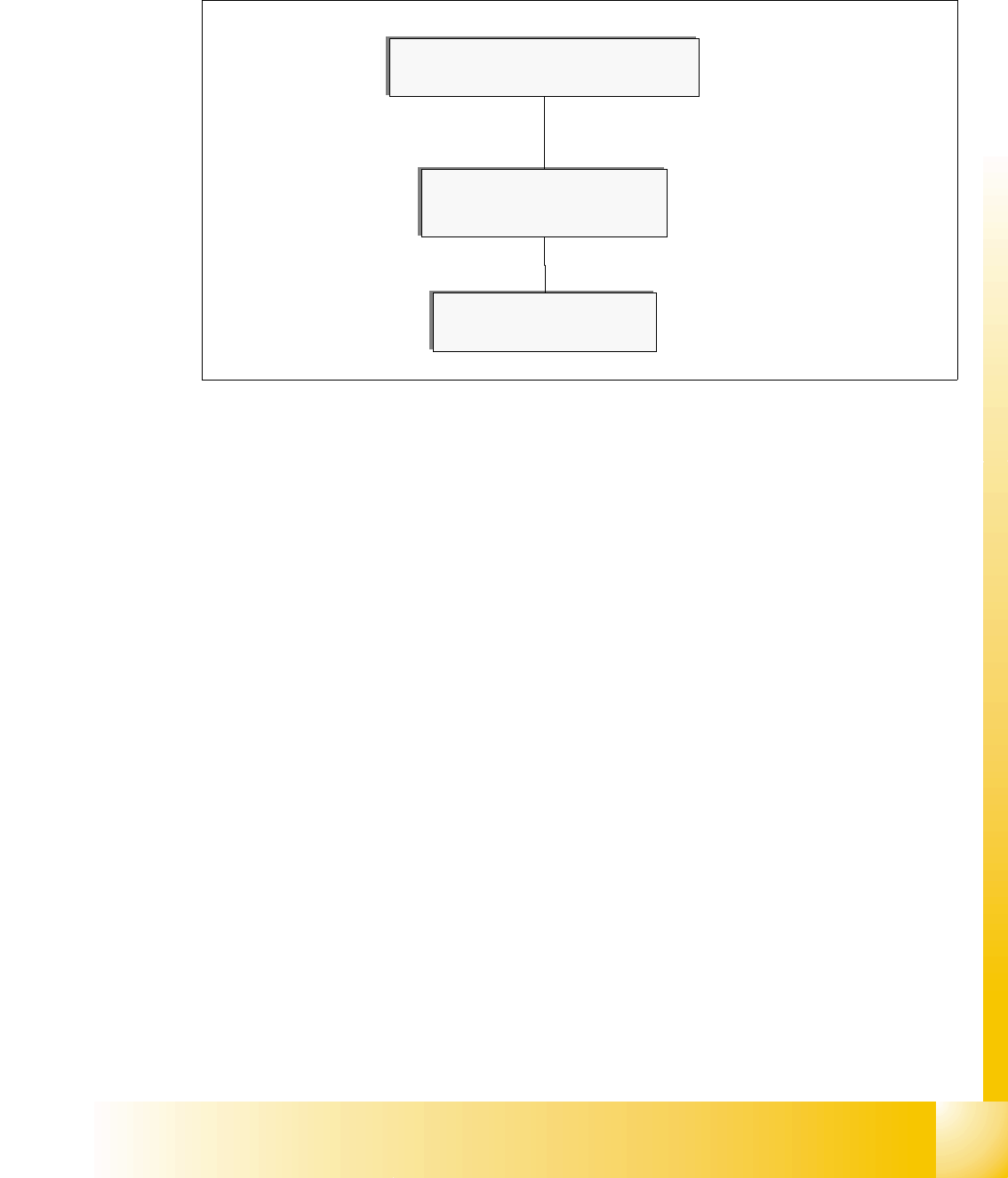

3.3.8.1 CAN-Bus gesteuerte Kopffunktionen am TWIN Head

Die folgende Übersicht zeigt verschiedene, vom CAN-System gesteuerte Kopffunktionen. Der

CAN-Bus steuert damit die Aktoren und Sensoren des Twin Heads.

Abb. 3.3 - 19 CAN-Bus gesteuerte Kopffunktionen am Twin Head

:

Vakuum / Blasluft

:

CAN Bus

Kommunikationsboard

16 Bit CAN Prozessorboard

am Twin Head

1 - 22

Student Guide SIPLACE HF/HF3

3 Kommunikation und Steuerung Ausgabe 09/2005

22

3.3.9 CAN E/A-Modul (SLIO) - HF bis MA.Nr. xx

Es sind 2 CAN-Bus E/A-Module in der HF-Maschine. Beide Module sind absolut identisch und be-

finden sich in Sektor 2 (Hauptverteiler) und Sektor 4 (Zwischenverteiler).

Funktionen:

– Microcontroller mit eingebautem CAN-Controller

– Datenspeicher

– Programmspeicher (Flash)

– CAN-Interface mit 9-Pin-Anschluss und Adresseinstellung

– 16 digitale Ausgänge 24 V mit Status-LED

– 24 digitale Eingänge 24 V mit Status-LED

– Download-Interface

– Stromversorgung 5 V und 24 V

8 digitale Eingänge können mit Hilfe eines FPGA (frei programmierbares Gate Array) logisch ver-

knüpft werden. Das FPGA wird für den Eingang von Sicherheitsmeldungen verwendet.

Abb. 3.3 - 20 CAN-E/A-Modul Sektor 2, Hauptverteiler