00197497-03_UM_SiplaceCA-Serie_DE - 第204页

4 SIPLACE Wafer-System (SWS) Betriebsanleitu ng SIPLACE CA-Serie 4.1 Funktionsbeschreibung Ab Softw areversion SR 708.0 Ausgabe 12/2014 204 4.1.3.3 Die-Erkennung und -Positionierung Die W afer sind grundsätzlich, mi t ei…

Betriebsanleitung SIPLACE CA-Serie 4 SIPLACE Wafer-System (SWS)

Ab Softwareversion SR 708.0 Ausgabe 12/2014 4.1 Funktionsbeschreibung

203

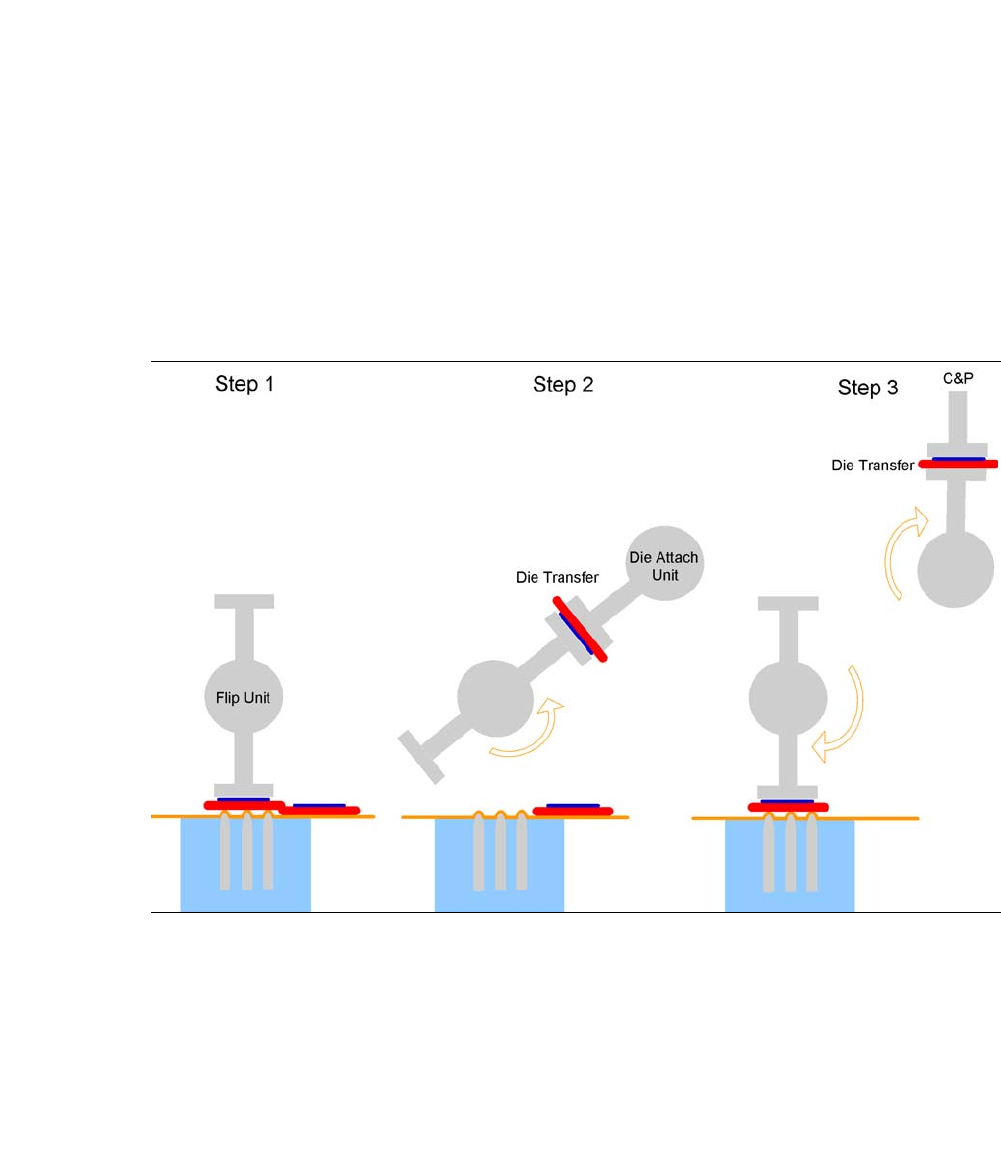

4.1.3.2 Die-Attach-Prozess

Für den Die-Attach-Prozess wird die optionale Die-Attach-Unit benötigt.

In diesem Verfahren wird das Die in der selben Oben-Unten-Orientierung bestückt wie es auf der

Wafer-Folie vorliegt ("face-up"-Bestückung).

Die-Attach ist das klassische etablierte Die-Bestückungsverfahren. Die-Attach erfordert einen zu-

sätzlichen Schritt um die Verbindungen vom Die zur Leiterplatte herzustellen (Drahtanschlüsse).

Abb. 4.1 - 3 Schritte des Die-Attach-Prozesses

Die Schritte des Die-Attach-Prozesses:

– Step 1: Die-Release

– Step 2: Das Die wird um ca. 130° gedreht und an die Die-Attach-Unit übergeben.

– Step 3: Die Die-Attach-Unit dreht das Die zur Abholposition und übergibt es an den Bestück-

kopf. Parallel dazu wird von der Flip-Unit das nächste Die abgeholt.

4 SIPLACE Wafer-System (SWS) Betriebsanleitung SIPLACE CA-Serie

4.1 Funktionsbeschreibung Ab Softwareversion SR 708.0 Ausgabe 12/2014

204

4.1.3.3 Die-Erkennung und -Positionierung

Die Wafer sind grundsätzlich, mit einer bestimmten Positions- und Winkeltoleranz, auf einer Wa-

fer-Folie befestigt.

Daher ist es nicht möglich das Die ohne Erkennung und Korrektur sicher in der Mitte der Ausste-

cheinheit zu platzieren. Dies ist besonders bei kleinen Dies notwendig um einen einwandfreien

Ausstechvorgang sicherzustellen.

Darüber hinaus kann es notwendig sein nur eine Auswahl an Dies zu verarbeiten. Eine solche

Auswahl kann über eine Ink-Punkt-Markierung auf "schlechten" Dies oder mit einer zum jeweili-

gen Wafer gehörigen Wafer-Map-Datei erfolgen.

Für diesen Verfahrensschritt ist die folgende technische Ausrüstung notwendig:

2-Achsen-Wafer-Tisch für die Positionierung

Wafer-Kamera-System für die Die- und die optionale Ink-Punkt-Erkennung

Optionales Wafer-Map-System

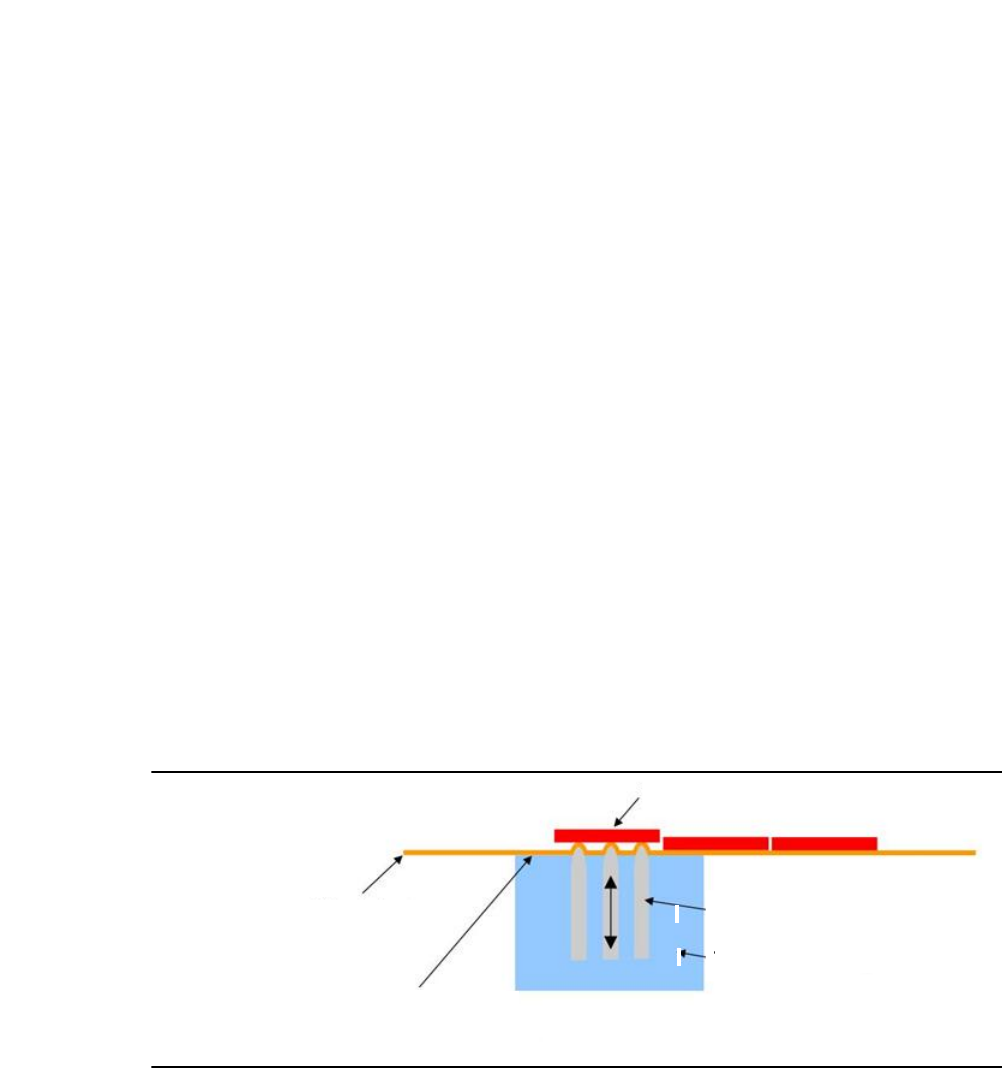

4.1.3.4 Ausstechvorgang

Ist das Die über dem Ausstechsystem zentriert, dann kann es mit Hilfe von Nadeln von der Wafer-

Folie abgelöst und an die Flip-Unit übergeben werden. Während die Nadeln das Die von der Folie

lösen, wird die Wafer-Folie in Richtung Ausstechsystem gesaugt.

Abb. 4.1 - 4 Die-Bereitstellungs-Prozess

Für dieses Verfahren ist die folgende technische Ausrüstung notwendig:

– Ausstechsystem mit austauschbarem Ausstech-Tool

Ausstechnadel

Vakuum-Kappe

Ausstechsystem

Aktives Bauteil - bereit zur Abholung

Wafer-Folie

Die Wafer-Folie wird mit Vakuum an

die Vakuum-Kappe angesaugt

Betriebsanleitung SIPLACE CA-Serie 4 SIPLACE Wafer-System (SWS)

Ab Softwareversion SR 708.0 Ausgabe 12/2014 4.1 Funktionsbeschreibung

205

4.1.3.5 Pickup-Prozess

Während des Pickup-Prozesses wird das Die an das Tool bzw. an die Pipette der Flip-Unit über-

geben. Die Flip-Unit übergibt das Die darauf entweder an den Bestückkopf (Flip-Chip-Prozess)

oder an die Die-Attach-Unit (Die-Attach-Prozess).

Die Die-Attach-Unit stellt das Die nach einem weiteren Drehvorgang für den Bestückkopf bereit.

Für diesen Verfahrensschritt ist folgende technische Ausrüstung notwendig:

Flip-Unit

Die-Attach-Unit (optional)

4.1.4 Embedded Wafer Level Ballgrid Array (eWLB/WLFO) Prozess

Embedded Wafer Level Ball Grid Array ist eine Verpackungs-Technologie die es erlaubt dünne

Bauteile mit hervorragender eklektischer Leistung mit einem Chip Fan Out herzustellen. D. h die

für die Anschlusspads verwendete Fläche ist größer als das eigentliche Silizium um SMD verträg-

liche Abstände der Kontatkierung zu ermöglichen.

Für diesen Prozess werden die Chip Bauelemente mit der aktiven Fläche nach unten (Face down)

auf einen Träger mit doppelt-klebender Folie bestückt. Nach der Bestückung wird diese Struktur

gemoldet. Nach dem Die-Bond Prozess des Trägers werden Wafer-Strukturierungs-Prozesse

verwendet, um die elektrische Kontaktierung herzustellen. Hierzu wird auch die Moldfläche um

das Silizium als Träger für „Leiterbahnen“ verwendet (Fan out). Anschließend werden die Bauteile

getestet, beschriftet und zum Beispiel in Gurte verpackt.