67021-ultraviolet-led-multi-chip-module-based-on-ceramic-substrate.pdf - 第5页

Figure 6: LED-chip soldered to an Al 2 O 3 su b- strate. Relevant process para meters are te mperature profile and reflow re gime as well as bonding force (app lied pressure duri ng placemen t and reflow). More than 30 a…

Stresses are significantly lower than for the solder

attach and thus below the ultimate tensile stresses

of the substrate materials. Due to lower Young’s

modulus of the adhesive – 1.2 GPa compared to

68 GPa for AuSn – the inherent stresses within the

adhesive layers are significantly lower than within

the solder. The results show equivalent stresses

within the adhesive of 3.1 MPa for 10 µm layers

and 2.6 MPa for 30 µm layers, respectively.

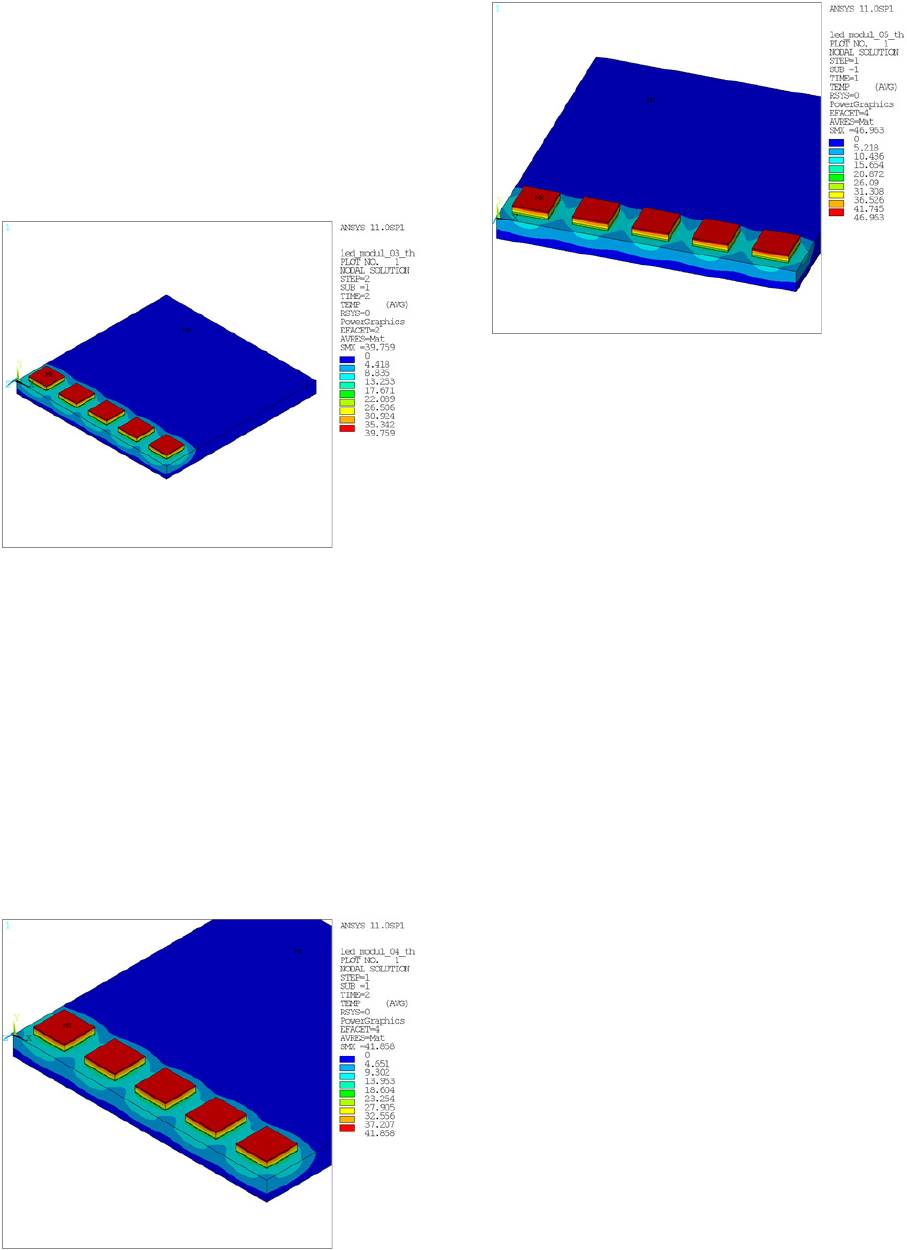

Figure 3: Temperature distribution within LED-

chips and Al

2

O

3

substrate (thickness 0.38 mm)

for eutectic AuSn solder (layer thickness 10 µm)

and 1.65 W thermal load.

Thermal analysis for a thermal load of 1.65 W per

chip results in chip temperatures of 42 K above

substrate temperature for 10 µm layers and 47 K for

30 µm layers (see Figure 4 and Figure 5). These

calculations indicate that a proper cooling of the

chips could be achieved using thermally conductive

adhesives. Thicker adhesive layers increase chip

temperature significantly. In the case of thin

bonding layers – either solder alloy or adhesive –

thermal properties are mainly influenced by the

chips and the substrate itself.

Figure 4: Temperature distribution within LED-

chips and Al

2

O

3

substrate (thickness 0.38 mm)

for silver-filled adhesive (layer thickness 10 µm)

and 1.65 W thermal load.

Figure 5: Temperature distribution within LED-

chips and Al

2

O

3

substrate (thickness 0.38 mm)

for silver-filled adhesive (layer thickness 30 µm)

and 1.65 W thermal load.

The results of the FE calculations show acceptable

thermo-mechanical stresses for both substrate ma-

terials and soldering with eutectic gold-tin. The

thermal matching of sapphire based LED-chips and

the used substrate materials AlN and Al

2

O

3

keep

the tensile stresses below ultimate yield strength.

Thermal results show proper extraction of heat

during operation. The high thermal conductivity of

AlN of 180 W/(m·K) leads to a lower chip tem-

perature during operation compared to Al

2

O

3

. Sil-

ver-filled adhesives provide similar performance if

thin layers could be successfully processed. The

results allow the comparison of different die-attach

technologies and can be transferred to other chip

types.

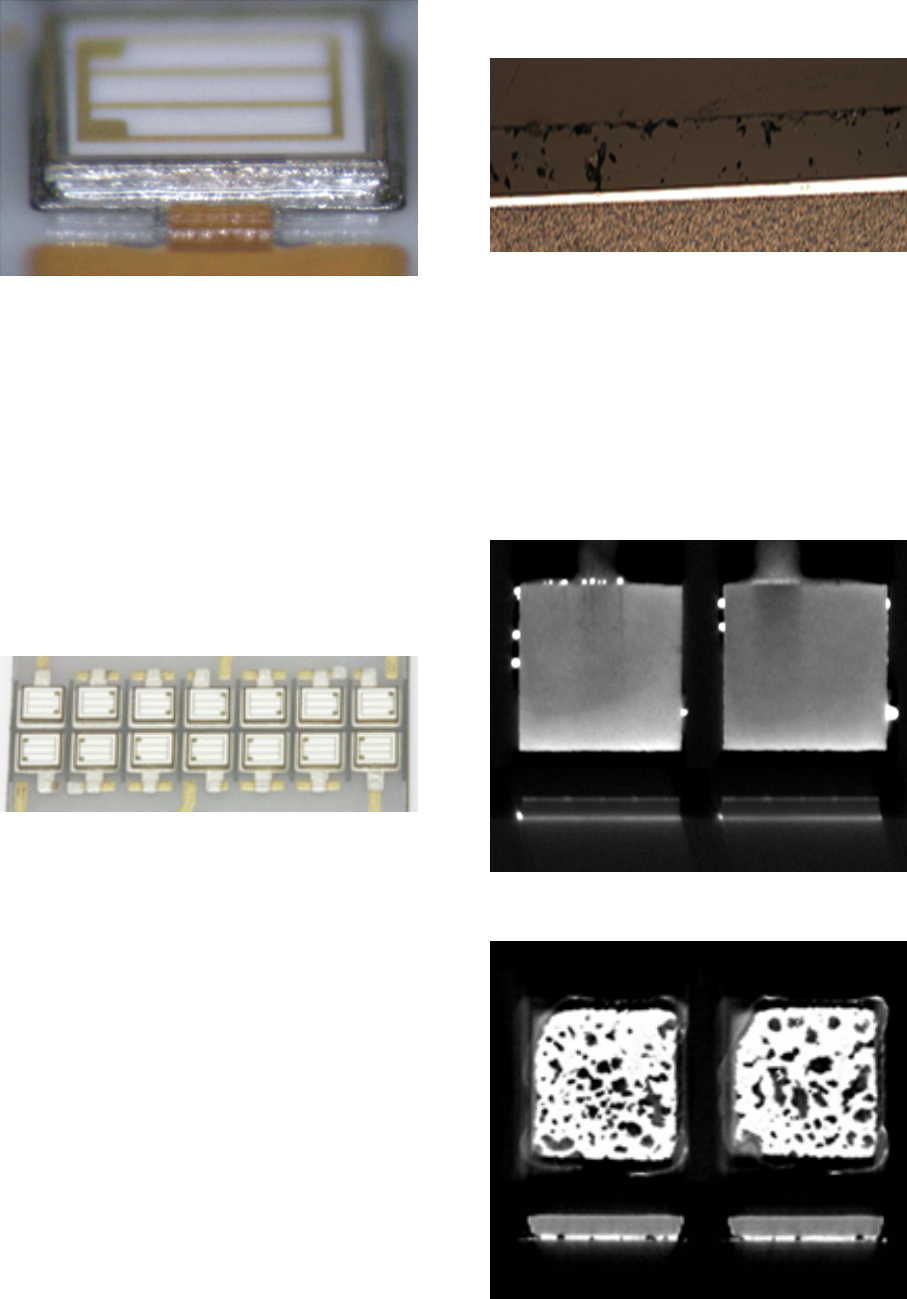

Experimental – Die Attach

Three different Die-attach technologies are compa-

ratively used: 1) eutectic gold-tin solder and flip-

chip-assembly, 2) standard vacuum reflow of a flux

enhanced SnPb solder (Figure 6), and 3) two differ-

ent silver-loaded adhesives. Flip-Chip assembly is

conducted using a ficonTEC Flip-Chip-Bonder BL-

2000 and a Finetech Fineplacer Lambda, respec-

tively. Reflow during flip-chip-placement is esta-

blished by using a heated pick-up tool (PUT) and a

hotplate with a substrate holder. The use of a sub-

strate hotplate allows a stand-by temperature below

solder alloy reflow and the subsequent placement

and soldering of single chips by the PUT. LED-

chips with a manufacturer-made gold metallization

are used for SnPb soldering and adhesive attach.

Sputtered eutectic gold-tin is used for additional

metallization of LED-chips for flip-chip-attach

[10]. An optional increase of solder layer thickness

is conducted by application of additional solder

volume by means of Solderjet Bumping [24].

IMAPS/ACerS 8th International CICMT Conference and Exhibition (2012) | April 16-19, 2012 | Erfurt, Germany

000241

Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2012/CICMT/000238/2360912/cicmt-2012-tp61.pdf by guest on 03 January 2023

Figure 6: LED-chip soldered to an Al

2

O

3

sub-

strate.

Relevant process parameters are temperature profile

and reflow regime as well as bonding force (applied

pressure during placement and reflow). More than

30 assemblies using testing elements are manufac-

tured for mechanical testing and process optimi-

zation. Soldering of chips using less than 10 µm

sputtered AuSn layers (as-sputtered, without addi-

tional solder applied) did not prove to be reliable

joined. Low shear forces and unregular wetting are

observed. An additional Ø300 µm solder sphere is

applied to provide for an additional solder layer

thickness of 12 µm. Fully operational 7×2-chip

samples are made for optical testing (Figure 7).

Figure 7: Fully assembled 7×2 UV-LED module.

The third die-attach technology used is adhesive

bonding with silver-loaded and thermally con-

ductive adhesives. Although being a well estab-

lished and commercially used technology the appli-

cation of highly filled adhesives requires major

adaptations of dispense and chip placement techno-

logies. The optimization of the process flow, curing

conditions and homogenization of the adhesive is

necessary to achieve reproducible thin joint fis-

sures.

Experimental – Analysis of Solder Joints

Mechanical testing of soldered components, both

LED-chips and testing vehicles is conducted using

shear force measurements. Using components with

an additional solder volume, 6 N to 18 N with glass

testing elements for variation of process parameters

are achieved. LED-chips show a shear force greater

than 10 N with the main failure mode being the

rupture of chips rather than failure of solder joints

or layer interfaces. Cross section views (Figure 8)

show a homogenous filling and a solder layer thick-

ness below 30 µm.

Figure 8: Cross section view of a AuSn soldered

LED-chip.

Micro-Computer-Tomography (Micro-CT) analysis

confirms a void free and homogenous solder layer

for AuSn soldering (Figure 9). In comparison the

micro-CT shows significant voiding for the vacuum

soldered LED-chips (Figure 10). The increase of

thermal resistance of solder joints with a higher

fraction of voids is obvious. Flux-free processing of

gold-tin solder furthermore eliminates the need for

additional cleaning after soldering.

Figure 9: Micro-CT of AuSn soldered LED-

chips.

Figure 10: Micro-CT of SnPb soldered LED-

chips.

IMAPS/ACerS 8th International CICMT Conference and Exhibition (2012) | April 16-19, 2012 | Erfurt, Germany

000242

Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2012/CICMT/000238/2360912/cicmt-2012-tp61.pdf by guest on 03 January 2023

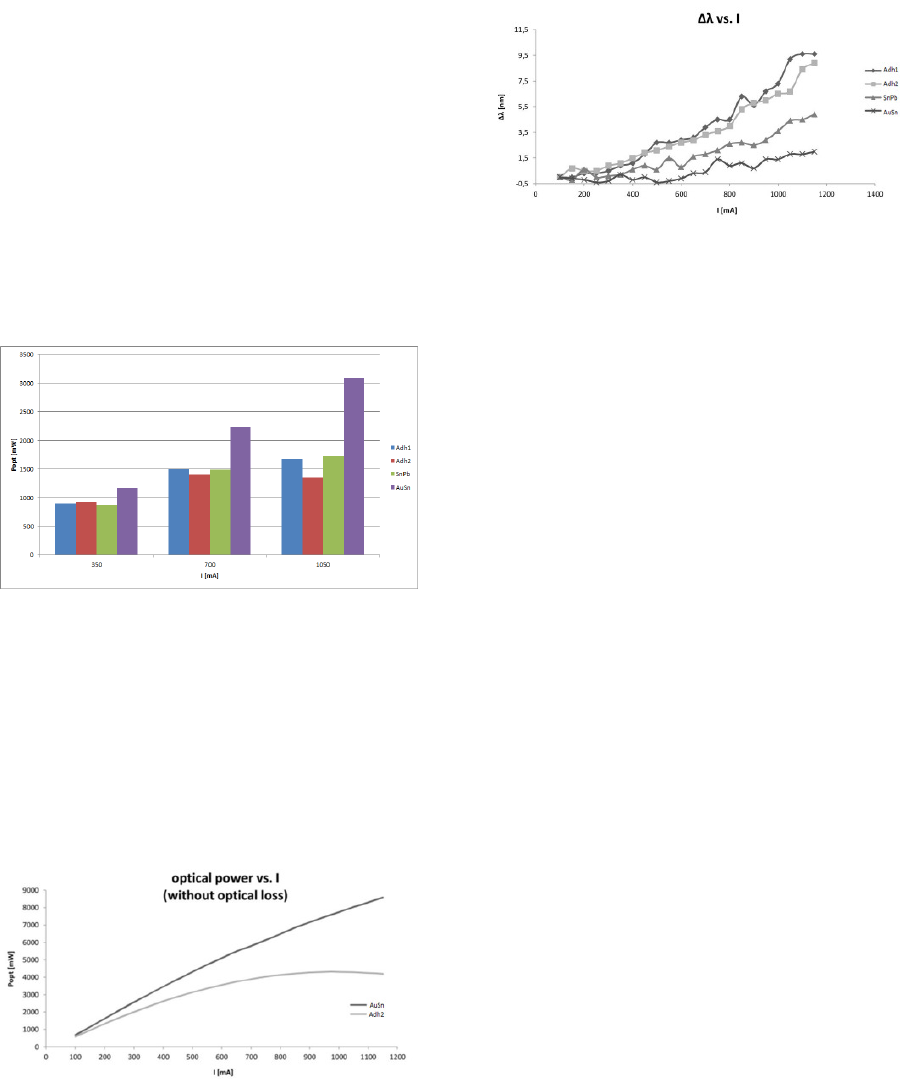

Optical Measurements

Optical power measurements and wavelength shift

are observed using an integrating sphere. A setup of

an Ulbricht sphere that allows for the mounting of

the proposed ceramics substrate attached to a heat

sink is constructed. This structure permits the oper-

ation of the LED-chips at high power ratings while

diffusing the light for an integrating measurement

of total power without concerns about the direc-

tional characteristics of the LED assembly. The de-

sign of the heat-sink and the substrate clamping

lead to approx. 30% NA-loss during measurements.

A calibration of the Ulbricht sphere with respect to

this fact is used to correct the results.

The results of optical output power of the four die-

attach variants – adhesive 1, adhesive 2, SnPb

solder, and AuSn solder – are shown in Figure 11.

Measurement has been conducted using one chan-

nel of 1×7 chips per substrate and for operational

currents of 350 mA, 700 mA and 1050 mA. A sig-

nificant improvement of output power is observed

for AuSn die-attach. Adhesive 2 shows a decrease

of output power with increased current.

Figure 11: Optical output power of one channel

(1×7 chips) for four die-attach variants.

Using both channels of 2×7 chips an optical output

power of 7.7 W is achieved at 1050 mA for AuSn

soldered assemblies. The resulting peak irradiance

is 30.8 W/cm² at the LED surface with respect to

the footprint and pitch of the attached chips. The

optimized cooling of AuSn-soldered LED-chips is

demonstrated by the increased optical output power

compared to adhesively joined LEDs (Figure 12).

Figure 12: Optical output power of both

channels (2×7 chips) for the gold-tin solder

(AuSn) and adhesive (Adh2) die-attach.

Additionally the thermally induced shift of emis-

sion wavelength can be used to compare different

die-attach technologies with respect to thermal

transfer capabilities. Better cooling corresponds to a

lower chip temperature and thus to a lower wave-

length shift. Both soldering techniques show

improved behavior compared to the adhesives

(Figure 13). Gold-tin solder layers show a lower

drift than the void-prone SnPb solder.

Figure 13: Wavelength shift over current for

four die-attach variants.

Summary and Outlook

The assembly of a UV-LED multi-chip module

using different die-attach technologies has been

demonstrated. Finite element analysis proves ac-

ceptable thermo-mechanical stresses and the reali-

zation of thermally high conductive joints using

solder alloys and new highly conductive silver-

loaded adhesives if thin layers could be processed.

The design of a multi-chip sub-module is flexible

and versatile to use. Line-shaped light sources are

possible by stackable modules. A six-module

assembly is demonstrated. Easy scaling of optical

output power as well as a simplified servicing by

changing single modules add to the customer

benefit. Measurements of optical output power and

low thermally induced wavelength drift as well as

analysis of solder layer structure show the

performance of thin gold-tin solder layers. A 14

chip module attains 7.7 W optical output power and

a respective peak irradiance of 30.8 W/cm². Long

term behavior and the investigation of reliability

over life time are the next steps to confirm the

usability of the proposed module design and die-

attach technologies.

Acknowledgements

The work presented in this paper was funded by the

TAB (Thüringer Aufbaubank) with funds provided

through EFRE (Europäische Fonds für regionale

Entwicklung) OP 2007-2013 under project FK

2009VF0003. The authors would like to thank G.

Leibeling, T. Feigl and A. Joswig for sample prepa-

ration, P. Kühmstedt for micro-tomography ana-

lysis and R. Schmidt for equipment manufacturing.

IMAPS/ACerS 8th International CICMT Conference and Exhibition (2012) | April 16-19, 2012 | Erfurt, Germany

000243

Downloaded from http://meridian.allenpress.com/imaps-conferences/article-pdf/2012/CICMT/000238/2360912/cicmt-2012-tp61.pdf by guest on 03 January 2023