Test_Flow_for_Advanced_Packages_WhitePaper_1115.pdf - 第8页

ADV ANCED P ACKAGE TEST FLOW 8 unit is controlled by the test program which r eads the die temperature and regulates the A TC behavior . The thermal chuck design has to be op timized to avoid pushing down on passives, ma…

ADVANCED PACKAGE TEST FLOW 7

When devices are built using the advanced packaging technologies with multiple

components, each with a yield Y

i

, the combined yield can be represented as:

Y

combined

= Y

substrate

* Y

interposer

* Y

die1

* Y

die2

* Y

die3

*….

In such cases, where multiple dies are added to a device, it becomes necessary to test the

partially-assembled device after each die is added to the build to reduce scrap costs. For economic

reasons, OEMs may opt to skip testing the partially assembled units, when components of very high

yield are added to the build.

Testing partially assembled devices at FT and SLT while operating at full speed brings new

challenges to test, such as handling partially assembled units with exposed die. The risks added by

testing at this stage are chipped edges, cracked die or cracked packages. To keep device temperatures

under control, active thermal control systems are connected to chiller units to maintain constant

device temperature. Additionally, partially assembled devices require electrical insulation to prevent

shorting of exposed pads and the chuck during test.

Adapting Existing Equipment for Advanced Package Test

When testing advanced packages, OSATs prefer to leverage existing assets rather than invest

in one-of-a-kind testers or material handlers (see Figure 4). For interposer testing, the incoming

requirement at test is to have the thinned 100 µm interposer wafers mounted on a 700 µm glass

carrier. This allows standard probers to handle the interposer wafer as a full thickness wafer.

Testing active dies with small pad sizes and pitch, requires probers with 1 µm accuracy and

the ability to apply up to 400 Kg of force. Thermal control of the die is achieved by adding the

optional chiller units to the prober that allow the chuck temperature to be lowered to -40°C.

Standard handlers are equipped with active thermal control (ATC) heads with each head

having its own heater / chiller unit. In more sophisticated implementations, the active thermal control

ADVANCED PACKAGE TEST FLOW 8

unit is controlled by the test program which reads the die temperature and regulates the ATC

behavior. The thermal chuck design has to be optimized to avoid pushing down on passives, making

contact with exposed pads and applying uniform pressure on the exposed dies.

Figure 4: Test Insert Points for Advanced Packages

System Level Tests are usually performed on asynchronous handlers – meaning, each site test

state is independent of the other. Asynchronous handlers allow a device that has failed a test to be

removed and placed in the output tray and a new device inserted into that test socket. In addition to

the modifications needed for device handling and ATC, SLT requires hard disk duplication -

maintaining the same BIOS version and motherboard hardware versions across all test sites. SLT

executes the complete boot sequence and therefore results in long test times (90 to 300 seconds).

Long test time mandates high parallel testing to meet throughput requirements. It is common to run

12 sites in parallel using asynchronous handlers. In these systems, each site has its own tester, which

replicates the target application. This tester could be a PC for a CPU/GPU application or a cell phone

board for an applications processor. The key to successful SLT operations lies in the design on the

test executive that controls and communicates with each individual test site, consolidates test data

files and issues commands to the handler.

ADVANCED PACKAGE TEST FLOW 9

Universal Test Flow for Advanced Packages

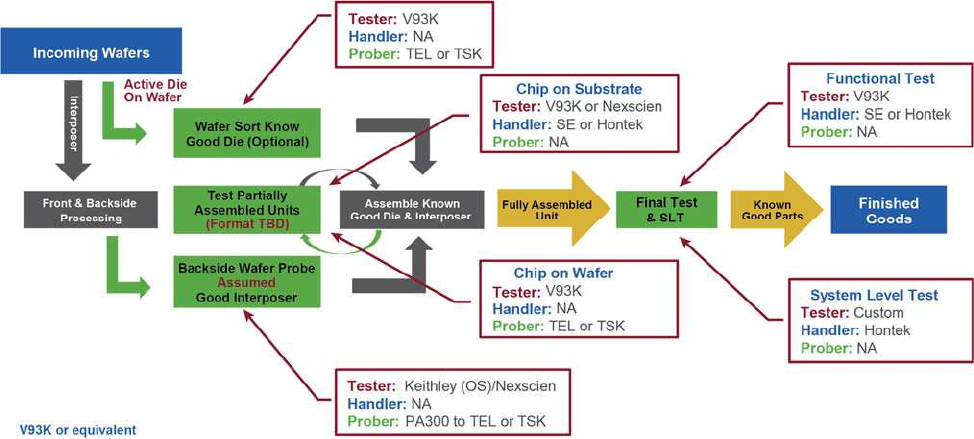

Despite the differences of the build technique employed with SLIM, 2.5D or 3D, the test

flow in Figure 5 defines the universal test flow that can be taken when building such devices. The

test stages are green boxes, while the assembly / middle end of line (MEOL) processes are shown in

black. The incoming and outgoing from the OSAT are shown in blue. The red boxes define the test

equipment used at each stage with a description of the process or test stage.

Figure 5: Test Flow for Advanced Packages

Incoming wafers have two alternate test paths: active wafers are tested as full thickness

wafers and passive interposers with test structures are tested after thinning and mounting on a glass

carrier wafer. If the interposer wafer is tested on an automated prober with a wafer loader, care must

be taken to ensure the prober recognizes the notch on the wafer for orientation. During interposer

test, only the test structures’ connectivity is verified, and if found good, all interconnects on the

interposer die are assumed good.