QLF08_LaBel.pdf - 第30页

IC and Component Selection for Space Sy stems – Presented by Kenneth A . LaBel 30 Programmatics: Development Cost • Overall product development costs are increasing: design, mask, and manufacturing – However , the percen…

IC and Component Selection for Space Systems – Presented by Kenneth A. LaBel

29

Programmatics:

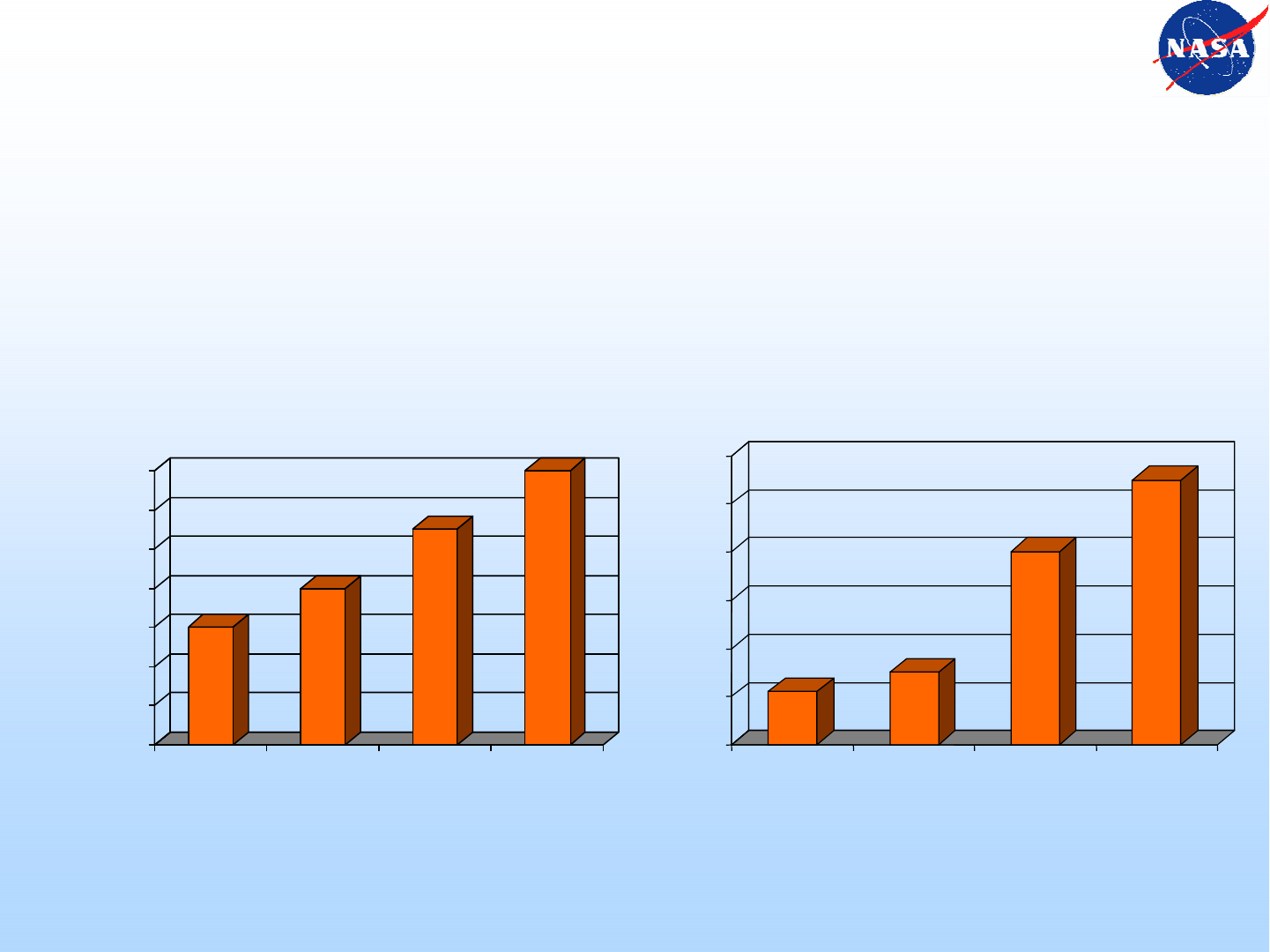

What if the first design is incorrect?

• As digital devices pack more bits into the same physical

space (i.e., technology feature size is shrinking), more

designs require a “second pass” or re-spin.

• Even worse, the time it takes for this re-spin has increased

0

1

2

3

4

5

6

7

Months

.25u .18u .13u .09u

Technology

Average Re-Spin time

Source: www.chipdesignmag.com

0

10

20

30

40

50

60

.25u .18u .13u .09u

Technology

Percent of designs requiring re-spin

IC and Component Selection for Space Systems – Presented by Kenneth A. LaBel

30

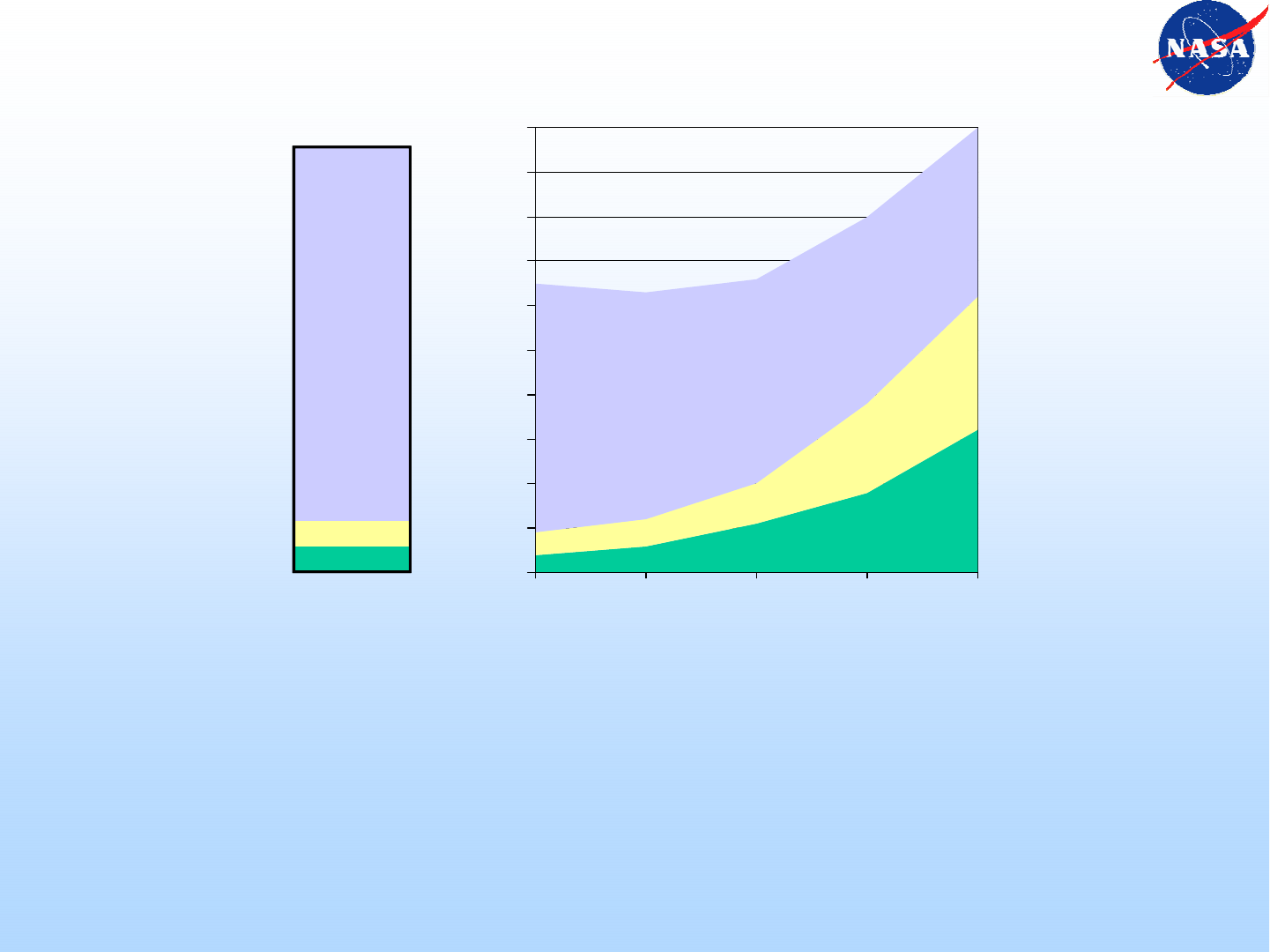

Programmatics: Development Cost

• Overall product development costs are increasing: design, mask, and

manufacturing

– However, the percentage of product cost for both design and masks (>$1M for

90nm!) are also Increasing

• Implies cost effectiveness of minimizing masks and design re-spin costs (advantage

FPGAs and SAs)

Graphic from MIPS Technologies "The Coming Reality for SOC Designers" by John Bourgoin

Design

Costs

Mask

Costs

Mfg.

Costs

$0M

$1M

$2M

$3M

$4M

$5M

$6M

$7M

$8M

$9M

$10M

1995

(0.35um)

1997

(0.25um)

1999

(0.18um)

2001

(0.13um)

2003

(0.10um)

Assumptions: 6M-70M transistors, 3 mask spins, 250K Units, transistor costs and productivity projected from the ITRS

Design

100%

Mfg.

(250KU)

62%

Masks

Design

100%

Masks

Mfg.

(250KU)

1995

13%

IC and Component Selection for Space Systems – Presented by Kenneth A. LaBel

31

Selection Criteria: Radiation and Reliability

• While there is no “generic” answer for radiation

tolerance and reliability levels in the trade, there

are numerous considerations such as

– What is known of the process radiation tolerance?

• Was process/device radiation qualification sufficient for

planned design or application?

– Library? Cells? Speed? Etc…

• Is the process reliable and achieving good yield?

– High-volume commercial fab vs. low-volume niche fab?

• Are there lot-specific or application-specific concerns?

– Is there a specific performance requirement such as

reconfigurability or ultra-low power that forces a non-

radiation tolerant device selection?

• How does a fault-tolerant system architecture enter the

equation?

– How testable is the design/device?

• As has become more evident, trade spaces are

much more complex than “just” an IC