IPC-4556 印制板化学镍钯浸金(ENEPIG)规范ENG.pdf - 第84页

This Page Intentionally Left Blank IPC-4556 January 2013 74

SUMMARY

The electroless Ni, electroless Pd, and immersion Au (ENEPIG) surface finish is capturing the attention of both the struc-

tural and electronics soldering communities as a means to enhance the solderability of common base materials for a range

of applications. Solderability testing has illustrated the robustness of this finish after simulated storage aging using the

Battelle Class 2 environment. For the various ENEPIG finishes in this study, the excellent performance was sensitive to sup-

plier but not to the thickness of the Pd layer. Only a slight decrease in wetting rate was observed after exposure to the

Battelle Class 2 conditions. Auger electron spectroscopy (AES) identified two possible sources of the reduced wetting rate:

(a) Pd diffusion to the Au surface and its oxidation and (b) the small build-up of carbon compounds that are attracted to the

Au layer.

REFERENCES

1. G. Milad, Is ‘‘Black Pad’’ Still an Issue for ENIG?’’ Circuit World, Vol. 36 Iss: 1, pp.10 - 13, 2010.

2. W. H. Abbott, ‘‘The Development and Performance Characteristics of Mixed Flowing Gas Test Environment,’’ IEEE

Transactions, Vol. 11, No. 1, March 1988.

3. A. Jackson, I. Artaki, and P.Vianco, ‘‘Manufacturing Feasibility of Several Lead Free Solders for Electronic Assembly,’’

Proc. 7

t

h Inter. SAMPE Electronics Conf. (Parsippany, NJ; June 21, 1994), p. 381.

4. I. Artaki, A. Jackson, and P. Vianco, ‘‘Fine Pitch Surface Mount Assembly with Lead-Free, Low Residue Solder Paste,’’

Proc. Surface Mount Inter., (San Jose, CA Aug. 28, 1994), p. 495.

5. P. Vianco, J. Rejent, I. Artaki, and U. Ray, ‘‘An Evaluation of Prototype Circuit Boards Assembled with a Sn-Ag-Bi Sol-

der,’’ Proc. IPC Works ’99 (IPC, Northbrook, IL; 1999), p. S-03-3-1.

6. P. Vianco and A. Claghorn, ‘‘Effect of Substrate Preheating on Solderability Performance as a Guideline for Assembly

Development - Part I: Baseline Analysis,’’ Soldering and Surface Mount Technology No. 24 (1996) p. 12.

7. R. J. K. Wassink, Soldering Electronics, (Ayr, Scotland: Electrochemical Publications Limited, 1984) p. 235.

January 2013 IPC-4556

73

This Page Intentionally Left Blank

IPC-4556 January 2013

74

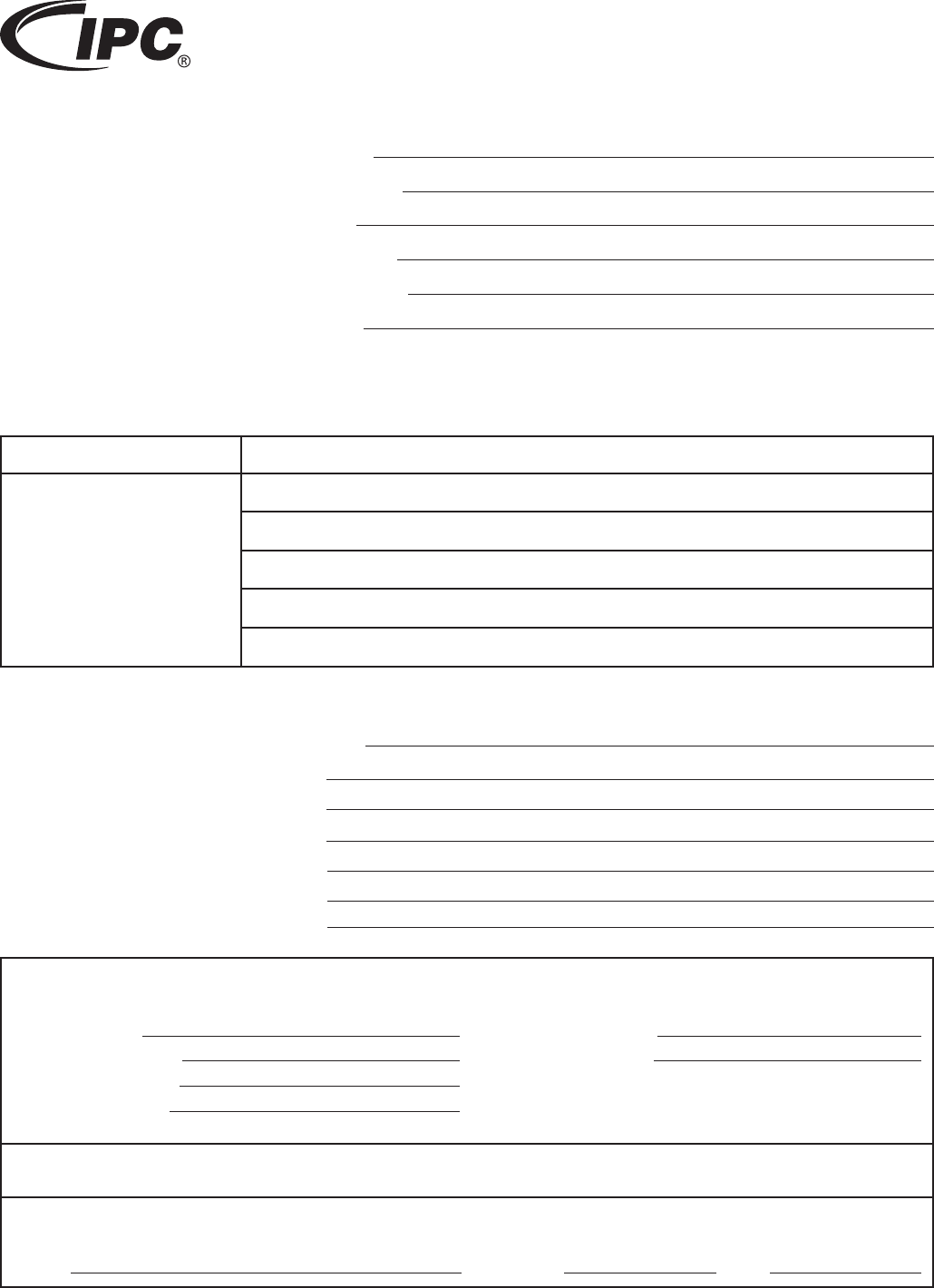

ANSI/IPC-T-50 Terms and Definitions for

Interconnecting and Packaging Electronic Circuits

Definition Submission/Approval Sheet

The purpose of this form is to keep

current with terms routinely used in

the industry and their definitions.

Individuals or companies are

invited to comment. Please

complete this form and return to:

IPC

3000 Lakeside Drive, Suite 309S

Bannockburn, IL 60015-1249

Fax: 847 615.7105

SUBMITTOR INFORMATION:

Name:

Company:

City:

State/Zip:

Telephone:

Date:

❑ This is a NEW term and definition being submitted.

❑ This is an ADDITION to an existing term and definition(s).

❑ This is a CHANGE to an existing definition.

Term Definition

If space not adequate, use reverse side or attach additional sheet(s).

Artwork: ❑ Not Applicable ❑ Required ❑ To be supplied

❑ Included: Electronic File Name:

Document(s) to which this term applies:

Committees affected by this term:

Office Use

IPC Office Committee 2-30

Date Received:

Comments Collated:

Returned for Action:

Revision Inclusion:

Date of Initial Review:

Comment Resolution:

Committee Action: ❑ Accepted ❑ Rejected

❑ Accept Modify

IEC Classification

Classification Code • Serial Number

Terms and Definition Committee Final Approval Authorization:

Committee 2-30 has approved the above term for release in the next revision.

Name:

Committee: Date:

IPC 2-30