00193790-01.pdf - 第44页

1 Deutsch I nstallation und Erste Schri tte mit CACCIA SIPLACE 1.10 Übersicht der J umpereinstellungen der einzelnen Subs ysteme Ausgabe 07/2004 45 ACHTUNG Bei Kopf-Mo dularität ist dar auf zu achten, das s der CAN-Ab sc…

Installation und Erste Schritte mit CACCIA SIPLACE 1 Deutsch

Ausgabe 07/2004 1.10 Übersicht der Jumpereinstellungen der einzelnen Subsysteme

44

1.10 Übersicht der Jumpereinstellungen der einzelnen

Subsysteme

1.10.1 SIPLACE HF3: Portal

1.10.1.1 DIP Schalter am Kopfinterface

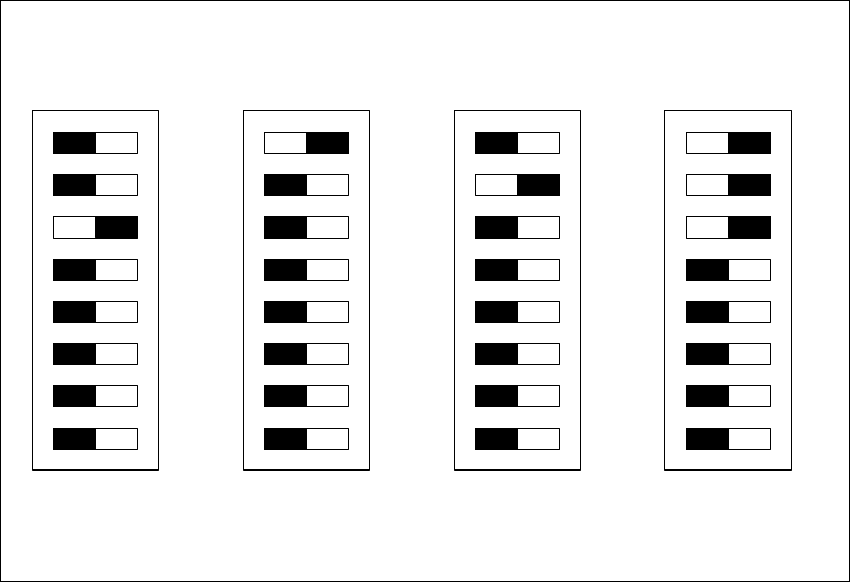

Abb. 1 - 33 DIP Schalter am Kopfinterface

Legende

(1) P0 - Adress-Schalter 1 → Portal

(2) P1 - Adress-Schalter 2 → Portal

(3) CAN R - Schalter Abschlusswiderstand CAN Bus (für Twin-Option immer OFF)

(4) Boot - CAN-Prozessor 16 Bit nicht installiert

(5) Reset - CAN-Prozessor 16 Bit nicht installiert

(6) C0 - Adressen Schalter CAN-Bus

(7) C1 - Adressen Schalter CAN-Bus

(8) WPE - Schreibschutz aktiviert z.Z ausgeschaltet (Write protect enable)

DIP Schalter

ON

78123456

ON

78123456

ON

78123456

ON

78123456

Portal 1

Portal 2

nicht benutzt

Portal 3 Portal 4

C&P Kopf

C&P Kopf

Twin-Kopf

1 Deutsch Installation und Erste Schritte mit CACCIA SIPLACE

1.10 Übersicht der Jumpereinstellungen der einzelnen Subsysteme Ausgabe 07/2004

45

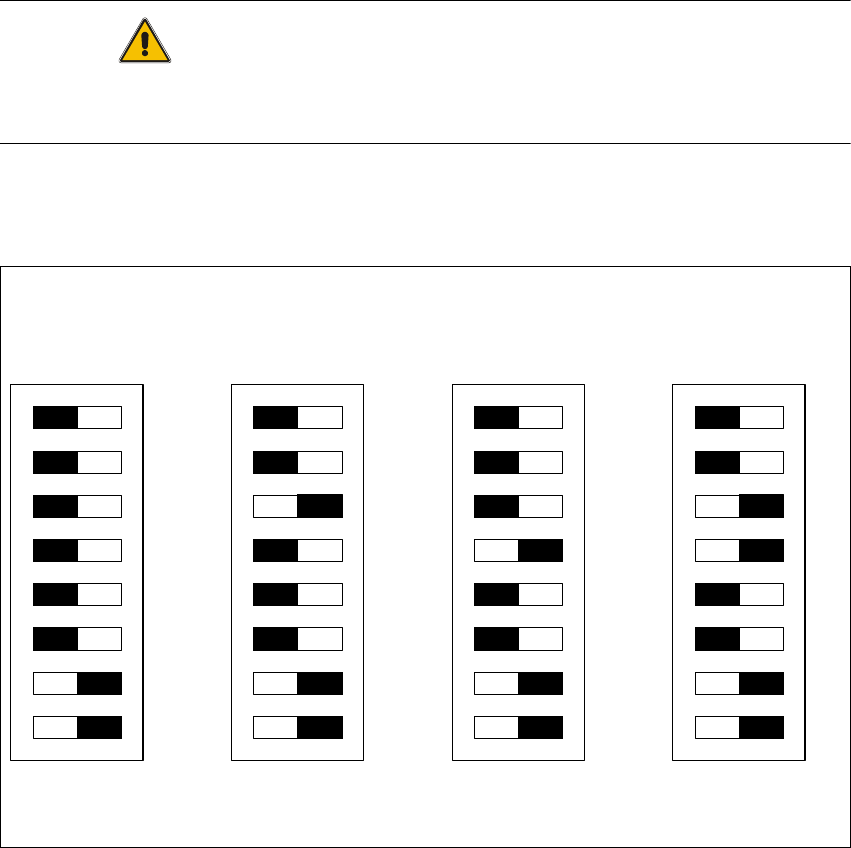

ACHTUNG

Bei Kopf-Modularität ist darauf zu achten, dass der CAN-Abschlusswiderstand richtig gesetzt

wird. D.h. bei C&P Köpfen auf ON, bei Twin-Kopf auf OFF.

1.10.1.2 DIP-Schalter am Visionboard

Abb. 1 - 34 DIP-Schalter am Visionboard

Legende

(1) Boot - CAN-Prozessor 16 Bit auf Sub board

(2) Reset - CAN-Prozessor 16 Bit auf Sub board

(3) P0 - Adress-Schalter 1 → Portal

(4) P1 - Adress-Schalter 2 → Portal

(5) WPE - Write protect enable z.Z ausgeschaltet

(6) CAN R - Schalter Abschlusswiderstand CAN-Bus

(7) Test 1 - CAN 1MBit/s → ON

(8) Test 0 - CAN group → ON

DIP Schalter

ON

78123456

ON

78123456

ON

78123456

ON

78123456

Portal 1

Portal 2

nicht benutzt

Portal 3 Portal 4

Installation und Erste Schritte mit CACCIA SIPLACE 1 Deutsch

Ausgabe 07/2004 1.10 Übersicht der Jumpereinstellungen der einzelnen Subsysteme

46

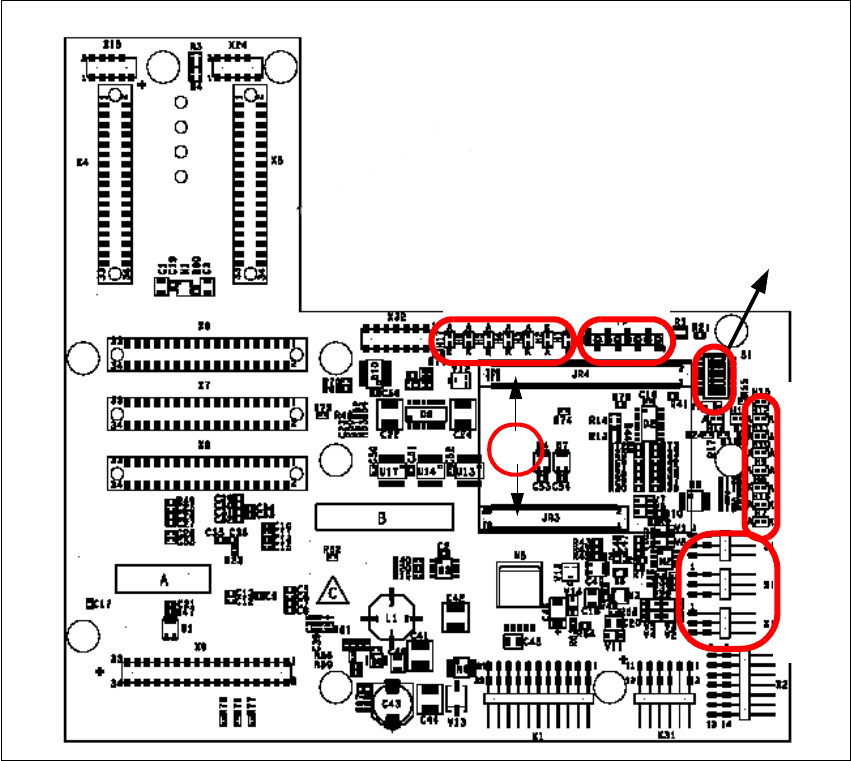

1.10.2 SIPLACE HF3: Schalterstellungen an den Leiterplatten am C&P Kopf

1.10.2.1 Kopfinterface

Es wird die gleiche Kopfinterface-Platine am Portal 1 und Portal 2 benutzt, unabhängig von der

Twin-Kopf und C&P-Kopf Konfiguration an diesen Portalen.

Abb. 1 - 35 (Head) Kopfinterface

Legende:

(1) X11 Stecker Temperatursensor X-Achse

(2) X17 Stecker BERO Verfahrbereich X-Achse

(3) X16 Stecker BERO Verfahrbereich X-Achse

(4) X15 Stecker für Inkrementalgeber (-encoder) X-Achse

(5) X24 Teststecker digitale Spursignale X-Achse

(6) Steckplatz für "One Wire" Prozessorboard

LED 1-7 TP 1-8

LED 1-10

DIP Schalter

1

2

3

4

5

6