IPC-JEDEC-9704A CHINESE.pdf - 第10页

• 连接器安装 • 元器件安装 2. 印制板 测试 过 程 • 在 线 测试( ICT ) 或等效 的 “ 短 路和开路 ” 测试 • 印制板 功 能测试( BFT ) 或等效 的 功 能测试 3. 机械 组装 • 散热 片 组装 • 印制板 的支 撑物 / 增 强 板 组装 • 系统印制板集 成 或系统 组装 • PCI ( 外设部 件 互 连) 或 者 子 板 安装 • 双 列 直 插内 存 模块 ( DIMM )安装 4. 运 输…

制板应变测试指南

1 范围

本文件旨在用来作为应变片布局和后续使用应变片对印制电路组件(PCAs)进行测试的一种方法。

该方法对印制板制造过程中PCAs的应变测试制定了详细的指南,这些制造过程包括组装、测试、系

统集成以及其他可能导致印制板弯曲的操作方式。

本文件建议的程序使印制板组装厂能够独立进行所要求的应变测试,并为印制板翘曲测量和风险等

级评估提供了量化的方法。

本文件所涵盖的主题包括:

• 测试设置和仪器要求

•应变测量

• 报告格式

本文件假定该方法是用来测试表面贴装器件的,如球栅阵列(BGA)、小外形封装(SOP)、芯片尺

寸封装(CSP)和面阵列表面贴装(SMT)连接器/插座。在某些情况下,所述的测试方法可用于非

面阵列分立式SMT 器件,如电容或电阻。

1.1 ⽬的 应变测试可以对SMT封装在PCA组装、测试和操作中受到的应变和应变率水平进行客观

分析。

由于元器件焊点对应变失效非常敏感,因此PCA在最恶劣条件下的应变特性显得至关重要。对于不

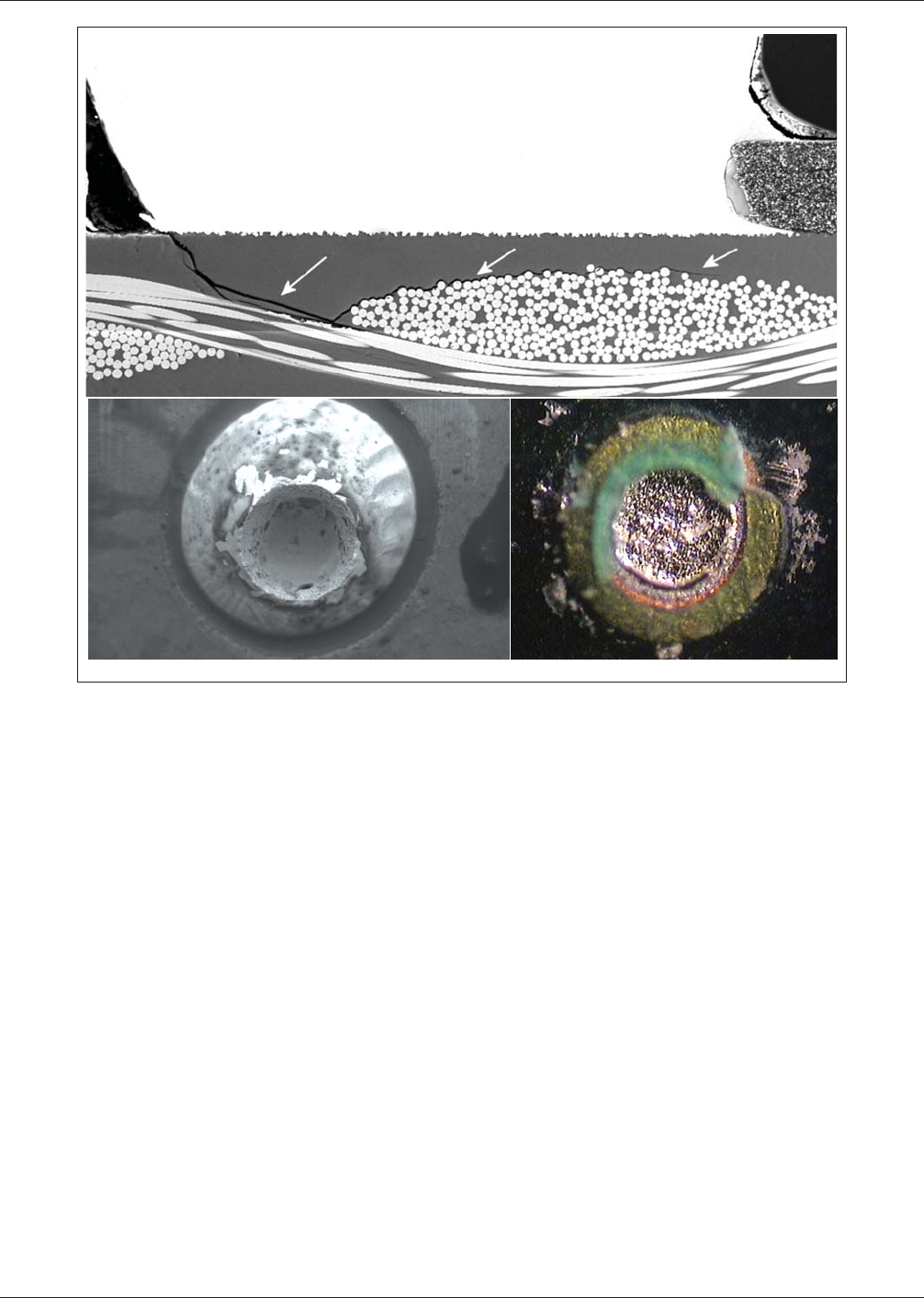

同的焊料合金、封装类型、表面处理或层压板材料,过大的应变都会导致各种模式的失效。这些失

效包括焊料球开裂、线路损伤、层压板相关的粘合失效(焊盘翘起)或内聚失效(承垫坑裂)和封

装基板开裂(见图1-1)。

1.2 背景 经证实,运用应变测量来控制印制板翘曲对电子工业是有利的,而且其做为一种识别和

改进生产操作(有造成互连损伤的高风险)的方法也被逐渐地认可。然而,随着向无铅组装技术的

快速过渡,互连密度的增加,以及新的层压板材料,翘曲导致损伤的可能性也在增大。

随着应变测量技术的成熟,不同的方法应运而生。应变测量方法的差异阻碍了可靠数据的采集及行

业间的数据对比。本文件对应变片粘附、应变片位置、实验设计、数据采集系统参数和应变度量体

系中的差异进行了讨论。

PCA应变测量包括把应变片贴在印制板上指定的元器件附近,随后使装有应变片的印制板经受不同

的测试、

组装以及人工操作。超出应变极限的步骤被视为应变过大,并进行确认以便采取纠正措施。

应变极限可以来自客户、元器件供应商或者企业/行业内部众所周知的惯例。应变测量标准的范例见

白皮书www.ipc.org/IPC-WP-011。

通过对制造变异敏感区域的鉴别,应变测试为产量的提升指明了方向。应变测量成为未来工艺改进

的基准,并可对调整的效果进行量化。需要进行应变测量的典型制造步骤如下:

1.

SMT组装制程

•分板(裁板)制程

• 所有人工操作制程

• 所有返工和修补制程

2012年2月 IPC/JEDEC-9704A

1

• 连接器安装

• 元器件安装

2. 印制板测试过程

• 在线测试(ICT)或等效的“短路和开路”测试

• 印制板功能测试(BFT)或等效的功能测试

3. 机械组装

• 散热片组装

• 印制板的支撑物/增强板组装

• 系统印制板集成或系统组装

• PCI(外设部件互连)或者子板安装

• 双列直插内存模块(DIMM)安装

4. 运输及处理

组装流程因印制板和组装厂的不同而异。本文件中,ICT和BFT等统称为测试。不同的工厂可能会有

不同的专业术语命名系统。因此,要对等效的测试过程采用相同的要求。总之,应变测量的目标是

描述所有涉及机械荷载的组装步骤的特性。不要将测试局限于以上所列的步骤,或者仅应用于已知

的高风险区域。通过这些测试得到的数据可作为将来参考的基准。

IPC-9704a-1-01-cn

图1-1 焊点损坏实例(顶部图:承垫坑裂,左下图:焊点本体失效,右下图:焊接界⾯断裂)

焊料球

坑裂

IPC/JEDEC-9704A 2012年2月

2

1.3 术语及定义 本文件所使用的所有术语的定义都 应当符合IPC-T-50及以下定义。

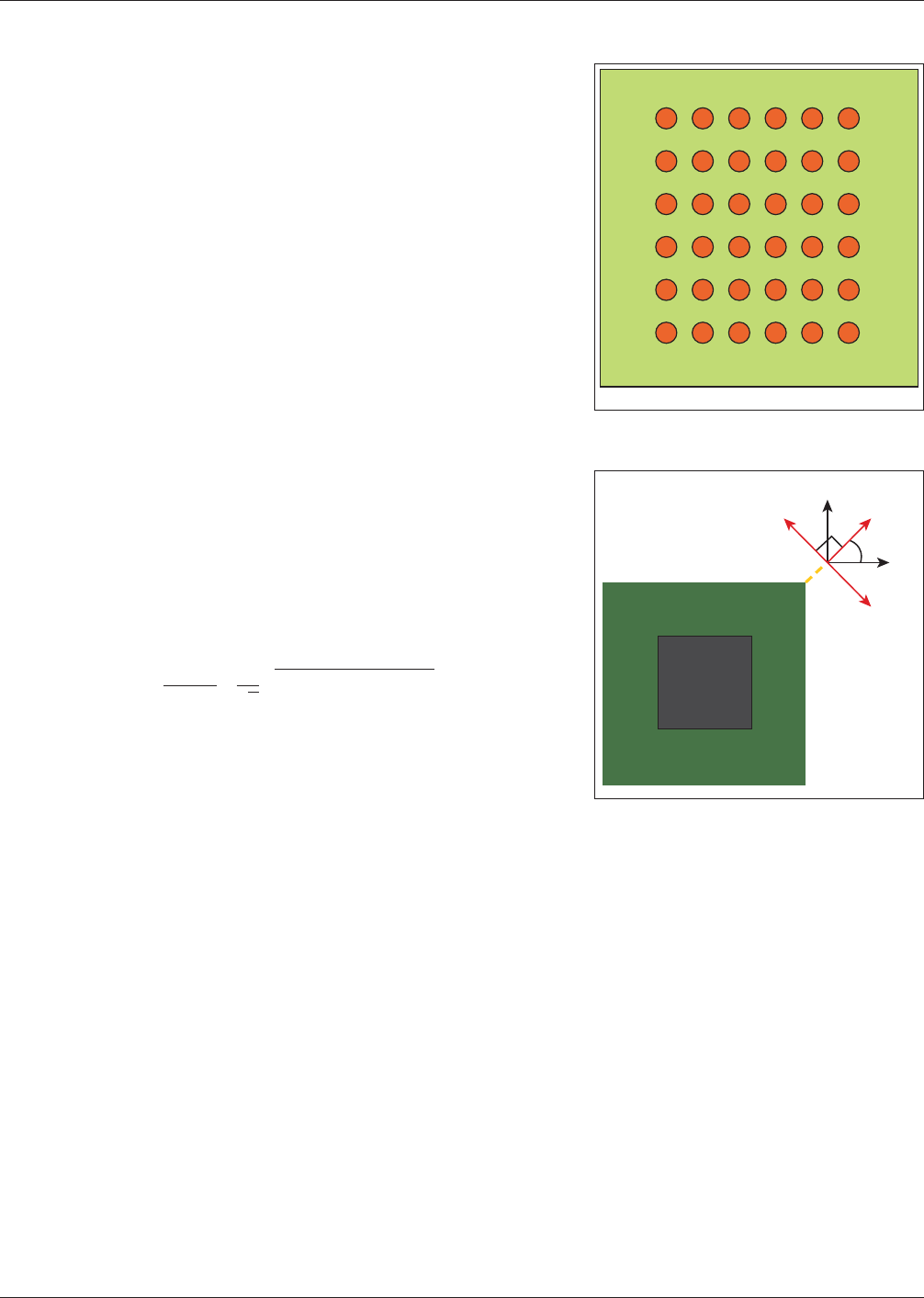

1.3.1 ⾯阵列元器件 端子以栅格形式排列于封装底部且包含

在其外形内的元器件(见图1-2)。

1.3.2 元器件 任何贴装在印制电路板上的器件或机械互连结

构。

1.3.3 互连 用于电气互连的导电要素,比如:焊料球、引线

等。

1.3.4 ⾮⾯阵列元器件 端子排列于封装外围的有引线或无引

线元器件,包括有端帽端子的元器件,如片式电容或电阻。

1.3.5 对⾓线应变(ε

d

) 与应变片e

2

成一直线或正交的定向应

变,其值取e

2

和e

4

(e

4

= e

1

+ e

3

-e

2

)中的较大者:

ε

d

= Max (|e

2

|,|e

1

+e

3

-e

2

|)

如图1-3所示

1.3.6 微应变 无量纲单位,10

6

×(长度变化)÷(原始长

度)。

1.3.7 主应变 一个平面中最大和最小的正交应变,互相垂直

且所在方向上的切应变为零。

e

p

=

e

1

+ e

3

2

±

1

√

2

√

(e

1

- e

2

)

2

+(e

2

- e

3

)

2

1.3.8 应变花 含有2个或以上独立敏感栅的应变片,这些敏

感栅用来测量一个公共点处沿他们各自轴向上的应变。

1.3.9 承垫坑裂 在粘合的电介质层形成的裂纹或是在表面贴

装元器件的焊盘下面发生的断裂。

1.3.10 堆叠花形应变⽚ 由相互堆叠于一个公共点的敏感栅

构成的花形应变片。

1.3.11 应变 无量纲单位,(长度变化)÷(原始长度)。

1.3.12 应变指导 选择的应变度量标准的大小极限。

1.3.13 应变度量标准 被选做临界测量判据的规定应变参数。对角线应变和主应变是两种合适的应

变度量标准。

1.3.14 应变率 应变的变化量除以这个变化被测量到的时间间隔。

1.3.15 应变⽚ 粘附于基底的平面金属膜图案,在受到应变时其电阻值会发生变化。

1.3.16 应变⽚单元 由蛇形金属敏感栅图案构成的应变片敏感区域。

1.4 修订版本变化 被纳入此标准当前修订版的变更部分用灰色阴影来标注。图片和表格的变更则

用灰色阴影标注其标题。以下章节已经在本文件的修订中被删除:

IPC-9704a-1-02-cn

图1-2 ⾯阵列元器件

IPC-9704a-1-03-cn

图1-3 对⾓线应变度量是e

2

或e

4

的最⼤

值,⽆论相对于元器件来说沿着这两个⽅

向是哪个应变较⼤。

H

H

H

H

H

2012年2月 IPC/JEDEC-9704A

3