IPC-JEDEC-9704A CHINESE.pdf - 第29页

附录 B 术语表 ASTM 美 国 材 料与测试学会 AW G 美 国 线规 BGA 球栅阵 列 BFT 板 功 能测试 CSP 芯片尺寸 封装 CTE 热膨胀 系 数 CAD 计算机 辅 助 设 计 DIMM 双 列 直 插内 存 模块 EIG 化 学 镀镍 / 浸 金 EBGA 增 强 型球栅阵 列 FEA 有限元 分析 FCBGA 倒 装 芯片球栅阵 列 HASL 热 风焊 料 整 平 ICT 在 线 测试 JEDEC 电子器件…

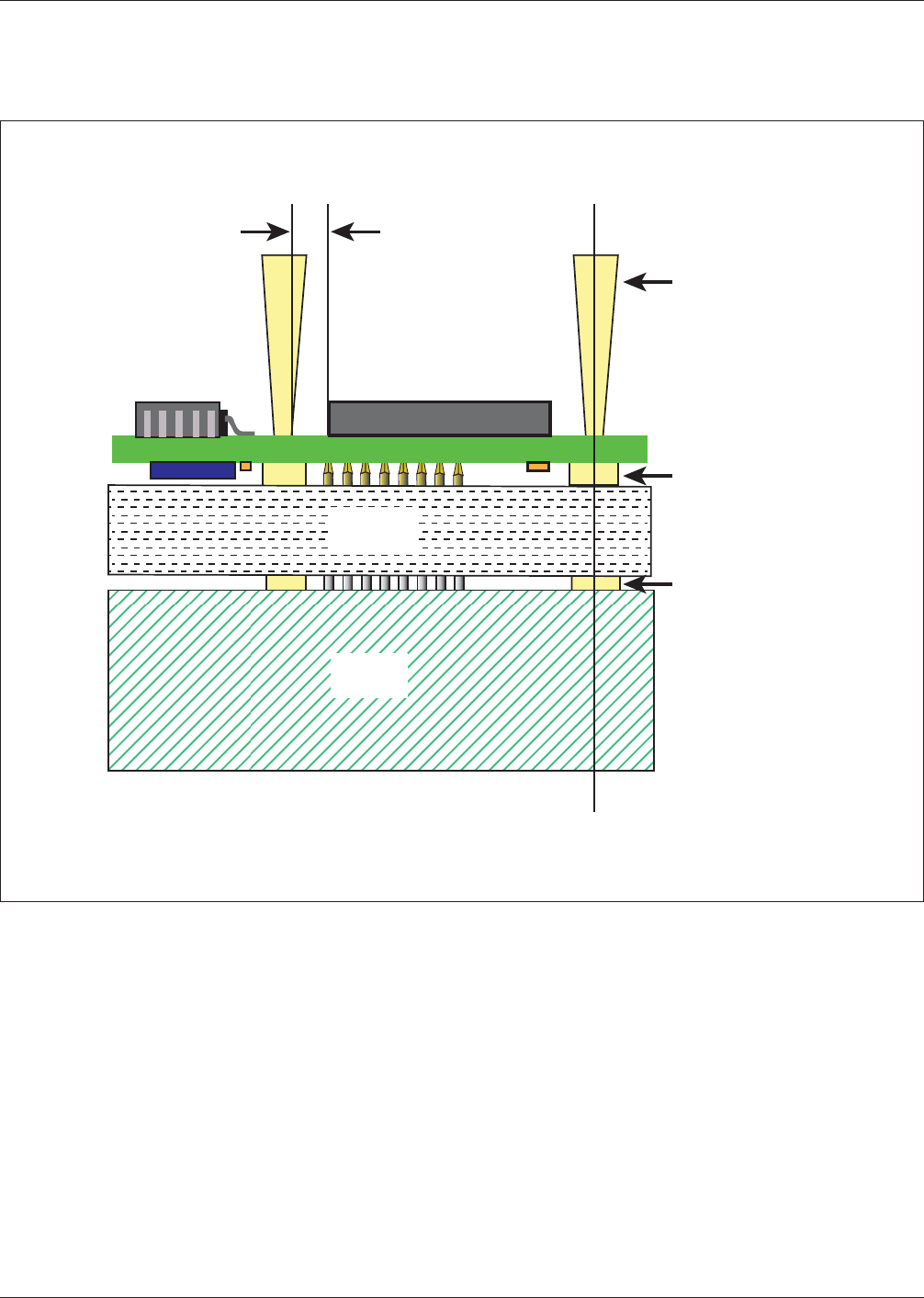

只要有可能,应尽可能把顶部和底部印制板支撑柱放置在一条近似的直线上,使材料之间层叠稳

固,从而进一步减少在UUT上的应变。当放置印制板支撑柱时,建议印制板支撑柱与元器件边沿之

间保持1.3mm的间隙。见图A-3。此外,在有大量探针的PTH连接器上放置支撑块是允许的。

应变花应该按供应商的规范放置在有需要的UUT上。如果可能,使用有限元分析作为每个应变花的

放置位置和预计应变范围的指南。

如果引线放置在印制板支撑柱下面,其可能会受损,而且测试结果也可能波动很大。为了正确地放

置应变花和导线,建议参照测试治具中印制板支撑柱的清晰布局图。如有必要,可以移除需要放置

应变花位置下面或附近的较小元器件(电容和电阻)。同样,如有必要,为了导线引线的布局,较小

元器件可以在不影响应变测试结果的情况被移除。

IPC-9704a-a-03-cn

图A-3 元器件与⽀撑柱的间隙和正确的⽀撑柱对位图解

1.3mm[0.050in]

顶部支撑柱与元器件边沿之间间隔1.3mm[0.50in]

顶板

针板

保持印制板支撑柱在一条直线上以减少UUT上的应变

顶部印制板支撑柱

底部印制板支撑柱

止动停止

IPC/JEDEC-9704A 2012年2月

20

附录 B

术语表

ASTM 美国材料与测试学会

AWG 美国线规

BGA 球栅阵列

BFT 板功能测试

CSP 芯片尺寸封装

CTE 热膨胀系数

CAD 计算机辅助设计

DIMM 双列直插内存模块

EIG 化学镀镍/浸金

EBGA 增强型球栅阵列

FEA 有限元分析

FCBGA 倒装芯片球栅阵列

HASL 热风焊料整平

ICT 在线测试

JEDEC 电子器件工程联合理事会

PCI 外设部件互连

PVC 聚氯乙烯

PM 预防维护

PWB 印制线路板

PWBA 印制线路板组装

SOP 小外型封装

SMT 表面贴装技术

TBGA 载带球栅阵列

UUT 被测单元

2012年2月 IPC/JEDEC-9704A

21

此页留作空白

IPC/JEDEC-9704A 2012年2月

22