IPC-JEDEC-9704A CHINESE.pdf - 第15页

9704a-3-04-cn 图 3 - 4 既有 SMT 元器件⼜有通孔元器件的印制板(波峰焊后) 导线 捆扎 和 固 定 应变片 位 置 9705a-3-05-cn 图 3 - 5 ICT 治具应变测试设置 捆扎 和 固 定导线 并 避 开下 压柱 2012 年 2 月 IPC / JEDEC - 9704A 7

以上是最低要求。系统组装制程的特征描述可能要求准备另外的测试板。如果被测器件的变形达到

了有可能已发生损坏的点,则应该对该系统进行评估,以确保使用此测试板仍可得到准确的数据。

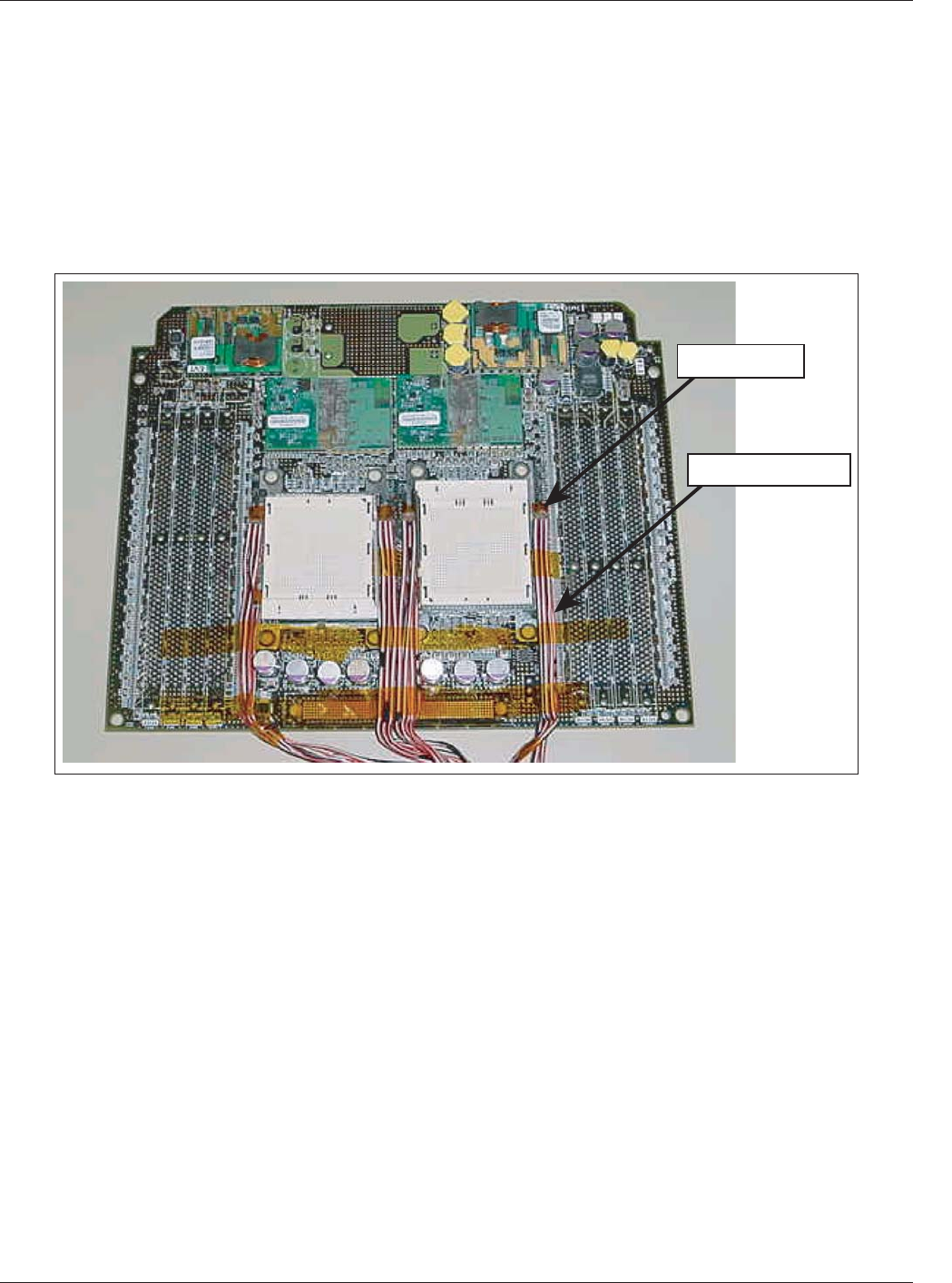

第一块装有应变片的印制板应该代表 已通 过SMT再(回)流焊,未 进行波峰焊的印制电路组

件(PCA)。图3-3给出了实例图。在这个阶段,板上只装有SMT元器件。正如图3-3所示,合理的布

线对于这些印制板非常重要。当准备测试板时,用耐热胶带或扎线带捆扎和固定导线很重要。导线

应该布置于元器件之间,避免与任何制程步骤发生干涉。

其目的在于对人工操作、连接器和其他通孔元器件插装、以及任何波峰焊前进行的电气测试过程中

的应变/应变率进行特征描述。此板不应该再用于波峰焊后组装步骤的特征描述。

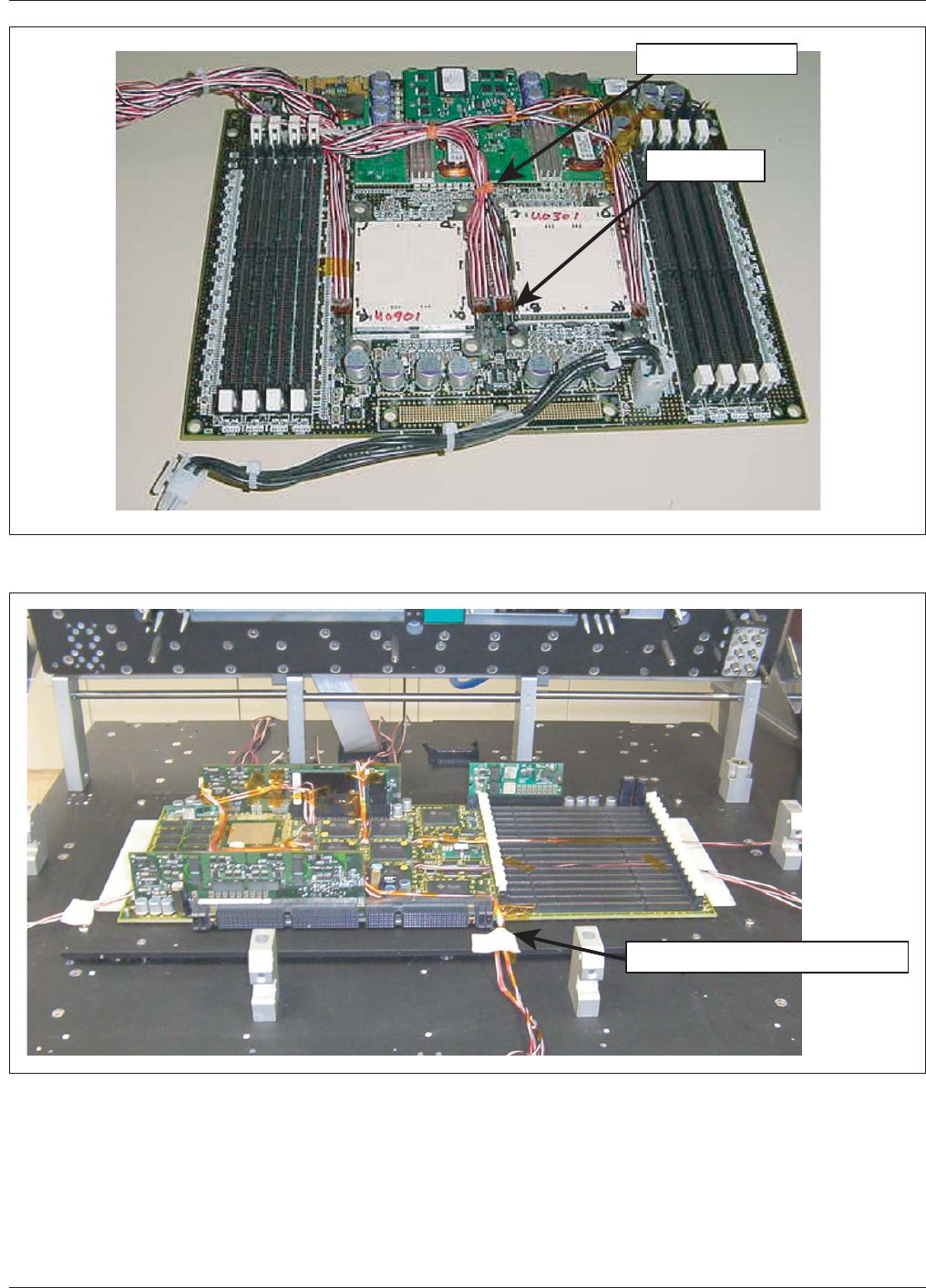

第二块装有应变片的印制板应该与完成波峰焊后的PCAs相似。图3-4给出了实例图。正如前面的印

制板一样(图3-3),应该遵循合理的布线。此板装有所

有SMT及通孔元器件,用来描述最终的再

(回)流焊后的以下所有组装步骤(如适用)的特征:

•分板/裁板

•印制板的支撑物/加固物组装

•最终系统组装

• PCI卡插入

• DIMM模块插入

• 子板插入

• 散热片连接

• 测试操作(ICT、BFT)

• BGA及通孔元器件的返工

虽然ICT和BFT是典型的高应变/应变率操作,任何其他步骤也有可能造成损伤。图3-5图示了一个典

型的ICT应变测试设置。

9704a-3-03-cn

图3-3 只有SMT元器件的印制板(SMT再(回)流焊后)

ᓄਈ⡷ս㖞

ሬ㓯઼പᇊ

IPC/JEDEC-9704A 2012年2月

6

9704a-3-04-cn

图3-4 既有SMT元器件⼜有通孔元器件的印制板(波峰焊后)

导线捆扎和固定

应变片位置

9705a-3-05-cn

图3-5 ICT治具应变测试设置

捆扎和固定导线并避开下压柱

2012年2月 IPC/JEDEC-9704A

7

应该描述所有组装步骤的特征。还应该重视使用机械治具的步骤,例如支撑治具、压合治具、锁螺

丝治具等。如用货架或托盘,也应该考虑比如存储和印制板转运等步骤。

强烈建议无论是否有治具,对组装步骤之间的任何人工操作都要进行特征描述。如果人工操作步骤

类似,可以将对这些操作的多个测试合并为一个对能代表最差情况操作的测试,这样是可接受的。

必须在测试报告中记录此人工操作模拟的详细信息。

模拟还应该被用于量化相关的变异性。一些独特的生产制程可能会要求不同的布局。例如通孔元器

件通常要求波峰焊。波峰焊照惯例是在对流再(回)流焊后(一次还是两次取决于印制板的布局)

进行。然而,印制板可能在SMT再(回)流焊前就已经手工插入电感线圈且不要求波峰焊。在要求

对SMT再(回)流焊前的组装进行特征描述的情况下,测试板在机械结构上必须能够代表SMT再

(回)流焊前的印制板。

在这种情况下,只要所有机械荷载的特征描述要求都能满足,使用不同的设置是可接受的。但印制

板上必须有以下的元器件:

• 大物理尺寸和/或大质量的元器件。

• 对印制板有机械约束的元器件,例如汇流条、长连接器等。

将应变片粘附到印制板上之前,建议先检验测试板是否存在过度的翘曲。另外可能还要考虑到焊料

老化的影响,也就是装有应变片的测试板上的焊点应该会比成品板的老化时间长。在解释结果时应

该考虑到这点。

3.2 元器件和器件 供应商和用户应当在需粘贴应变片并测试的元器件上达成统一。3.2.1和3.2.2列

出了应变测试的推荐规范。

3.2.1 ⾯阵列元器件 建议对任何封装尺寸大于或等于27x27

mm的面阵列器件或者尺寸 >10 mm的细

节距元器件(0.8mm节距及以下)进行评估。 如果有多 个细节距元器件,那么应该根据工程学判

断、损伤历史或者有限元分析,来测试至少三个最差情况的位置。

上述的其中一种方法可以作为特征描述的准则。其他确定应变片放置位置的准则包括:观察到的失

效位置、历史的失效率、有限元分析、组装/测试治具的结构、板的设计和BGA的封装设计。板和封

装设计需考虑的因素包括几何外形、材料和结构。失效位置可采用染色(Dykem®或类似的产品)渗

透和元件移除技术(染色实验)来确定。

如果板上有大量的BGA元器件(也就是6个或以上),可以先依靠一个有限元分析(FEA)模型,或

其他分析和计算方法来预测应变片最佳放置位置。然而,如果初次测试就确定了高应变区域,就要

对此区域进行更多的关注。*注意:在应用这些方法时,一定要认识到任何人不可能把所有装载作业

中所有位置上的所有机械荷载都完全搞清楚。在任何情况下,除非受到空间限制,否则封装的四个

角都要粘贴应变片。

对于CPU插座来说,应变片应该放置于靠近BGA的拐角焊点处,以便三轴应变片的正交栅格与焊点

的行/列平行。插座设计的不同使得应变片的放置不可能完全一致。一般而言,应变片会放置在距

BGA拐角焊点处6mm - 10mm之间。当测量值是直接与客户和供应商指定的应变指南值比较时,应变

片应该只能放置于其指定的位置和方向上。

3.2.2 ⾮⾯阵列元器件 焊点较小、本体较硬的非面阵列元件(例如,多层陶瓷电容(MLCC))的

互连也容易受到应变的影响而导致焊点失效。通过评估这些制程中产生的应变,并确保其在可接受

范围内,能够明显的减少/消除诸如焊点开裂、器件断裂、焊盘起翘、承垫坑裂和印制板导体损伤之

类的失效的发生。更多的信息见www

.ipc.org/IPC-WP-011 IPC白皮书。

IPC/JEDEC-9704A 2012年2月

8