IPC-7095D-CHINESE NP 2019.pdf - 第53页

IPC-7095D-W AM1 CN 2019 年 1 月 37 顺序堆叠预先测试过的 FBGA 封装使元器件密度和功 能性急剧增加 。作为当前应用的一个可行案例 ,可在 单面小外形双排直列存储器模组( SO-DIMM )上考虑 存储容量的动态和潜能,如图 4-28 所示。 4.4.10 折叠和堆叠的封装组合 由于处理器和 ASIC 晶圆制造良率不像存储器或功能复杂度低的集成电路 那样可预测 ,因此必须在封装组装前对每一个芯片进 行测试…

IPC-7095D-WAM1 CN 2019 年 1 月

36

率。某些多芯片封装方法是在单个基板上将一个芯

片叠加连接到另一个芯片的上面,如图 4-24 所示。

常见的是以金字塔形叠加不同尺寸的芯片,但是当

芯片尺寸相同时,各有源芯片间要加入隔离片以消

除键合线弧。

4.4.7 系统级封装(SiP)

制造商将大量相关功能

单元合并至单个封装外形中以便为额外功能提供空

间。尽管一些制造商选择研发多功能芯片(片上系

统),但这个选项对于许多其它制造商来说可能并不

实际。由于开发带有混合功能能力的定制芯片其时

间跨度太长,将已验证的芯片组合(叠加)在单个

封装结构内更为实际(见图 4-25 的芯片叠加示例)。

由于制造工艺的偏离以及来自于多种货源不同的芯

片级产品良率潜能,对某些器件来说,总封装级别

的成本目标不是总能达成的。为了保证未封装裸芯

片的质量和可靠性,在封装级组装前必须对裸芯片

进行一些种类的电气性能测试。ASIC、简单逻辑

电路、某些处理器以及线性电路在某一时间段趋于

稳定,然而测试依然是对质量和可靠性用于证明的

指标。比如,将逻辑和存储器整合在单一封装上,

会造成非常实际的问题。这两种功能的测试有本质

上的不同,且将会进一步损害用户使用此产品的信

心。

4.4.8 三维(3D)折叠封装技术

存储器芯片(如

Flash 或 SRAM),有比较高的制造良率。虽然在组

装加工和操作中会发生损伤,但总体上存储器芯片

的封装和测试制程有很高的良率。挠性基板材料可

将几个芯片折叠并放置在单个 FBGA 封装外形之

内,此封装仅比芯片组中最大的一个略大。图 4-26

为常见的折叠挠性封装应用,将三个独立的存储器

芯片合并在单封装外形中。

4.4.9 焊球堆叠

尽管不限于存储器封装,堆叠的

一个主要应用是双倍数据速率同步 SDRAM 芯片

堆,它可使原始设备制造商(OEM)和存储器模块

制造商增加存储器板密度高达八倍。将预测试合格

的 FBGA 封装芯片堆叠是存储器的一种理想应用。

联接前对存储器的测试、挑选和分级可保证最终器

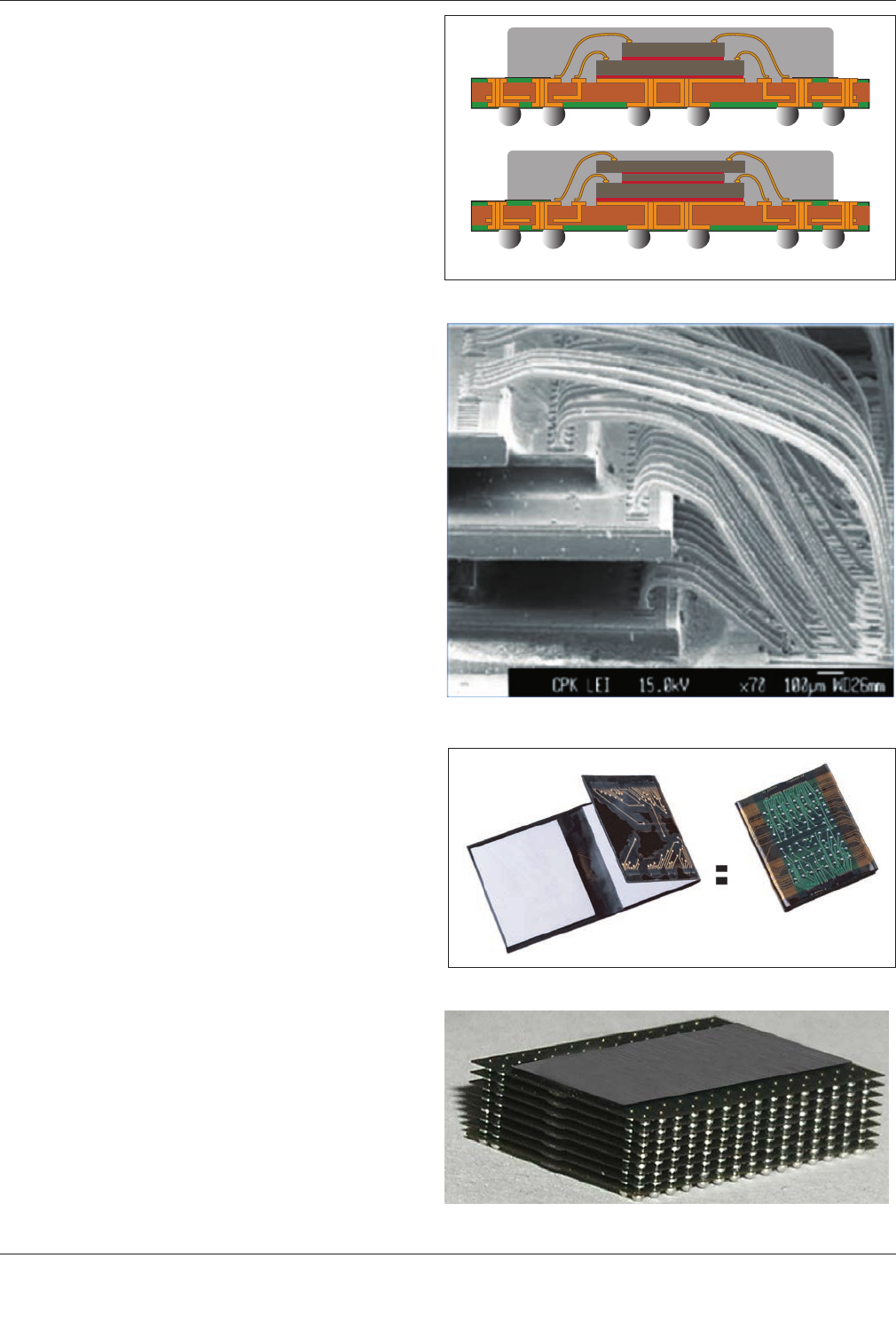

件配置能提供全部的潜在性能。图 4-27 展示了将几

个焊球封装堆叠为一个整体组件的案例。

IPC-7095d-4-24-cn

图 4-24 单封装芯片叠加 BGA

图 4-25 定制八芯片(倒装芯片及金属线键合)SiP 组件

图 4-26 折叠式多芯片 BGA 封装

图 4-27 八层焊球堆叠封装

IPC-7095D-WAM1 CN2019 年 1 月

37

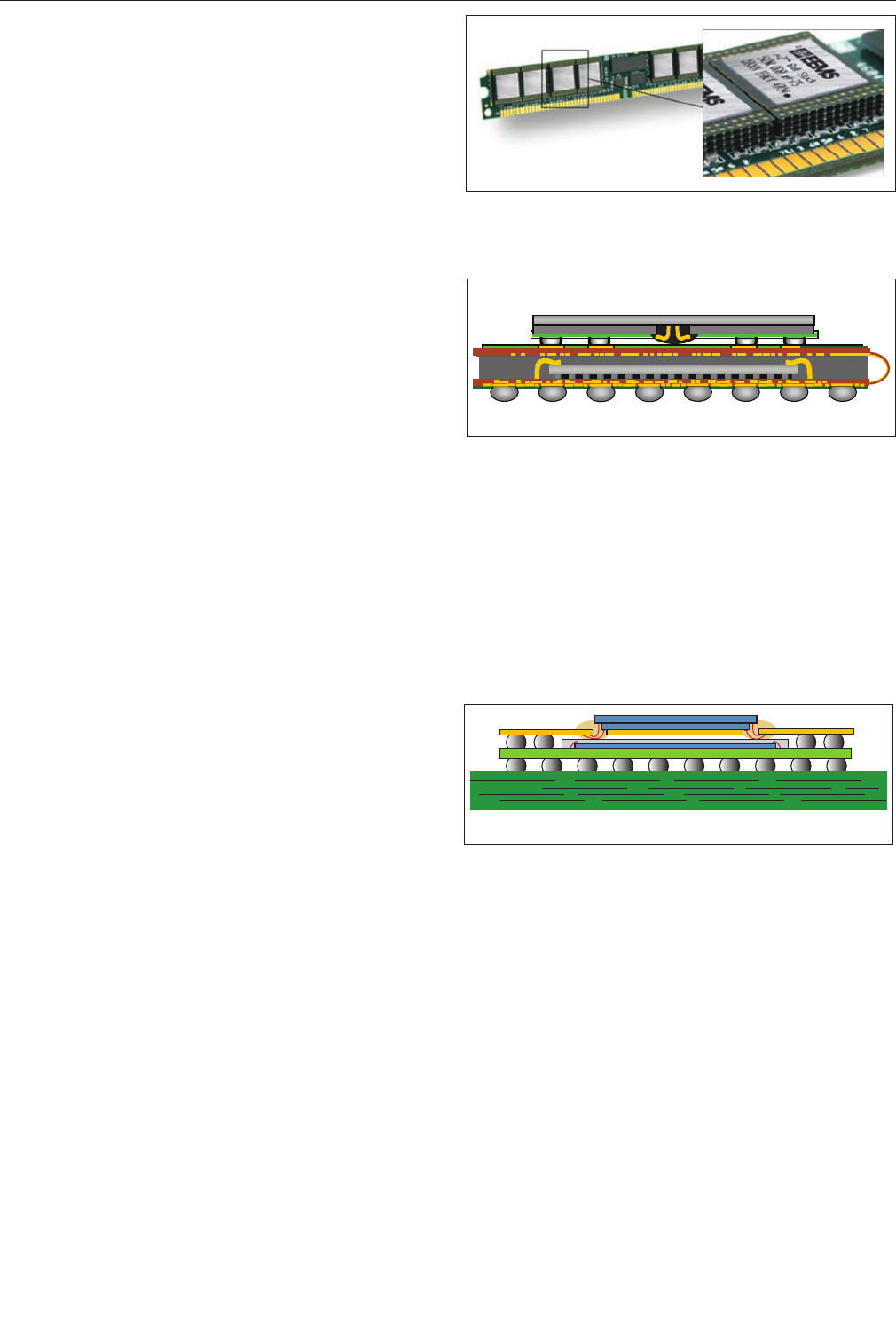

顺序堆叠预先测试过的 FBGA 封装使元器件密度和功

能性急剧增加。作为当前应用的一个可行案例,可在

单面小外形双排直列存储器模组(SO-DIMM)上考虑

存储容量的动态和潜能,如图 4-28 所示。

4.4.10 折叠和堆叠的封装组合

由于处理器和 ASIC

晶圆制造良率不像存储器或功能复杂度低的集成电路

那样可预测,因此必须在封装组装前对每一个芯片进

行测试。另外,将两种良率差距较大的器件置于同一

成品封装中风险是非常大的。为了将风险最小化,顺

序叠加多芯片封装的理念变得很有吸引力。

由于将几种功能组合在单个封装的最终目标仍是可行

的,在最终整合之前对单个器件进行组装和测试是比

较理想的。与合成良率和测试相关的问题可以较容易

地通过堆叠单个封装来解决。一个例子是两分区格式

的存储功能模块中各自封装和测试 ASIC,典型地如同

图 4-29 所示。

带有存储器的上下封装组件在折叠和合并之前进行处理和测试。通过折叠和表面贴装连接处理,这两个预测试

过的分区成为单个、高良率的多功能元器件。除此之外通过在 ASIC 封装顶部上提供通用阵列图形界面,一些

不同的存储功能块可以直接焊接该封装基础上。

4.4.11 叠装封装(PoP)

在单个封装外形内封装多个芯片单元的解决方案已得到迅速发展。对于许多高密度

存储应用来说,在单个半导体封装基板上将数个半导体芯片进行垂直叠加已证明是有效的。但是将一些较新的

多功能处理器和控制器产品与一些较成熟的高良率存储单元混合时,总封装良率不是总能满足预期。

已证明 PoP 是更有效的一种多芯片封装方法,其设计

是将已完全封装和经过预测试的分立逻辑和存储器件

垂直组合在独立的、阵列配置的封装基板上,将它们

设计成相互对齐并上下堆叠,典型地如图 4-30 所示。

封装叠加方式对于需要多功能、高性能和小脚位的各

种应用是理想的。堆叠经过预测试的封装分区使得设

计人员有高度的灵活性,几乎允许任何存储器组合和

与任何逻辑芯片组相结合。以垂直布局的方式将分立的逻辑器件和存储封装进行组合,不仅节省了它们在印制

板的空间,而且也会减少引线数量,简化系统集成度并使性能得到加强。一些产品(如无线耳机、数码相机、

便携式游戏机等)就利用了这种多芯片封装方案的优点。

4.4.12 多芯片封装的优势

多芯片封装的主要优势是元器件密度急剧增加和空间限制的缓解。产品的尺寸和重

量可能会减小,但其功能性却得到了增强。功能的增强是通过集成几个不同类型器件来实现的。其它的优点包括:

• 降低印制板复杂性

• 通过更高的可靠性改善产品质量

• 降低产品进入市场的风险

使用多渠道已证实的成熟芯片,可使上市时间和拥有成本最小化。研发多芯片产品的任务并不是没有障碍,其

中一些关键问题为:

图 4-28 单面小外形双排直列存储器模组(SO-

DIMM)存储卡组件

IPC-7095d-4-29-cn

图 4-29 折叠以及堆叠的多芯片 BGA 封装

IPC-7095d-4-30-cn

图 4-30 叠装封装(PoP)组件

IPC-7095D-WAM1 CN 2019 年 1 月

38

• 需管理多个供应商(成本,物流和变更控制)

• 已知好的芯片测试和老化方法

• 芯片和晶圆可获得性

• 整合高、低良率的器件

• 总体的产品质量和可靠性

有关补充和相关主题的详细信息,如晶圆级封装和 CSP,参见 IPC-7094;关于 3D 封装,参见 IPC-7091。

4.5 BGA 连接器和插座

4.5.1 BGA 连接器材料考量

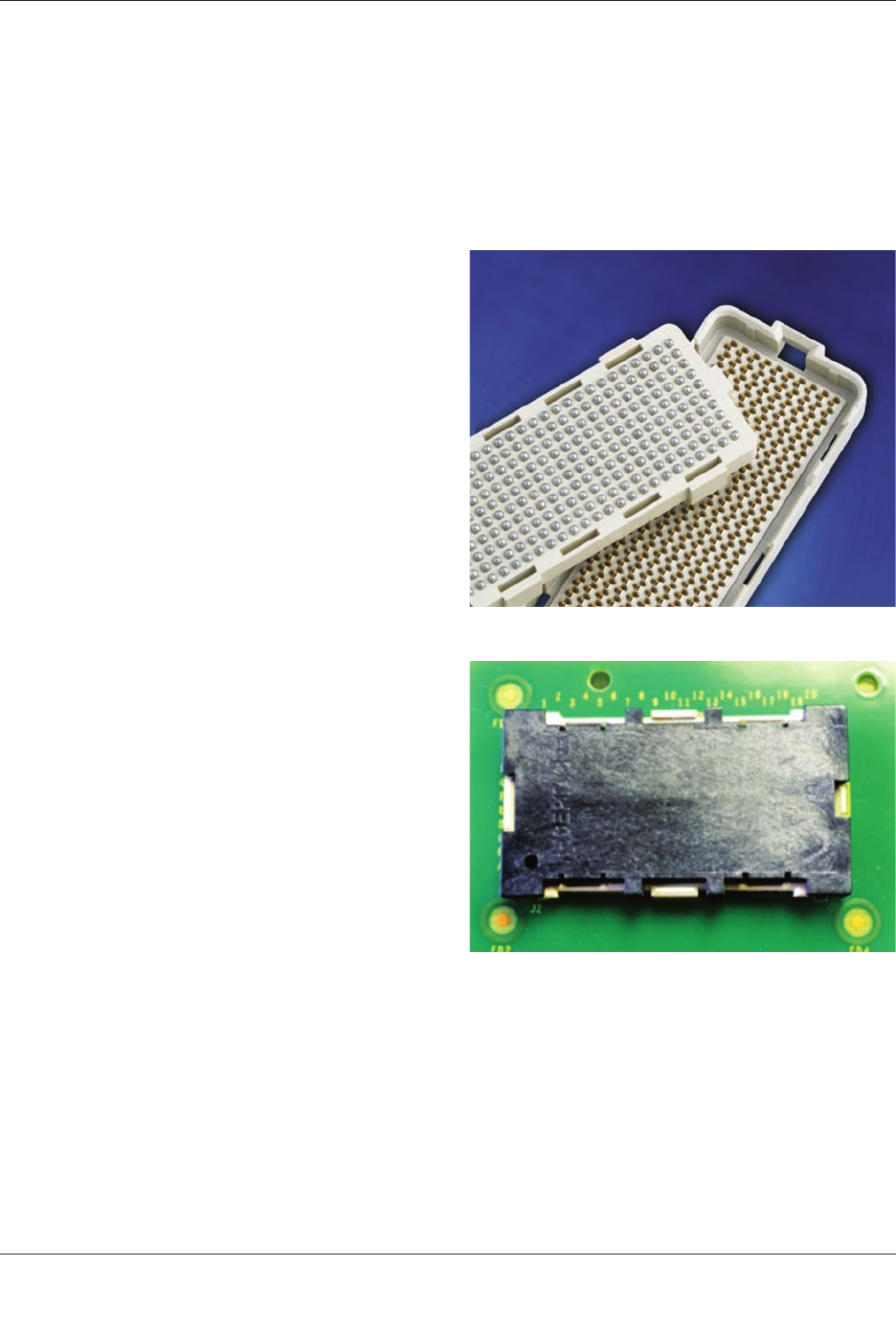

图 4-31 所示的 BGA 连

接器设计在两个印制板组件间提供相对低外形的水平

或平行界面。已开发出为这种应用设计的材料以承受

与 SMT 组装相关的再流焊接温度,并提供典型产品终

端使用在变化的环境条件下的可靠互连。

了解连接器系统的材料性质很重要。在产品寿命周期

之内,印制板组件会经历许多不同的热循环,这些热

循环会导致组件中的元器件材料包括 BGA 连接器的膨

胀和收缩。由于连接器和印制板基板之间的热交互作

用,因此选择 BGA 连接器材料很重要。特别地,BGA

连接器材料与印制板基板材料的 CTE 匹配性对于封装

和焊点的可靠性很重要,CTE 的高度匹配可使热导致

的应力最小化。在选择外壳树脂、端子方向和触点的

许多设计都应考虑到这一点。

4.5.2 BGA 连接器的连接考量

BGA 连接器贴装并焊接到印制板基板上时需要解决几

个事项,一些 BGA 连接器设计,没有提供用标准的

SMT 吸嘴来真空拾取它们。在这种情况下,有以下两

个选项:

1)使用定制的吸嘴进行机械吸盘拾取

2) 设计带有盖子或其它临时吸附表面的 BGA连接器,

这样可用标准的真空吸嘴(见图 4-32)。

这两种选择对于生产都是可行的,最佳的选项主要取

决于连接器的设计。取决于连接器材料,必须验证再

流焊温度曲线并比较连接器材料的 Tg。当连接器的温

升超过了其 Tg 点,连接器有向印制板内拱或向板外翘的倾向(翘曲)。实际的行为取决于:

• 连接器几何形状

• 连接器材料

• 连接器焊球与基板之间的表面张力

• 成功焊接所需的连接器共面性要求

再流焊过程中的材料性质表现和连接器的整体尺寸决定了连接器焊球共面性要求。

图 4-31 BGA 连接器

图 4-32 带真空帽的 BGA 连接器