IPC-7095D-CHINESE NP 2019.pdf - 第80页

IPC-7095D-W AM1 CN 2019 年 1 月 64 唯一能注意到的影响是一个小凹痕。设计时可以借助类型 VII 导通孔保护概念进行填塞和遮蔽导通孔,以避免 出现凹痕(见图 5-13 ) 。通过将导通孔直接布置于连接盘上,外层 BGA 连接盘之间的间隙可只用作布线。 在设计包含导通孔或微导通孔的 BGA 连接盘图形之前,联系印制板制造商以确定相关选项和规则。 6.2.5 影响 BGA 阻焊膜的参数 连接盘图形和 / 或阻焊膜…

IPC-7095D-WAM1 CN2019 年 1 月

63

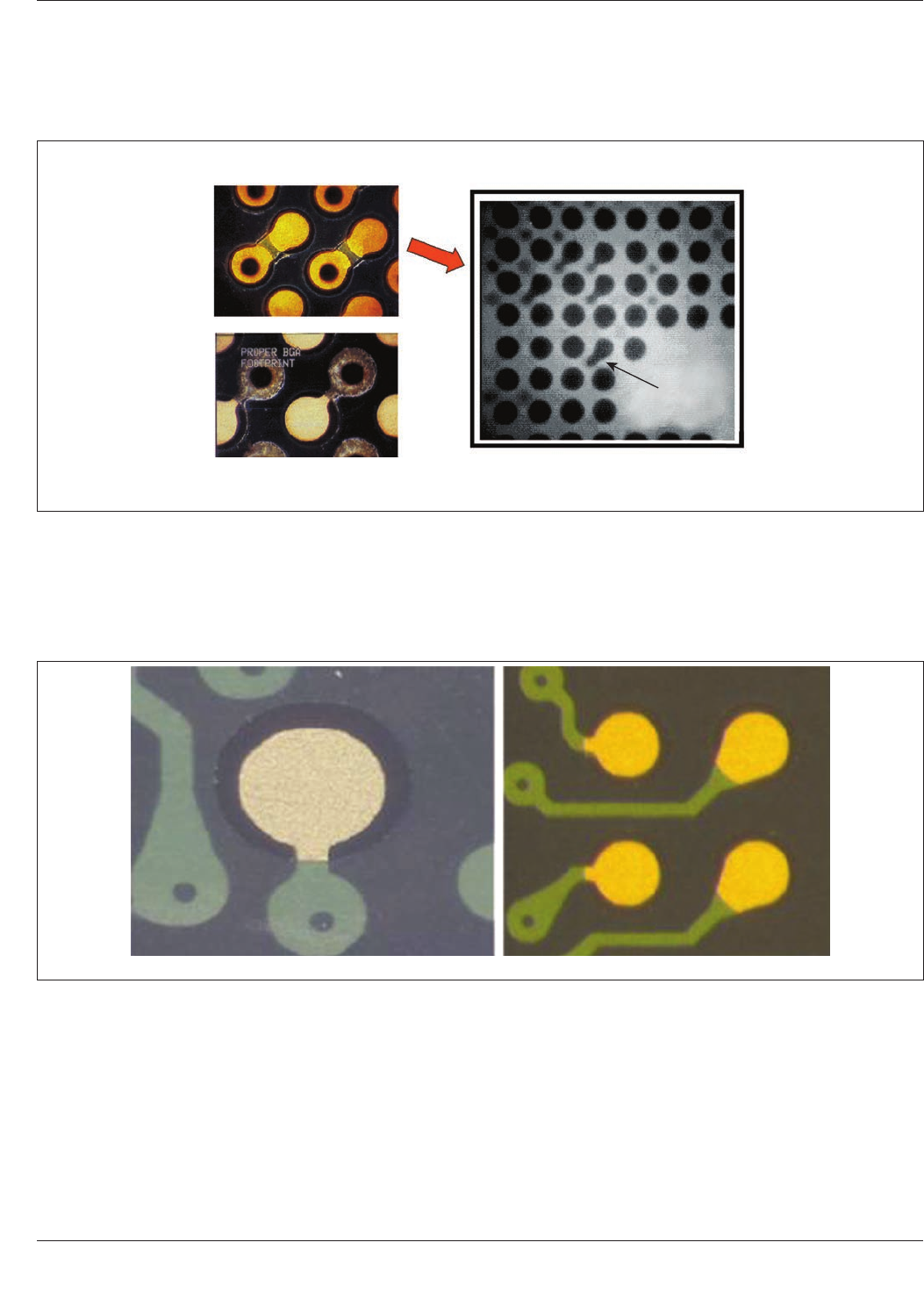

导通孔连接盘上覆盖阻焊膜也会降低 BGA 返工时狭窄阻焊膜坝脱落的风险。某些阻焊膜与表面处理组合的掩

蔽导通孔可能并不可靠。侵入孔上的阻焊膜开窗应该大到足以使助焊剂和其它污染物在焊接时排出。在准备用

掩蔽或侵入导通孔时,咨询印制板制造商确认其能力。图 6-6 为较好的和较差的阻焊膜设计示例,图 6-7 是金

属限定连接盘的示例。

A

B

C

IPC-7095d-6-6-cn

图 6-6 好 / 差的阻焊膜设计

A– BGA 走线和阻焊膜设计

B– 显示焊点影响

C– 由于不正确的走线和阻焊膜设计导致焊料被吸入导通孔

IPC-7095d-6-7-cn

图 6-7 金属限定连接盘示例

BGA 连接盘图形上导通孔的其它选择包括盲孔和微导通孔。盲孔可用钻孔、激光、烧蚀或者通过湿式或干式(等

离子)化学的感光限定法来实现。外层和内层依次制备,然后层压在一起。因为盲孔仅穿透外层,故采用尺寸

较小的钻头。但是通常这种方法成本较高。盲孔可以布置在连接盘之间,但是由于该盲孔盘尺寸较小,是否将

盲孔布置在两连接盘间的中心并没有那么重要。

微导通孔由二次加工实现,仅穿透印制板外层。标准微导通孔连接第 1 层与第 2 层和/或第 n-1 层与第 n 层。

典型的微导通孔连接盘大小为 0.3mm,钻孔尺寸为 0.1mm。由于尺寸较小,这种微导通孔被置于连接盘的中央,

IPC-7095D-WAM1 CN 2019 年 1 月

64

唯一能注意到的影响是一个小凹痕。设计时可以借助类型 VII 导通孔保护概念进行填塞和遮蔽导通孔,以避免

出现凹痕(见图 5-13)。通过将导通孔直接布置于连接盘上,外层 BGA 连接盘之间的间隙可只用作布线。

在设计包含导通孔或微导通孔的 BGA 连接盘图形之前,联系印制板制造商以确定相关选项和规则。

6.2.5 影响 BGA 阻焊膜的参数

连接盘图形和 / 或阻焊膜尺寸的变化可能会导致 BGA 焊接缺陷或可靠性问

题。主设计图纸和印制板制造商的工作文件可能需要根据以下项目来评审以确认设计。出现任何变化必须与设

计人员和印制板制造商讨论。

为了确保 BGA 再流焊接成功,应该认真考虑下列问题:

• BGA 连接盘图形尺寸(见 6.2.1)与阻焊膜开窗的对比

• BGA 连接盘选择

- SMD 连接盘(见 6.2.2.2)

- 金属限定连接盘 MD(见 6.2.2.1)

- 同一 BGA 位置的两种技术

• 阻焊膜材料的选择

• 适应 BGA 连接盘节距的阻焊膜公差

• 线条至导通孔上面的阻焊膜(导通孔尺寸和位置见 6.2.4)

• 阻焊膜最大厚度

另外,也必须要评审阻焊膜定位和印制板制造商的能

力(收缩和补偿见 5.4.3)

确保印制板制造商不在原始设计文件的基础上修改阻

焊膜开窗或网格设计(为适应内部的制程能力)是很

重要的。BGA 布线和阻焊膜设计的最小的网格尺寸必

须与板制造商的能力相匹配。例如,典型的常规最小

激光可成像的阻焊膜网格为 0.15mm。先进的最小网格

可以是 0.0762mm。使用 0.15mm 的阻焊膜网格认为是

标准技术,印制板制造商没有理由进行额外的更改。

因此,重要的是审查和验证制造商实际生产的印制板

结构,以确保预期的 BGA 连接盘和结构的形成。

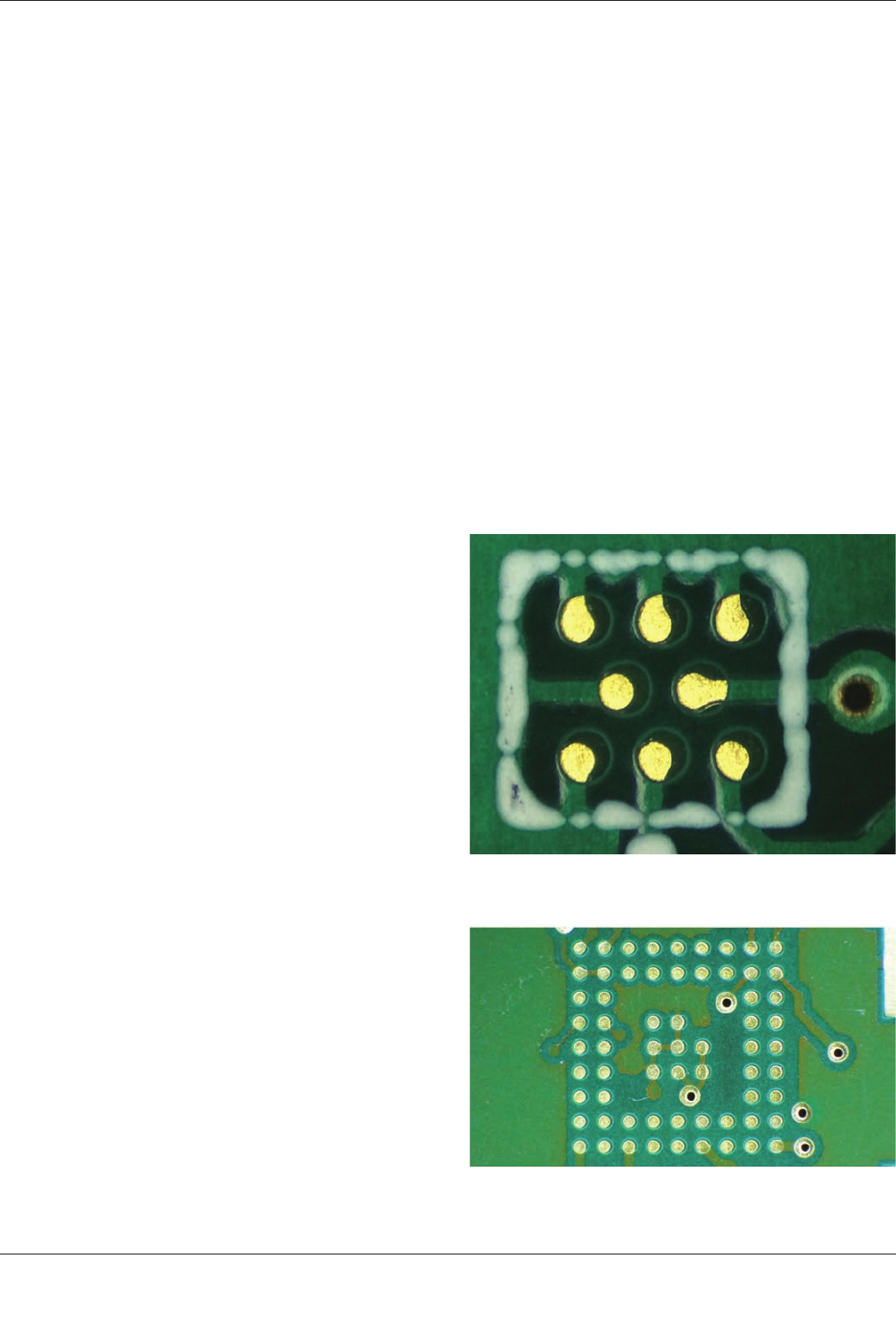

图 6-8 和图 6-9 显示了阻焊膜定位质量的对比示例,图

6-8 还显示了一种示例,丝网图例油墨勾勒 BGA 连接

盘图形,该图形预计会妨碍印刷模板均匀接触(例如

贴合)焊盘阵列的能力。

6.2.6 多栅格 BGA 连接盘图形阵列设计

对于 CPU

需要较高 I/O 密度的设备诸如移动电话、平板电脑和

超轻型便携式计算机等移动设备已驱动 BGA 元器件间

距降至 0.5mm 或者更小,且 I/O 数量大于 1,500。这种

密集的连接盘图形的布线模式需要多个导通孔和多层

数。印制板的成本随着层数的增加而显著上升。为了

将成本和层数保持在低位,尽可能多的将高密度的 I/O

图形布局在在外层势在必行。

图 6-8 差的阻焊膜定位

图 6-9 好的阻焊膜定位

IPC-7095D-WAM1 CN2019 年 1 月

65

为了实现这一目标,需要采用 BGA 焊球和连接盘设计

的一种替代策略。一种策略是抛弃 I/O 固定网格位置的

概念,取而代之的是采用多网格设计方法,也被称为焊

球随布。这大大增加了印制板对于高密度 I/O 元器件的

可布能力。

焊球随布 I/O 布局设计方法区别于固定网格位置设计

方法。焊球随布设计包含了不同网格的多个连接盘区

域,甚至一些没有规则网格的连接盘区域,因此增加了

PCB 的可布线性以减少层数。

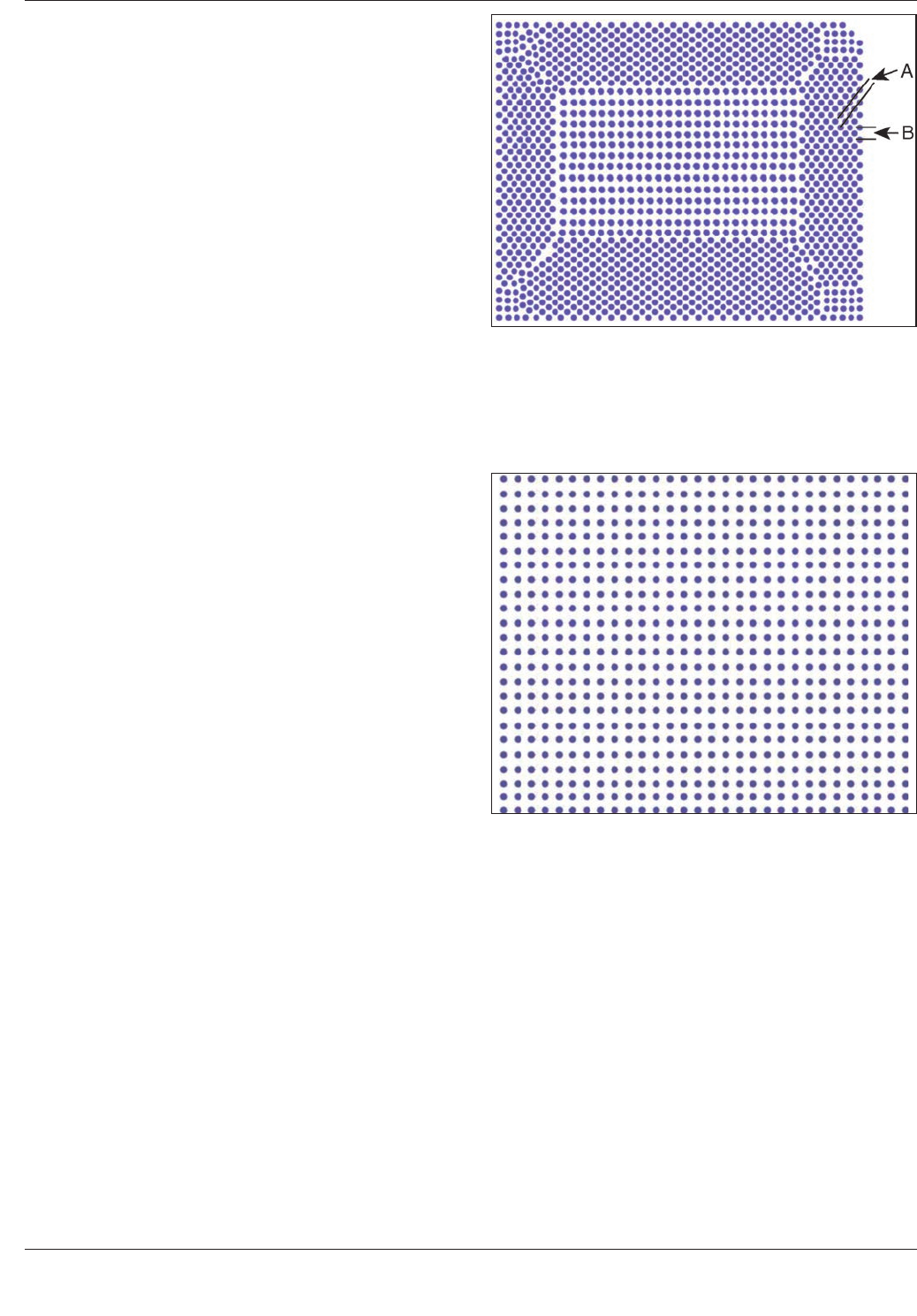

图 6-10 显示了 CPU 元器件的一个连接盘图形,是焊球

随布连接盘设计的一个示例。其连接盘按照不同网格来

布局。

• 角落的连接盘按照一种网格。

• 中心区域连接盘按照另一种网格,

• 侧面按照另一种网格,它是散布网格图形,并具有最

密的连接盘间隙。

这种连接盘图形设计中最靠近的连接盘至连接盘节距是

0.4mm,这些不同网格区域之间的过渡区域似乎有一些

连接盘 没放置在任何网格上。

将图 6-10 的连接盘图形和图 6-11 显示的均匀网格图形

作比较,可以发现,焊球随布连接盘图形可能的线性布

线密度(图 6-10)比均匀网格连接盘图形的(图 6-11)

多 40% 至 50%,导致较低的层数和印制板成本。

焊球随布封装在印制板设计上是为特定应用和客户定制

的,用户需要与封装供应商合作获得焊球随布封装。

6.3 出线和布线策略

与外围引线封装不同,BGA 焊

点不容易全部在印制板外层访问,尤其是对于大尺寸、

全栅阵列的 BGA 封装,可能需要增加额外层将信号从封装中间的底下引出。

例如,一个节距为 1.27mm,引脚数为 357 的 PBGA,为角落不带焊球 19×19 的全栅阵列。如果使用尺寸为

0.63mm 的连接盘,则连接盘之间可供布线的间距仅为 0.63mm。在这种情况下,只能允许在连接盘间布置一

条宽度为 0.2mm 的导体,即封装只有最外两排引脚(共计 136 个)可通过外层将其导出。剩下的引脚(共计

221 个)需要连接导通孔并通过其它信号层将其引出。如果导体宽度和间距均为 125

μ

m,连接盘之间可布置两

条导体,于是最外三排的引脚(共计 192 个)可通过外层引出,剩余的引脚(共计 165 个)则需要借助导通孔

将其引出。

随着 BGA、FBGA 及 CSP 的节距不断缩小,印制板导通孔图形需要更严格的要素控制。

图 6-10 焊球随布 BGA 器件的焊球随布连接盘图形

设计

A– 最窄的通道

B– 较宽的通道

图 6-11 均匀网格 BGA 连接盘图形