IPC-7095D-CHINESE NP 2019.pdf - 第96页

IPC-7095D-W AM1 CN 2019 年 1 月 80 • 可能会影响元器件放置、导体布线、连接器触点分配的测试/故障定位要求 • 加工余量(如用于导体宽度、间距、连接盘制造等的蚀刻因子补偿) • 制造限制(例如最小蚀刻外形、最小镀层厚度、印制板形状和尺寸等) • 涂层和标记要求 • 使用的组装技术(如 SMT , 通孔或混合技术) • 印制板性能等级 • 材料选择 • 基于制造设备限制条件的印制板组件的可制造性: – 挠性(…

IPC-7095D-WAM1 CN2019 年 1 月

79

和接地引脚来发现在器件信号通道上的焊点开路、键合线损坏和由 ESD 导致的器件失效,元器件安装方向

不正确也可被检测到。这类测试需要使用含有磁感应器的夹具。

3)

电容耦合测试

—这项技术使用电容耦合来测试引脚开路。它不依赖于器件内部电路,而是依靠器件存在的

金属引线框来测试引脚。连接器和插座、引线框和电容极性的正确性可采用这种技术检测。

6.5.4.1 测试过程中的电路板弯曲

由于无铅焊点比锡铅焊点更刚硬而缺少延展性,如果 ICT/FT 夹具设计和

使用导致印制板组件过度弯曲,则它们会损伤焊点。这种弯曲引发的损伤通常由印制板组件支撑和下压位置不

恰当造成的,特别是在测试探针密集区域周围。过度弯曲还会由支撑板和下压板平面不平齐、探针压力过大、

过度或不足的真空度或上压板和针床板之间的弹簧不合适分布而引起。另外,设计不合理的工装夹具会很容易

导致组件异常弯曲,进而引发损伤。

为了确保测试夹具不会对印制板组件造成损伤,在测试夹具使用期间必须要对组件的应变和应变率进行测量。

按照 IPC/JEDEC-9704 标准推荐的应变片放置位置,用三元矩形应变花对 BGA 角落进行应变测量。应变和应

变率应在“应变极限规范”中规定,该规范定义了对待测产品加载、测试和释放的要求。

此外:

• 应变测量系统必须能同时对所有应变花方向(e1,e2,e3)进行取样,以正确地测量和计算所有的应变分量

• 在主轴或对角线方向,锡 / 铅组件可接受应变极限为 600

με

• 在主轴主对角线方向,无铅组件可接受应变极限为 450

με

• 在主轴或主对角线方向,常用应变率极限为 30,000

με

/s,

• 典型的损伤可接受标准为:使用切片失效分析方法,未发现 BGA 焊点的损伤。

6.5.4.2 在线测试(ICT)问题

ICT 可探查开路、短路、错件、元件反置、器件失效、不正确组装以及其它

制造缺陷。ICT 既不能找出处于合格边缘状态的元件,也不能验证关键时序参数或其它电气设计功能。

数字印制板组件的 ICT 会涉及到被称为反向驱动的工艺。反向驱动也可导致器件振荡,并且测试设备可能会

因驱动不足而使装置处于非饱和状态。反向驱动仅可在时间受控的条件进行,否则,器件结点(具有过度驱动

输出)会出现过热现象。

ICT 方面需要关注的两点是,印制板和印制板组件的设计应与 ICT 夹具和电气设计要素相兼容。

6.5.4.3 功能测试(FT)问题

在设计印制板组件时必须考虑一些与 FT 相关的问题。敷形涂覆印制板组件或

者大部分 SMT 板和混装技术设计的故障隔离是非常困难的,因为印制板上缺少电路接入点。如果重要信号可

引出至测试连接器或者印制板上信号可探测的区域(测试点),则故障隔离会得到大幅改善。这会使探测、隔

离和纠错的成本降低。也可设计一个电路,使得测试连接器可以用来激励电路(如将测试连接器作为数据总线)

或者屏蔽印制板组件的功能(如屏蔽自激振荡器并通过测试连接器加入单步运行功能)。

6.6 其它可制造性设计(DfM)问题

布局生成报告应该包括对布局细节进行正式的设计评估,这些评估由

公司内部尽可能多的相关部门如制造、组装和测试参加。由受影响的代表部门批准布局方案可确保设计中已考

虑了与生产相关的因素,互连结构设计是否成功取决于许多互相影响的因素。从终端产品使用立场来说,应该

考虑以下常见 DfM 参数对于设计的影响:

• 设备环境条件(如环境温度、元器件所产生的热量、通风、冲击和振动)

• 必须考虑元器件 / 电路密度、印制板 / 敷形涂敷材料的选择和元器件安装的可达性(如果组件是可维护和可

修理的)

• 可能会影响到安装孔大小和位置的安装界面、连接器位置、引线伸出限制、元件放置、支架和其它硬件的布局

IPC-7095D-WAM1 CN 2019 年 1 月

80

• 可能会影响元器件放置、导体布线、连接器触点分配的测试/故障定位要求

• 加工余量(如用于导体宽度、间距、连接盘制造等的蚀刻因子补偿)

• 制造限制(例如最小蚀刻外形、最小镀层厚度、印制板形状和尺寸等)

• 涂层和标记要求

• 使用的组装技术(如 SMT, 通孔或混合技术)

• 印制板性能等级

• 材料选择

• 基于制造设备限制条件的印制板组件的可制造性:

– 挠性(弯曲)要求

– 电气 / 电子

– 性能要求

• ESD 敏感度考量

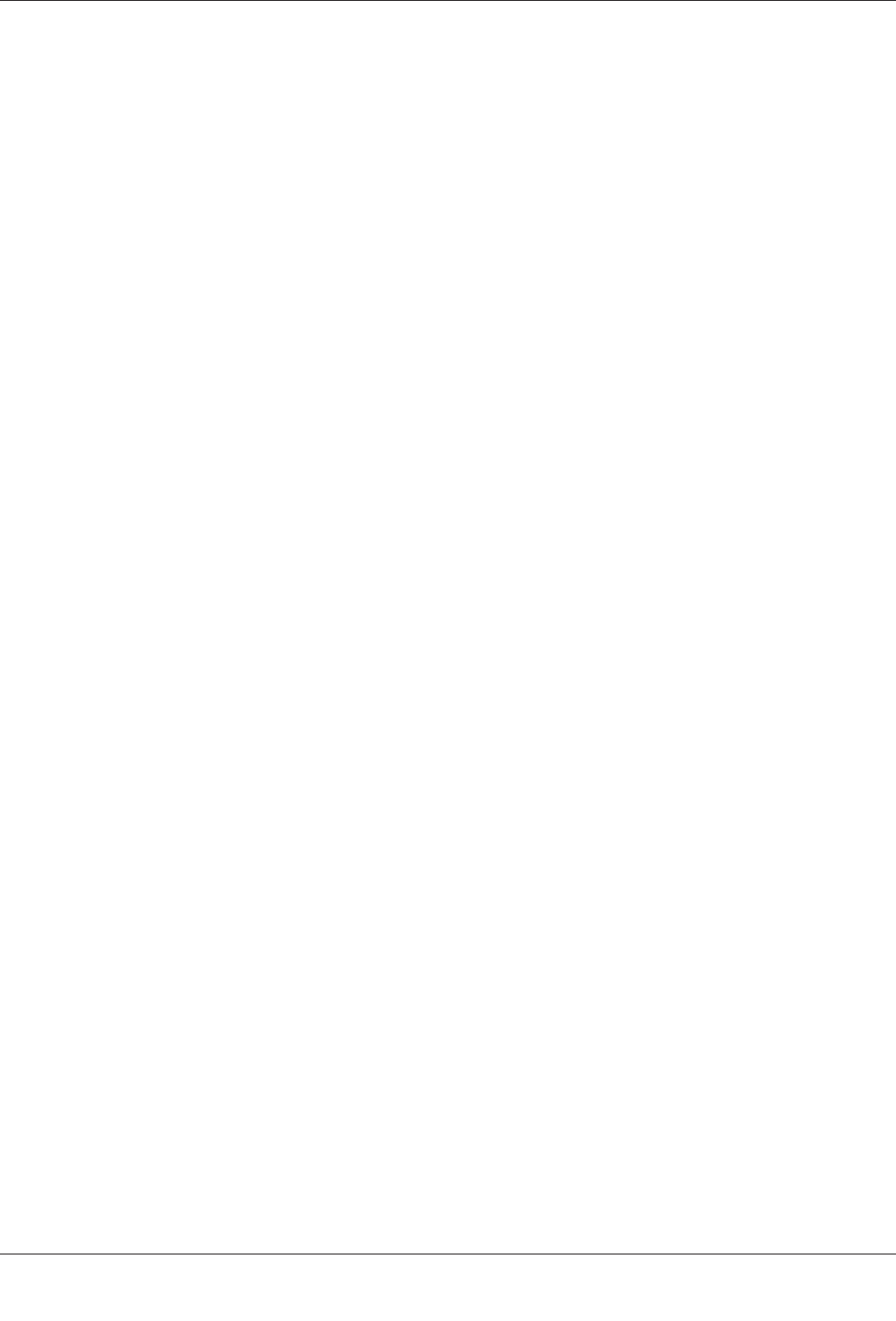

6.6.1 在制板/拼托板设计

印制板拼联和拼托板对于测试和组装是一种标准的工艺。在制板制造需要基准系

统,同样在制板中单个印制板或拼托板都需要各自的基准系统。为了减少产生公差累积,将各单板基准与在制

板基准关联是很重要的。(见图 6-39)

大部分组装厂都想要用拼托板的形式进行组装,如图 6-39 所示。这些拼托板制造商可能在一张标准在制板上

将它们定位,在制板通常为 460mm×610mm。鼓励设计人员与制造供应商合作以优化物料流动、拼托板/单

板各自的分离方式以及如何进行测试。

6.6.2 中间制程 / 最终产品测试附连板

附连板旨在评估在制产品。它们能代表印制板或印制板组件的特征,

它们被整合到在制板板边为印制板厂商使用或整合到拼托板板边供组装厂商使用。大部分制造商和组装厂都有

自己受控的工艺。然而,通过各种物理方法评估测试附连板,对于弄清楚生产该部件的工艺和方法是否处于满

足要求所必要的受控状态是有价值的。

这种理念对于 BGA 来说是必要的,因为组装后人们无法看见连接盘或者焊点。测试附连板或试样应该反映了

具体印制板或在制板的特性。由在制板导出的数据应该用于建立导通孔和连接盘、线条、间距等要求。当试样

用于建立工艺控制参数时,它们

应当

持续使用可反映出此工艺的单孔尺寸或连接盘配置。工艺特性和通用的印

制板特性应该互相匹配。

IPC-2221 提供的附连板用于评估这些印制板和印制板组件特性,它们包括:

• 孔可焊性

• 防焊掩蔽

• 热应力电镀

• 厚度和连接强度

• 镀层附着力

• 表面可焊性

• 阻焊膜

• 表面贴装可焊性

• 表面键合强度

• SIR 表面绝缘电阻

• 湿度和绝缘阻抗

• 定位

• 互连电阻

IPC-7095D-WAM1 CN2019 年 1 月

81

图 6-39 板拼联

A– 拼板工具孔(3 处)

B– 单板工具孔(每块板 3 处)

C– 基准

X.XX

X.XX

X.XXX

X.XXX

X.XXX

X.XX

X.XXX

C

C

X.XXX

X.XX

A

B

IPC-7095d-6-39-cn

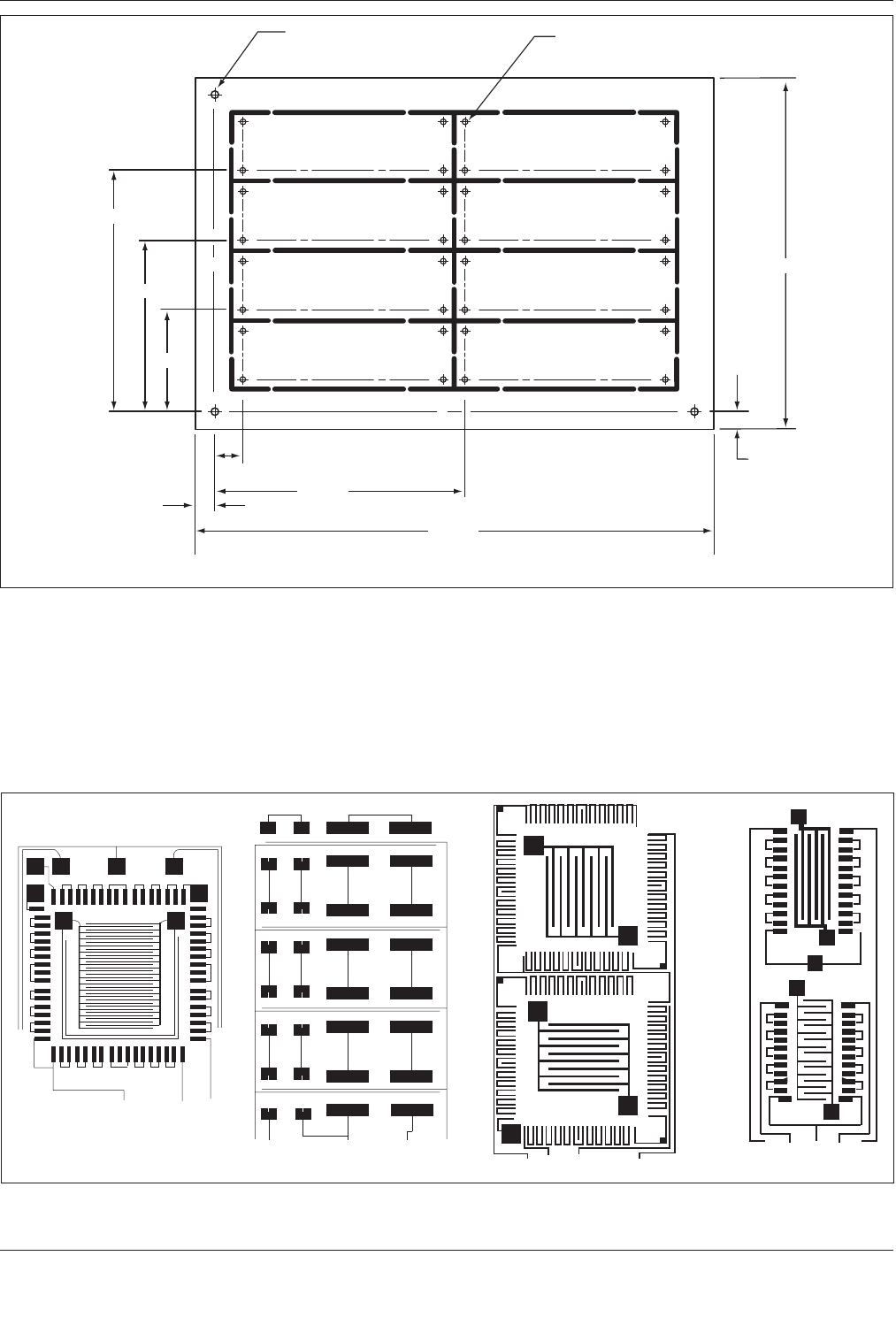

图 6-40 展示了焊球焊接完成之后,常用来评估印制板组件清洁度的其它附连板。这些用于组件的梳形电路是

为了确认助焊剂或助焊剂残留不会损害产品的电气性能。

图 6-40 梳形电路示例

IPC-7095d-6-40-cn