IPC-7095D-CHINESE NP 2019.pdf - 第83页

IPC-7095D-W AM1 CN 2019 年 1 月 67 图 6-16 所示为一些焊球缺失 、空白或空缺的 4 × 4 方 形阵列。 外围焊球扇出导体到周边与外界互连相对来说并不 难。 但是阵列内部的焊球必须要从外围焊球之间走线。 随着阵列尺寸的增加 ,越来越多的导体阵列内部焊球 中引出 ,而必须在外围焊球之间走线以连接外界 。重 要的是基板设计人员要知道在相邻焊球间距中需要容 纳多少导体数量 ,以便确定导体的宽度和导体间的间 …

IPC-7095D-WAM1 CN 2019 年 1 月

66

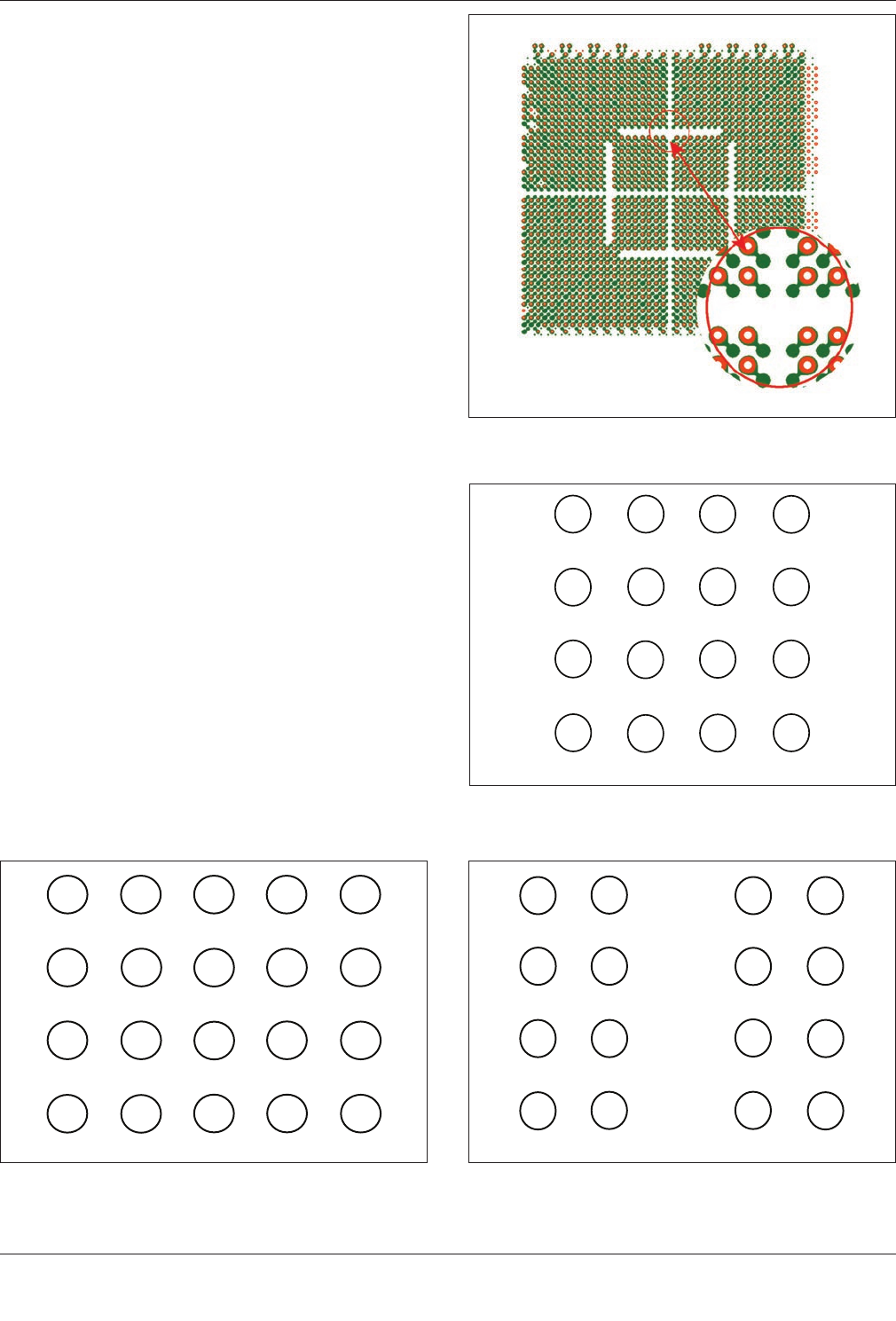

扇出图形应该为电源区域显示出特有的十字。由于电

源间隙的原因,当 BGA 扇出时没有使用十字图形,可

能发生电源隔离的情况,而在内部电源引脚的周围形

成了围墙。这种十字图形也为内部或交叉的 BGA 网络

布线留下余地(见图 6-12)。

成功的 BGA 扇出包括:

• 只要可能,坚持布局网格与扇出网格对齐。

• 在布线时保护 BGA 扇出导通孔。

• 合适的导通孔和连接盘尺寸。

BGA 扇出的一种可替代方法是不扇出 BGA 最外两排 /

列周围引脚。对于最外两排,可允许布线工具以宽松

的距离规则布置扇出导通孔。最外两排宽松的扇出可

在 BGA 周围形成双排直插(dip-like)图形,可由自动

布线器来完成。双排直插图形和 BGA 图形的间距使得

非 BGA 网格可以跨过 BGA 区域,而不需要通过内部

BGA 扇出图形。这种方法可在带有 BGA 的印制板布

线出现问题时进行尝试。

为了便于布线,可将电源和接地引线布置在阵列图形

的中心,这样它们可以与导通孔直接相连接而不会妨

碍封装外围边缘的布线。

BGA 可为方形或矩形。方形阵列的行数与列数相等。

图 6-13 所示为 4×4 的方形阵列。

矩形阵列的行数与列数不相等。图 6-14 所示为 4×5 的

矩形阵列。

阵列可填充,也可在某些位置不填充。图 6-15 所示为

中间一列未使用、空白或空缺的 4×5 矩形阵列。

图 6-12 BGA 象限图形

IPC-7095d-6-13-cn

图 6-13 方形阵列

IPC-7095d-6-14-cn

图 6-14 矩形阵列

IPC-7095d-6-15-cn

图 6-15 有空缺的矩形阵列

IPC-7095D-WAM1 CN2019 年 1 月

67

图 6-16 所示为一些焊球缺失、空白或空缺的 4×4 方

形阵列。

外围焊球扇出导体到周边与外界互连相对来说并不

难。但是阵列内部的焊球必须要从外围焊球之间走线。

随着阵列尺寸的增加,越来越多的导体阵列内部焊球

中引出,而必须在外围焊球之间走线以连接外界。重

要的是基板设计人员要知道在相邻焊球间距中需要容

纳多少导体数量,以便确定导体的宽度和导体间的间

距。这些信息有助于设计人员构建信号完整性模型以

确保应用成功。

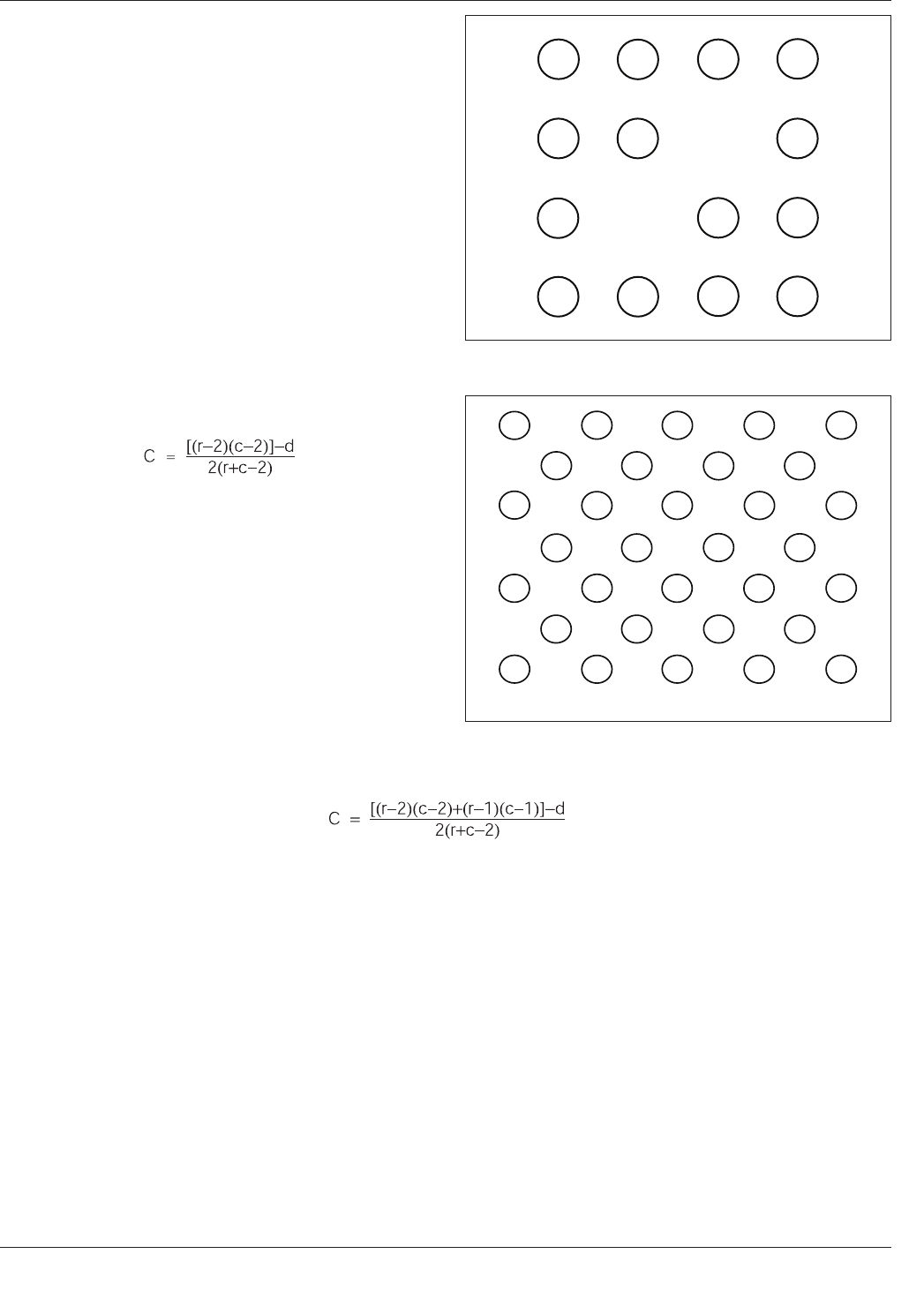

在简单的 r×c 阵列中,每个出口的导体数量 C 可通过

下述关系式给出,式中 r 和 c 分别代表给定阵列的行

数和列数,d 代表阵列的空白位置数。

假使上述等式给出的 C 为整数,则相邻焊球之间每阵

列出口需要容纳 C 条导体。如果 C 为分数,那么一些

出口包含的导体数向下取 C 的整数值,剩余则向上取

C 的整数值。小数部分为出口较低导体数和较高导体

数的比值。

阵列中的焊球也可以散状分布(如对角线阵列)。图 6-17

中为 5×5 散布阵列示例。

下述关系式可用来确定散布阵列中每个出口所含导体

数。

如果 C 为分数,将其向下取整会得到某些相邻焊球间所需布置较少导体数目,若向上取整则可得到剩下的相

邻焊球间所需布置的较大导体数目。小数部分给出了这两个数目所占的比例。

焊料连接盘和导通孔连接盘的尺寸也会影响 BGA 封装的布线能力。1.27mm 节距,大小为 0.8mm 的焊料连

接盘,剩下的连接盘间距仅 0.5mm 可供布线。为了能够在焊料连接盘间布置两条导体,有必要使用规格为

100

μ

m 间距的导体。但是,如果使用大小为 0.6mm 的焊料连接盘,此时在连接盘间可布置间距为 125

μ

m 的

两条导体。

由于密节距 BGA(节距小于等于 1mm)的焊料连接盘间距较小,需要采用较小的导通孔连接盘和钻头尺寸。

随着钻头尺寸减少,印制板最大允许加工厚度也会随之减少。这就迫使设计人员采用较少的层数或者减少层间

的介质厚度。如果使用微导通孔,可能要迫使印制板的外两层作为信号层。

IPC-7095d-6-16-cn

图 6-16 焊球缺失的方形阵列

IPC-7095d-6-17-cn

图 6-17 散布阵列

IPC-7095D-WAM1 CN 2019 年 1 月

68

6.3.1 出线策略

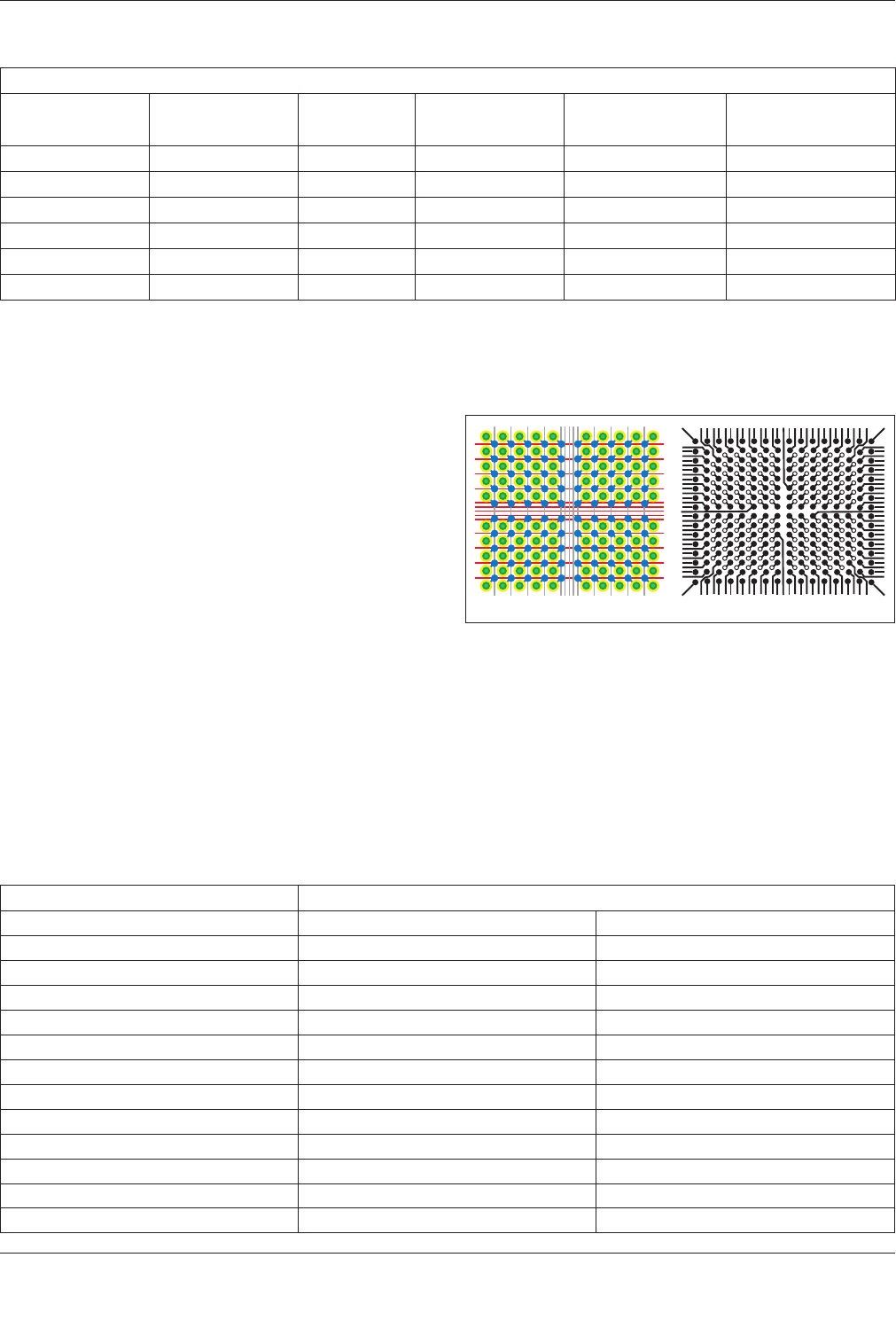

表 6-7 中提供了一些全阵列的出线策略。

表 6-7 全阵列出线策略

全阵列器件

节距(mm)

标称焊球直径

(mm) 表层走线 连接盘至导通孔 连接盘至微导通孔 连接盘中微导通孔

1.27 0.75 Y Y Y Y

1.0 0.45 至 0.63 Y Y Y Y

0.80 0.30 至 0.50 Y Y Y Y

0.75 0.30 至 0.45 N H, S Y Y

0.65 0.30 至 0.40 N N Y Y

0.50 0.30 N N N Y

Y= 是,具有标准印制板制造能力和标准连接盘尺寸

H= 需要较高的印制板制造能力

S= 需要缩减连接盘尺寸

N= 对于业界标准设计及工艺不可行

为适应节距为 0.25mm 的面阵列 I/O 连接盘的倒装芯

片,BGA 基板的正面需要有节距为 0.25mm 的键合连

接盘,反面焊球节距为 1.27mm 或 1.00mm。这些对应

的连接盘必须要通过 BGA 基板(高密度微印制板)线

路和层间导通孔或镀覆孔来互相连接。在 BGA 基板正

面,两个相邻键合连接盘之间可能有必要有一根或多

根互连导体。这样做是为了连接内部多排 I/O 连接盘

至导通孔或镀覆孔,并最终与反面的焊球互连。即便

采用表面再分配层设计,也必须采用非常激进的布线

规则。(见图 6-18)

对于要求有 1,700 引脚的高性能芯片,具有密度极高连线层的 BGA 是必要的。这种 BGA 的本体尺寸将达到

50mm,其中间位置会有焊球空缺。关于节距,该 BGA 基板需要有 1mm 的导通孔和焊球节距,这可适应焊球

分布密度达到每平方厘米 100 个 I/O。

6.3.2 表面导体和间距宽度

表 6-8 和图 6-19 显示了不同阵列节距的大致导体间距和宽度。下列等式可用于

计算大致的导体宽度。

表 6-8 不同阵列节距的导体和间距宽度

导线和间距宽度

节距 (

mm) 单根布线(mm) 两根布线(mm)

1.5 0.248 0.15

1.4 0.231 0.14

1.3 0.215 0.13

1.2 0.198 0.12

1.1 0.182 0.11

1.0 0.165 0.10

0.9 0.149 0.09

0.8 0.132 0.08

0.7 0.116 0.07

0.6 0.099 0.06

0.5 0.083 0.05

0.4 0.066 0.04

IPC-7095d-6-18-cn

图 6-18 导体布线策略