MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS.pdf - 第520页

MIL-STD-883F METHOD 3015.7 22 March 1989 6 NOTES: 1. The c urrent waveforms shown s hall be meas ured as des cri bed in the wavef orm veri fic ation pr ocedure of 3.2, using equi pment meeting t he requir ements of 2. 2.…

MIL-STD-883F

METHOD 3015.7

22 March 1989

5

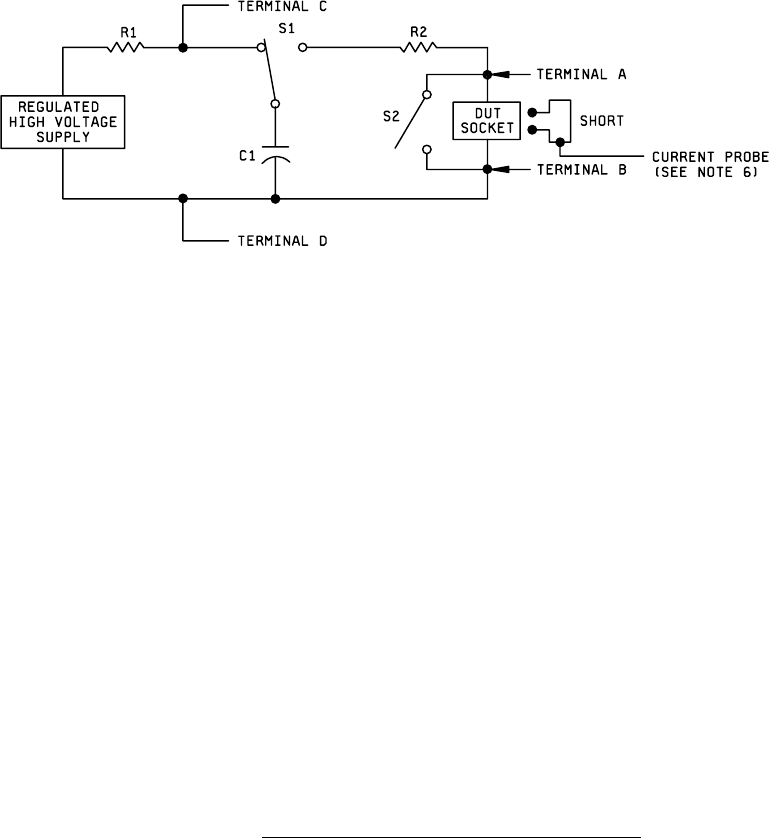

R1 = 10

6

ohms to 10

7

ohms

C1 = 100 picofarads ±10 percent (Insulation resistance 10

12

ohms minimum)

R2 = 1,500 ohms ±1 percent

S1 = High voltage relay (Bounceless, mercury wetted, or equivalent)

S2 = Normally closed switch (Open during discharge pulse and capacitance measurement)

NOTES:

1. The performance of this simulator circuit is strongly influenced by parasitics. Capacitances across relays and

resistor terminals, and series inductance in wiring and in all components shall be minimized.

2. As a precaution against transients upon recharge of C1, the supply voltage V

S

may be reduced before switch

S1 is returned to the charging position.

3. Piggybacking DUT sockets is not permitted during verification or classification testing.

4. Switching terminals A and B internal to the simulator to obtain opposite polarity is not recommended.

5. C1 represents the effective capacitance (see 2.3.2).

6. The current probe connection shall be made with double shielded cable into a 50-ohm termination at the

oscilloscope. The cable length shall not exceed 3 feet.

FIGURE 3015-1. EDS classification test circuit (human body model)

.

MIL-STD-883F

METHOD 3015.7

22 March 1989

6

NOTES:

1. The current waveforms shown shall be measured as described in the waveform verification procedure of 3.2,

using equipment meeting the requirements of 2.

2. The current pulse shall have the following characteristics:

Tri (rise time) ---------------Less than 10 nanoseconds.

Tdi (delay time) ------------150 ±20 nanoseconds.

I

p

(peak current) -----------Within ±10 percent of the I

p

value shown in table II for the voltage step selected.

I

r

(ringing) -------------------The decay shall be smooth, with ringing, break points, double time constants or

discontinuities less than 15 percent I

p

maximum, but not observable 100

nanoseconds after start of the pulse.

FIGURE 3015-2. EDS classification test circuit waveforms (human body model)

.

MIL-STD-883F

METHOD 3016

29 November 1985

1

METHOD 3016

ACTIVATION TIME VERIFICATION

1. PURPOSE

. This method establishes a means for assuring circuit performance during cold temperature start up. It

defines an activation time for digital microelectronic devices such as TTL, DTL, RTL, ECL, and MOS and establishes the

procedure necessary to accomplish the required testing. This method will ensure that a specified capability is available a

known time interval after application of power.

1.1 Definitions

. The following definitions shall apply for the purposes of this test method:

a. Activation time. Activation time is defined as the time required for a device to become functionally operable after

initial power is applied at the operating temperature extremes as specified by the applicable acquisition document.

Note that activation time may be due to device and test system limitations, or both.

b. Maximum and minimum. Maximum and minimum refer to an algebraic system where "max" represents the most

positive value of the range and "min" represents the least positive value of the range. This is consistent with

MIL-STD-1331, 30.1 and 30.2 for logic levels only.

c. Maximum operating frequency. Maximum operating frequency is defined as the frequency of operation resulting

from use of the minimum clock period for devices requiring a clock, or the frequency of operation resulting from the

use of the minimum cycle time for devices not requiring a clock (such as memory devices) as specified in the

applicable acquisition document.

1.2 Symbols

. The following symbols and definitions shall apply for the purposes of this method.

1.2.1 Logic levels

.

a. V

LW

= worst case nominal low level logic input. The maximum allowable V

IL

specified in the applicable acquisition

document minus 100 millivolts to allow for uncertainty in the drive level capability of high speed functional test

equipment. (V

LW

= V

IL

(max) - 100 mV).

b. V

HW

= worst case nominal high level logic input. The minimum allowable V

IH

as specified by the applicable

acquisition document plus 100 millivolts (V

HW

= V

IH

(min) + 100 mV).

c. V

OH

(min) = minimum output high level specified for a digital microelectronic device.

d. V

OL

(max) = maximum output low level specified for a digital microelectronic device.

1.2.2 Activation times

.

a. t

AH

= maximum allowable activation time requirement, measured at V

CC

(max).

b. t

AL

= maximum allowable activation time requirement, measured at V

CC

(min).

2. APPARATUS

. An instrument shall be provided which has the capability of applying sequential logic patterns to the

device under test in accordance with the applicable acquisition document. The test instrument shall also be capable of

applying nominal power supply voltage(s) and monitoring the output for the specified logic levels. The output monitoring

circuit shall be of the double comparator type. The threshold voltage (trip point) for a comparator shall be V

OL

(max) and V

OH

(min) as specified in the applicable acquisition document. The test chamber shall be capable of maintaining the device

under test at any specified test temperature.

3. PROCEDURE.

The device shall be thermally stabilized at the minimum specified test temperature with no power

applied to the device. The specified power supply voltage and the specified input logic patterns using V

LW

and V

HW

input

voltage levels shall then be applied to the device under test and the outputs shall be monitored as described in section 2.

This functional test shall be performed at a speed of at least 75 percent of F(max) using a test vector pattern as called out in

the applicable acquisition document that has been designed for maximum fault coverage with no more than 4 K vectors.