MIL- STD-883F 2004 TEST METHOD STANDARD MICROCIRCUITS.pdf - 第637页

MIL-STD-883F METHOD 5007.6 19 August 1994 1 METHOD 5007.6 W AFER LOT ACCEPTANCE 1. PURPOSE . This method est ablis hes the r equirements for the lot ac ceptanc e tes ting of mi croc irc uit waf ers i ntended for class le…

MIL-STD-883F

METHOD 5006

20 November 1969

4

4. SUMMARY. The following details shall be specified in the applicable acquisition document:

a. Test condition letter (see 3.1 and 3.2).

b. Test sequence and sample quantities if other than specified (see 3.1 and 3.2).

c. Failure analysis procedures and test condition, if other than specified (see 3.1 and 3.2).

d. For test condition B, the test conditions and stress levels, where applicable (see 3.2).

e. Percent failure for test termination, if other than specified (see 3.1 and 3.2).

f. Requirements for Limit Test Plan and data reporting (see 3.3).

MIL-STD-883F

METHOD 5007.6

19 August 1994

1

METHOD 5007.6

WAFER LOT ACCEPTANCE

1. PURPOSE

. This method establishes the requirements for the lot acceptance testing of microcircuit wafers intended for

class level S use.

2. APPARATUS

. The apparatus used shall be in accordance with the apparatus requirements of the methods specified

in the conditions column of table I.

3. PROCEDURE

. The performance of the wafer lot acceptance tests shall be in accordance with the conditions specified

in table I. If a lot fails a test under the sampling plan, as an alternative to rejecting the entire lot, the manufacturer may elect

to test each wafer in the lot for that parameter(s). All wafers successfully passing the test(s) shall be considered the lot for

the remainder of the tests. All wafers failing any test shall be removed from the lot. Data obtained from all tests shall be

recorded. The sequence of the tests in table I does not have to be adhered to, however, the tests must be performed at the

point in the processing (if specified) required in the conditions column of table I. Where limits are based on tolerances about

an "approved design nominal", the nominal shall be stated in the maintenance plan submitted for approval to the qualifying

or acquiring activity. Where table I limits are based on tolerances about the "mean", the mean shall be determined initially

on measurements from a minimum of five lots and the mean shall be stated in the maintenance plan submitted for approval

to the qualifying or acquiring activity. In no case shall the "design nominal" or "mean" exceed the absolute limits specified in

table I.

4. SUMMARY

. The following detail shall be specified in the applicable device specification:

Requirements or limits if other than those on table I.

MIL-STD-883F

METHOD 5007.6

19 August 1994

2

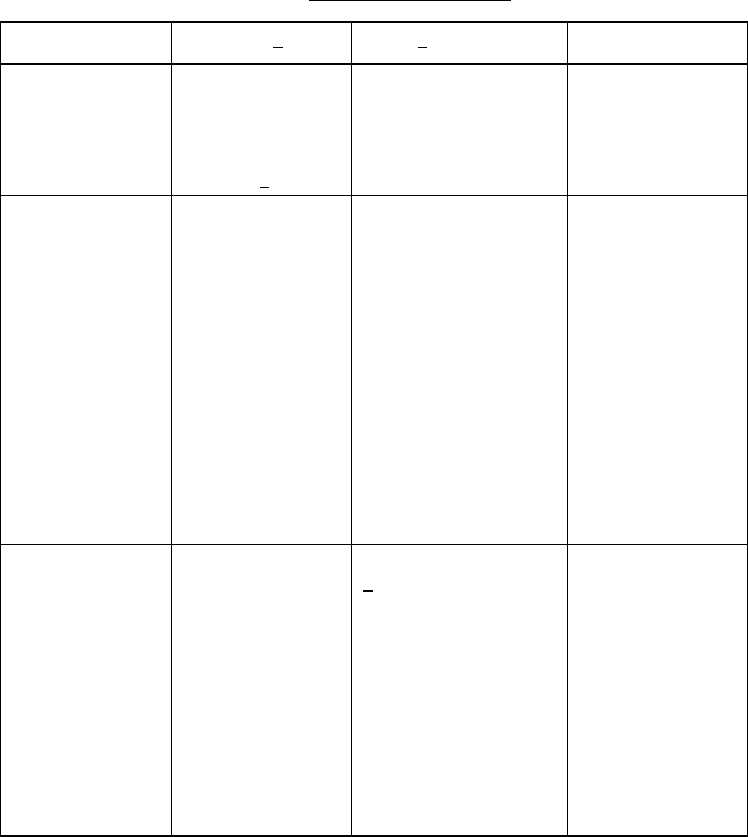

TABLE I. Wafer lot acceptance tests.

Test

Conditions 1/ Limits 3/ Sampling plan

1. Wafer thickness Measurement

shall be performed

after final lap

or polish. All

readings shall be

recorded. 2

/

Maximum deviation of

±2 mil from approved

design nominal 6 mil

minimum.

Two wafers per

lot. Reject lot

if any measurement

exceeds limits or

revert to test of

each wafer.

2. Metallization

thickness

All readings

shall be

recorded.

a. Conductor: 8 kÅ

minimum for single

level metal and for

the top level of

multi-level metal;

5 kÅ minimum for lower

levels, with a maximum

deviation of ±20

percent from the

approved design

nominal.

b. Barrier: Maximum

deviation of ±30

percent from the

approved design

nominal.

One wafer (or

monitor) per lot.

Reject lot if

measurement ex-

ceeds limits or

revert to test

of each wafer.

3. Thermal sta-

bility (ap-

plicable to:

All linear;

all MOS; all

bipolar digi-

tal operating

at 10 V or

more)

Record V

FB

or V

T

.

a. ∆V

FB

or ∆V

T

<

0.75, normalized to

an oxide thickness of

1000Å for bipolar

digital devices oper-

ating at 10 volts or

greater and all

bipolar linear devices

not containing MOS

transistor(s). The

monitor shall have an

oxide and shall be

metallized with the

lot.

One wafer (or

monitor) per lot.

Reject lot if

measurement ex-

ceeds limits or

revert to test

of each wafer.

See footnotes at end of table.