IPC-SM-782A 表面安装设计和焊盘设计标准(带BGA).pdf - 第78页

6.0 TOLERANCE AND SOLDER JOINT ANALYSIS Figure 4 provides an analysis of tolerance assumptions and resultant solder joints based on the land pattern dimensions shown in Figure 3. Tolerances for the component dimensions, …

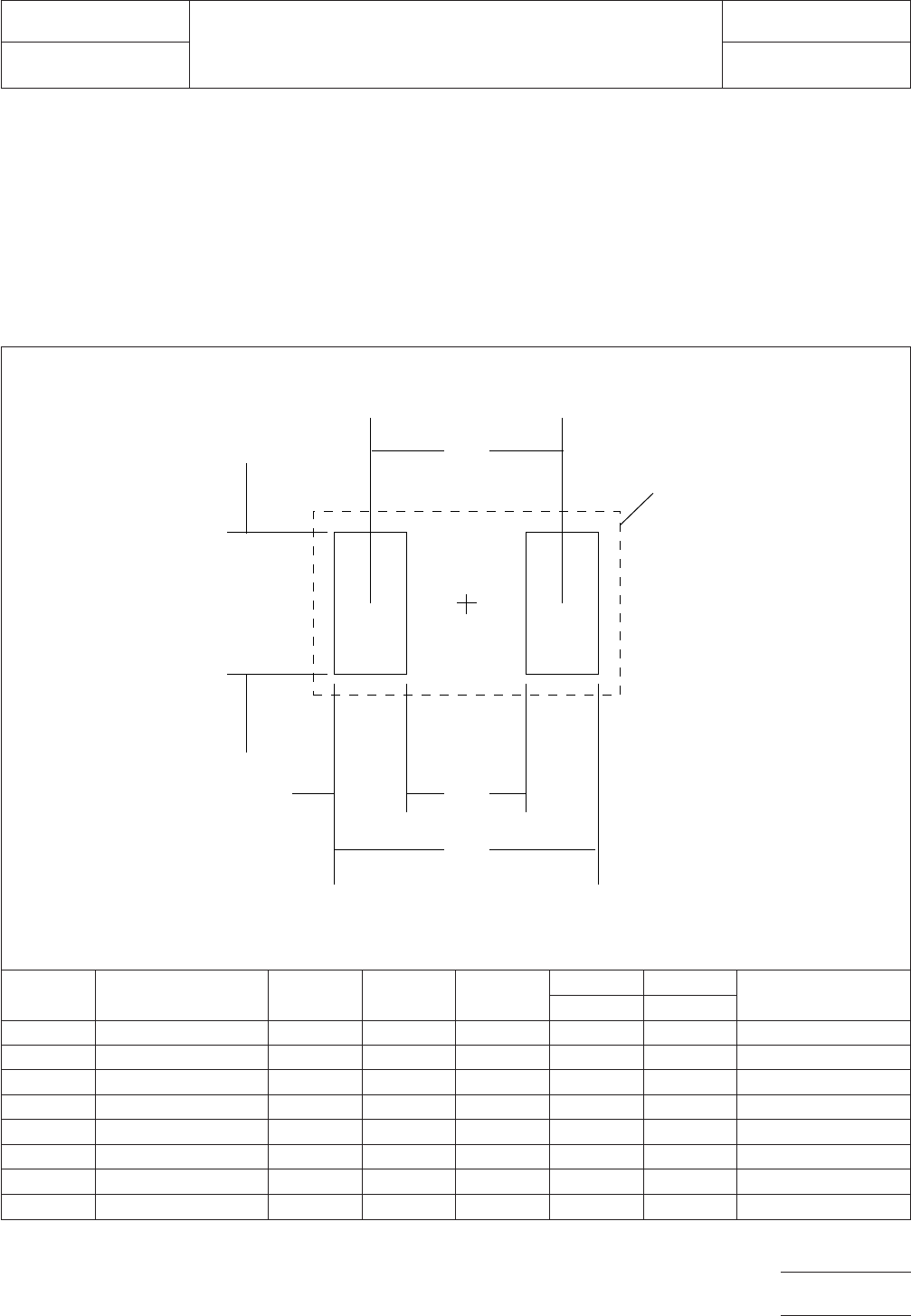

5.0 LAND PATTERN DIMENSIONS

Figure 3 provides the land pattern dimensions for chip capaci-

tors. These numbers represent industry consensus on the

best dimensions based on empirical knowledge of fabricated

land patterns.

In the table, the dimensions shown are at maximum material

condition (MMC). The least material condition (LMC) should

not exceed the fabrication (F) allowance shown on page 4.

The LMC and the MMC provide the limits for each dimension.

The dotted line in Figure 3 shows the grid placement court-

yard which is the area required to place land patterns and

their respective components in adjacent proximity without

interference or shorting. Numbers in the table represent the

number of grid elements (each element is 0.5 by 0.5 mm) in

accordance with the international grid detailed in IEC publica-

tion 97.

RLP No.

Component Identifier

(mm) [in] Z (mm) G (mm) X (mm)

YC

Placement Grid

(No. of Grid elements)ref ref

130A 1005 [0402] 2.20 0.40 0.70 0.90 1.30 2x6

131A 1310 [0504] 2.40 0.40 1.30 1.00 1.40 4x6

132A 1608 [0603] 2.80 0.60 1.00 1.10 1.70 4x6

133A 2012 [0805] 3.20 0.60 1.50 1.30 1.90 4x8

134A 3216 [1206] 4.40 1.20 1.80 1.60 2.80 4x10

135A 3225 [1210] 4.40 1.20 2.70 1.60 2.80 6x10

136A 4532 [1812] 5.80 2.00 3.40 1.90 3.90 8x12

137A 4564 [1825] 5.80 2.00 6.80 1.90 3.90 14x12

Figure 3 Chip capacitor land pattern dimensions

▼

▼

▼

▼

▼

▼

▼

▼

▼

C

G

Z

X

Y

Grid

placement

courtyard

▼

IPC-782-8-2-3

IPC-SM-782

Subject

Chip Capacitors

Date

5/96

Section

8.2

Revision

A

Page3of4

电子技术应用 www.ChinaAET.com

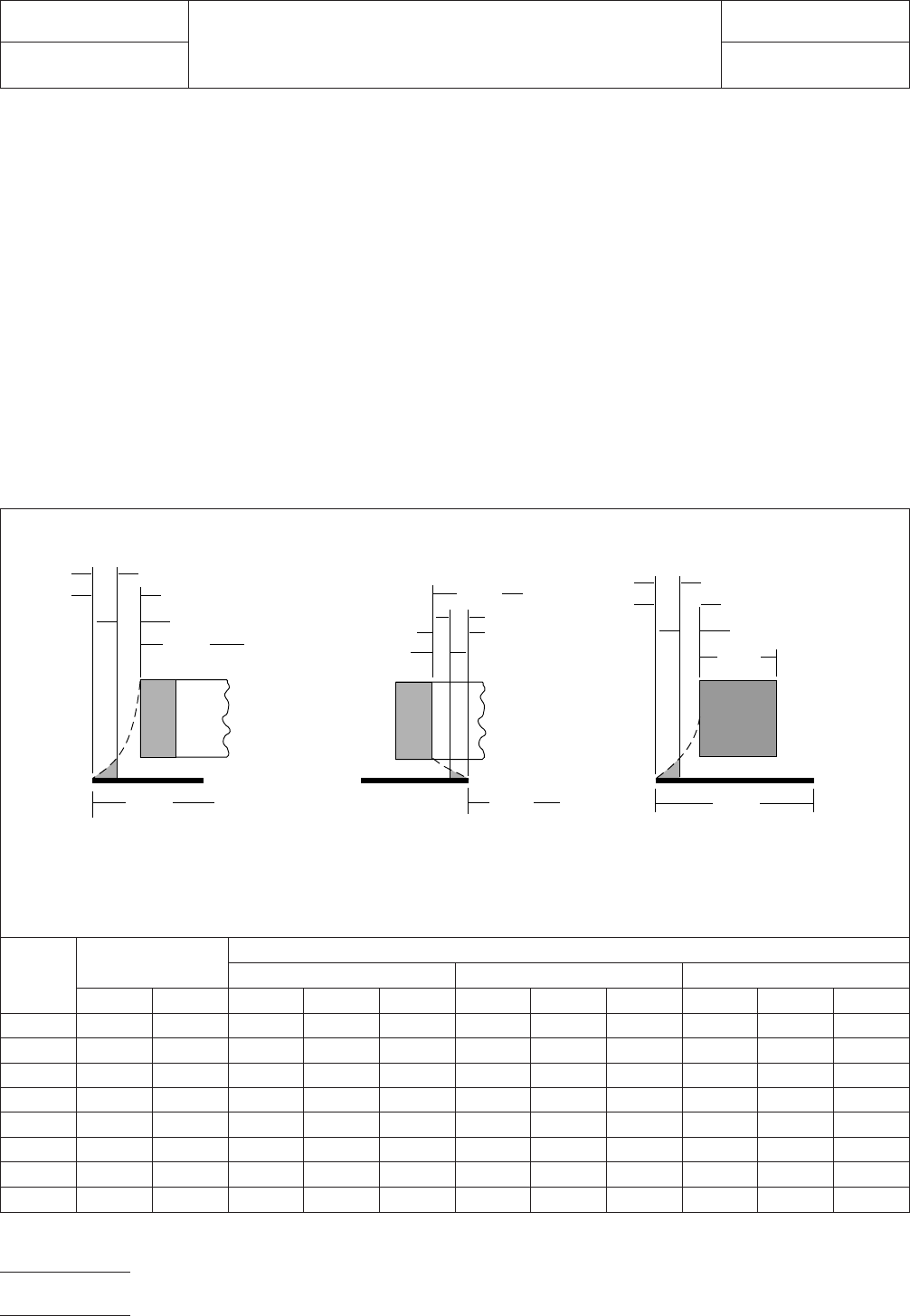

6.0 TOLERANCE AND SOLDER JOINT ANALYSIS

Figure 4 provides an analysis of tolerance assumptions and

resultant solder joints based on the land pattern dimensions

shown in Figure 3. Tolerances for the component dimensions,

the land pattern dimensions (fabrication tolerances on the

interconnecting substrate), and the component placement

equipment accuracy are all taken into consideration.

Figure 4 provides the solder joint minimums for toe, heel, and

side fillets, as discussed in Section 3.3. The tolerances are

addressed in a statistical mode, and assume even distribution

of the tolerances for component, fabrication, and placement

accuracy.

Individual tolerances for fabrication (‘‘F’’) and component

placement equipment accuracy (‘‘P’’) are assumed to be as

given in the table. These numbers may be modified based on

user equipment capability or fabrication criteria. Component

tolerance ranges (C

L

,C

S

, and C

W

) are derived by subtracting

minimum from maximum dimensions given in Figure 2. The

user may also modify these numbers, based on experience

with their suppliers. Modification of tolerances may result in

alternate land patterns (patterns with dimensions other than

the IPC registered land pattern dimensions).

The dimensions for minimum solder fillets at the toe, heel, or

side (J

T

,J

H

,J

S

) have been determined based on industry

empirical knowledge and reliability testing. Solder joint

strength is greatly determined by solder volume. An observ-

able solder fillet is necessary for evidence of proper wetting.

Thus, the values in the table usually provide for a positive sol-

der fillet. Nevertheless, the user may increase or decrease the

minimum value based on process capability.

RLP No.

Tolerance

Assumptions (mm)

Solder Joint

Toe (mm) Heel (mm) Side (mm)

FPC

L

J

Tmin

J

Tmax

C

s

J

Hmin

J

Hmax

C

W

J

Smin

J

Smax

130A 0.10 0.10 0.20 0.53 0.65 0.60 –0.06 0.12 0.20 0.03 0.15

131A 0.10 0.10 0.30 0.52 0.69 1.00 –0.08 0.16 0.50 0.01 0.27

132A 0.10 0.10 0.30 0.51 0.68 0.65 –0.08 0.18 0.30 0.01 0.18

133A 0.10 0.10 0.40 0.49 0.70 0.95 –0.16 0.26 0.40 0.01 0.23

134A 0.10 0.10 0.40 0.49 0.70 1.40 0.14 0.56 0.40 –0.01 0.20

135A 0.10 0.10 0.40 0.49 0.70 1.40 0.14 0.56 0.40 –0.01 0.20

136A 0.10 0.10 0.60 0.49 0.80 1.10 0.15 0.73 0.40 –0.01 0.20

137A 0.10 0.10 0.60 0.49 0.80 1.10 0.15 0.73 0.80 –0.01 0.40

Figure 4 Tolerance and solder joint analysis

Wmin

Lmin

▼

▼

Zmax

▼

▼

1

/2 T

T

J

T

min

Zmax = Lmin + 2J

T

min + T

T

Where:

J

T

min = Minimum toe fillet

T

T

= Combined tolerances

at toe fillet

Smax

J

H

min

Gmin = Smax - 2J

H

min - T

H

Where:

J

H

min = Minimum heel fillet

T

H

= Combined tolerances

at heel fillet

1

/2 T

H

Xmax

Xmax = Wmin + 2J

S

min + T

S

Where:

J

S

min = Minimum side fillet

T

S

= Combined tolerances

at side fillet

▼

▼

Toe Fillet

1

/2 T

S

▼

▼

▼

Heel Fillet Side Fillet

▼

▼

▼

▼

▼

J

T

max

J

H

max

J

S

max

J

S

min

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

Gmin

▼

▼

IPC-782-8-2-4

IPC-SM-782

Subject

Chip Capacitors

Date

5/96

Section

8.2

Revision

A

Page4of4

电子技术应用 www.ChinaAET.com

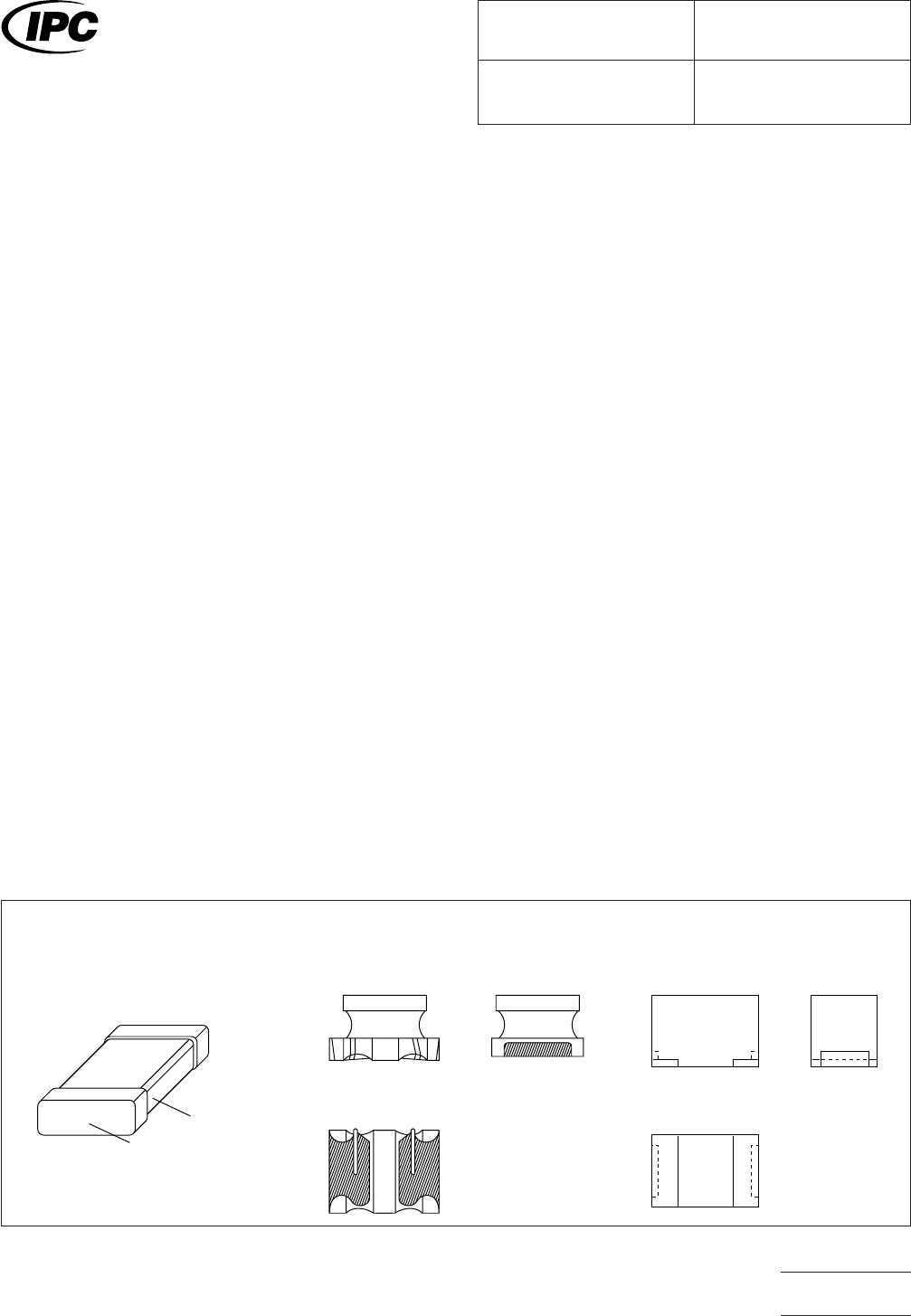

1.0 SCOPE

Microminiature leadless devices are available to the circuit

designer in rectangular form for discrete components such as

inductors.

This subsection provides the component and land pattern

dimensions for inductors, along with an analysis of tolerance

and solder joint assumptions used to arrive at the land pattern

dimensions. Basic construction of the inductor is also cov-

ered.

2.0 APPLICABLE DOCUMENTS

See Section 8.0 for documents applicable to the subsections.

3.0 COMPONENT DESCRIPTIONS

A variety of values exist for inductors. The following sections

describe the most common types.

3.1 Basic Construction

At the time of publication, there

was no industry standard document for leadless inductors.

The dimensions were taken from manufacturer’s catalogs, but

only when at least two component vendors manufacture the

same package. However, the same inductor value may not be

available in the same package from the two manufacturers.

See Figure 1.

3.1.1 Termination Materials

End terminations should be

solder coated with a tin/lead alloy. The solder should contain

between 58 to 68% tin. Solder may be applied to the termi-

nation by hot dipping or by plating from solution. Plated sol-

der

terminations should be subjected to a post-plating reflow

operation to fuse the solder. The tin/lead finish should be at

least 0.0075 mm [0.0003 in] thick.

The termination shall be symmetrical, and shall not have nod-

ules lumps, protrusions, etc., that compromise the symmetry

or dimensional tolerances of the part. The end termination

shall cover the ends of the components, and shall extend out

to the top and bottom of the component.

Most common termination materials include palladium-silver

alloy, silver, and gold. Solder finish applied over precious

metal electrodes shall have a diffusion-barrier layer between

the electrode metallization and the solder finish. The barrier

layer should be nickel or an equivalent diffusion barrier, and

should be at least 0.00125 mm [0.00005 in] thick.

3.1.2 Marking

Parts are available with or without marked

inductance values.

3.1.3 Carrier Package Format

Bulk rods, 8 mm tape/4

mm pitch is preferred for best handling. Tape and reel speci-

fications provide additional requirements.

3.1.4 Resistance to Soldering

Parts should be capable of

withstanding five cycles through a standard reflow system

operating at 215°C. Each cycle shall consist of 60 seconds

exposure at 215°C. Parts must also be capable of withstand-

ing a minimum of 10 seconds immersion in molten solder at

260°C.

IPC-782-8-3-1

Figure 1 Inductor construction

Ferrite

Chip

▼

Precision wire—wound Molded

External electrode

▼

IPC-SM-782

Surface Mount Design

and Land Pattern Standard

Date

8/93

Section

8.3

Revision Subject

Inductors

Page1of4

电子技术应用 www.ChinaAET.com