IPC-SM-782A 表面安装设计和焊盘设计标准(带BGA).pdf - 第92页

4.0 COMPONENT DIMENSIONS Figure 2 provides the component dimensions for SOT 23 components. Component Identifier L (mm) S (mm) W (mm) T (mm) H (mm) P (mm) min max min max min max min max max nom SOT 23 2.30 2.60 1.10 1.47 …

1.0 SCOPE

This subsection provides the component and land pattern

dimensions for SOT 23 (small outline transistor) components.

Basic construction of the SOT 23 device is also covered. At

the end of this subsection is a listing of the tolerances and

target solder joint dimensions used to arrive at the land pat-

tern dimensions.

2.0 APPLICABLE DOCUMENTS

See Section 8.0 for documents applicable to the subsections.

3.0 COMPONENT DESCRIPTIONS

One of the first active devices in packaged form for surface

mounting was the SOT device. Plastic encapsulated three ter-

minal devices with leads formed out from the body were sur-

face mounted to overcome some of the problems and difficul-

ties in handling dip transistors. In general, SOT packages are

used with diodes, transistors, and small I/O devices.

The SOT 23 package is the most common three-lead surface

mount configuration.

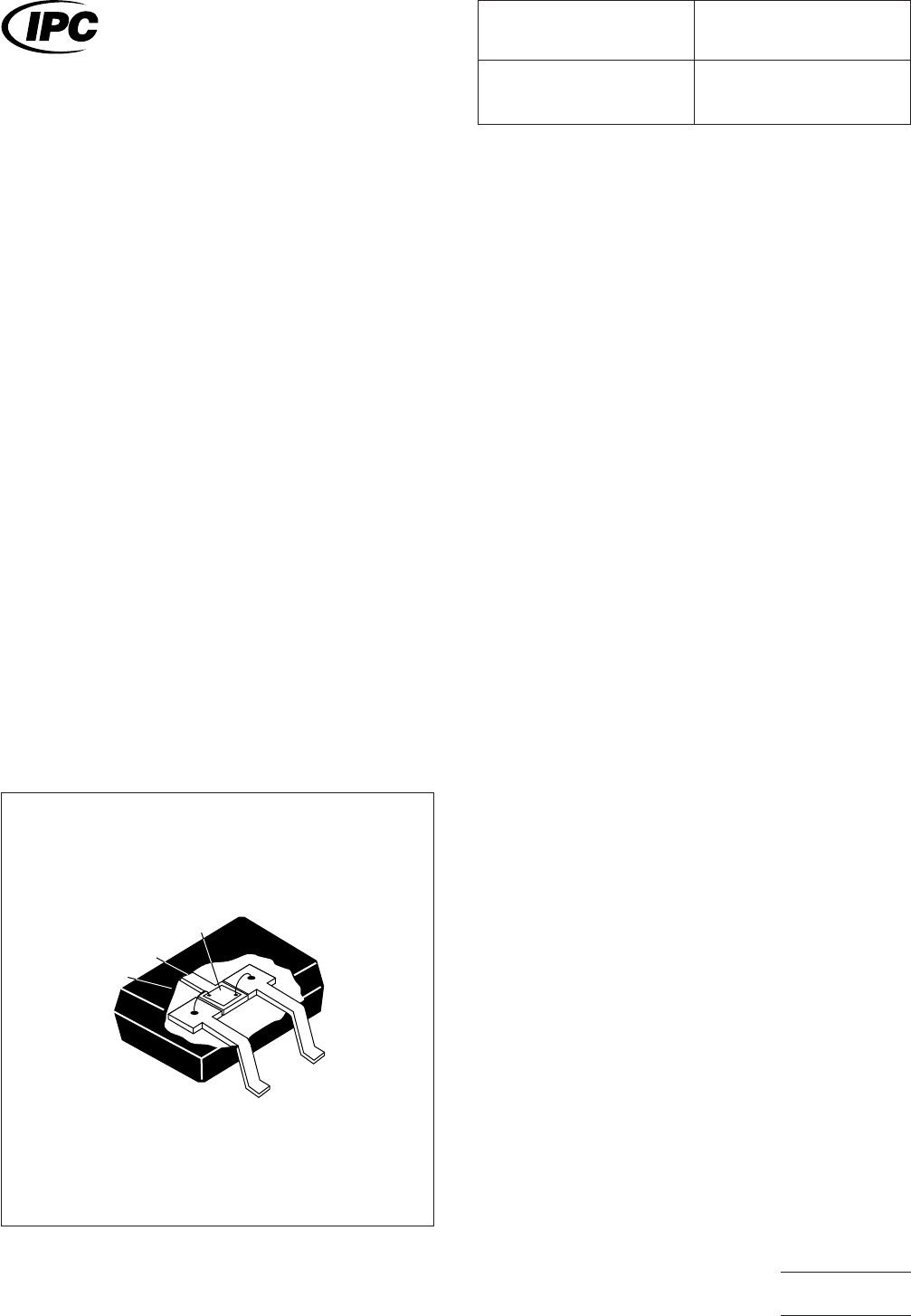

3.1 Basic Construction

The SOT 23 package has had

several redesigns to meet the needs of both hybrid and

printed board surface mount industries. These changes

resulted in low, medium and high profile characteristics which

basically reflect the clearance that the body is from the mount-

ing surface. See Figure 1 for construction characteristics and

Figure 2 for dimensions.

3.1.1 Termination Materials

Leads should be solder-

coated with a tin/lead alloy. The solder should contain

between 58 to 68% tin. Solder may be applied to the leads by

hot dipping or by plating from solution. Plated solder termina-

tions should be subjected to post-plating reflow operation to

fuse the solder. The tin/lead finish should be at least 0.0075

mm [0.0003 in] thick.

Solder finish applied over precious metal electrodes should

have a diffusion barrier layer between the electrode metalliza-

tion and the solder finish. The barrier layer should be nickel or

an equivalent diffusion barrier, and should be at least 0.00125

mm [0.00005 in] thick.

3.1.2 Marking

Parts are available with or without marked

values.

3.1.3 Carrier Package Format

Carrier package format

shall be according to the following: body type TO-236, 8 mm

tape/4 mm pitch.

3.1.4 Resistance to Soldering

Parts should be capable of

withstanding five cycles through a standard reflow system

operating at 215°C. Each cycle shall consist of 60 seconds

exposure at 215°C. Parts must also be capable of withstand-

ing a minimum of 10 seconds immersion in molten solder at

260°C.

IPC-782-8-6-1

Figure 1 SOT 23 construction

Passivated

Semiconductor Chip

Collector lead

Bonding wire

Epoxy body

Emitter lead

Base lead

IPC-SM-782

Surface Mount Design

and Land Pattern Standard

Date

8/93

Section

8.6

Revision Subject

SOT 23

Page1of4

电子技术应用 www.ChinaAET.com

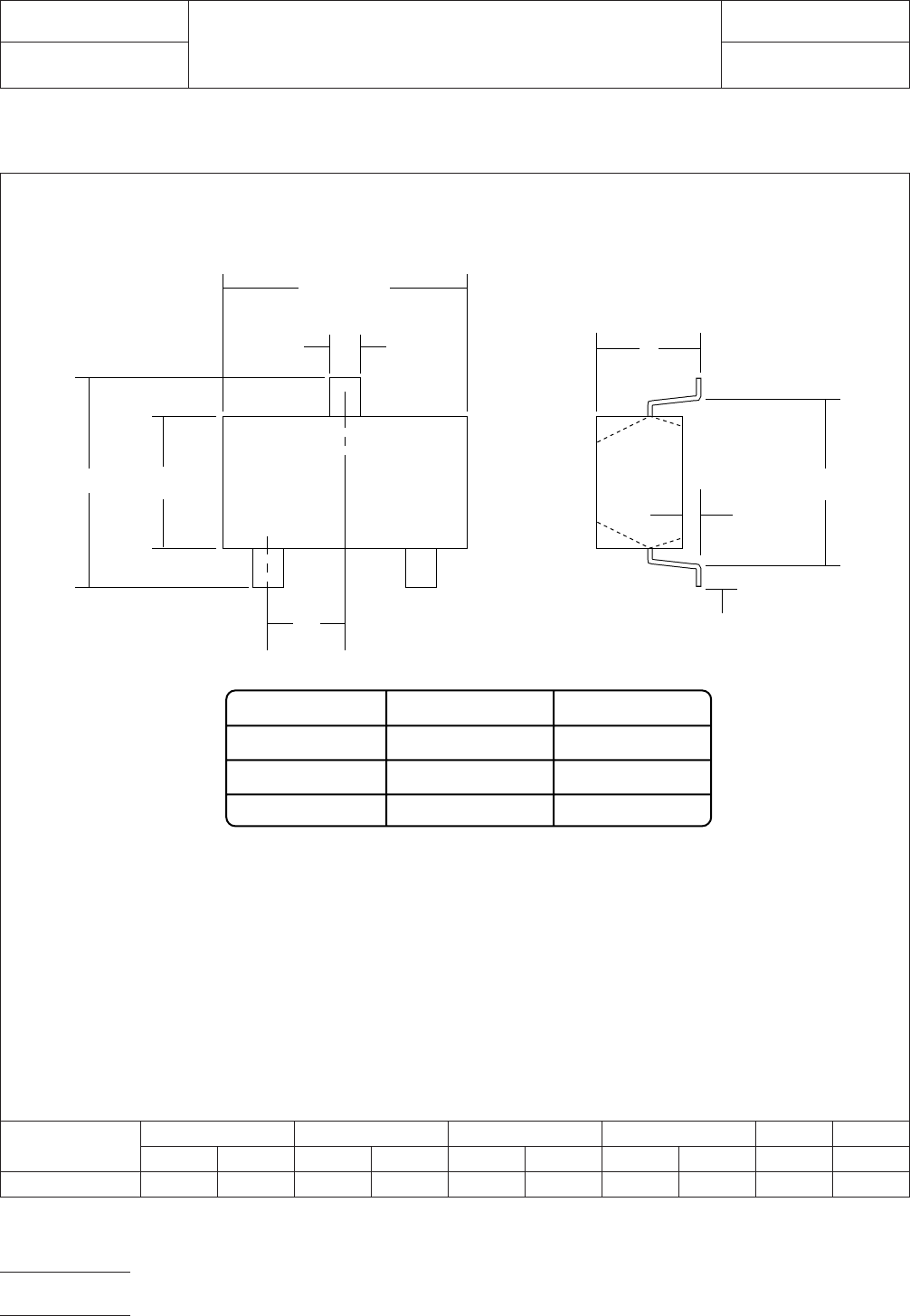

4.0 COMPONENT DIMENSIONS

Figure 2 provides the component dimensions for SOT 23 components.

Component

Identifier

L (mm) S (mm) W (mm) T (mm) H (mm) P (mm)

min max min max min max min max max nom

SOT 23 2.30 2.60 1.10 1.47 0.36 0.46 0.45 0.60 1.10 0.95

Figure 2 SOT 23 component dimensions

2.80–3.00

W

L

P

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

H

S

T

▼

▼

See profile

table

Profile Dimension TO 236 Des

Low 0.01–0.10 AB

Medium 0.08–0.13 ——

High 0.1–0.25 AA

1.20–1.40

Dimensions are in millimeters

IPC-782-8-6-2

IPC-SM-782

Subject

SOT 23

Date

8/93

Section

8.6

Revision

Page2of4

电子技术应用 www.ChinaAET.com

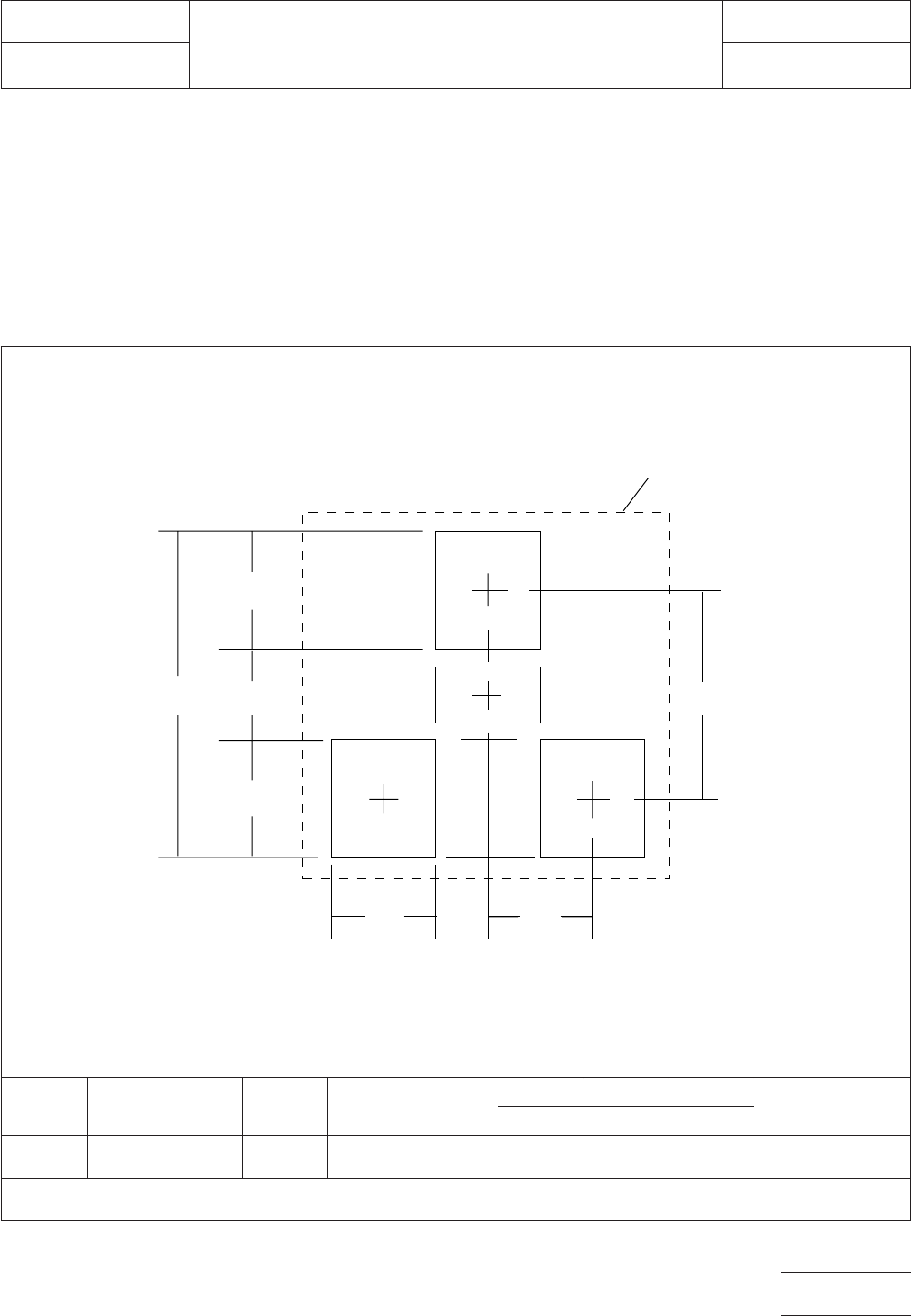

5.0 LAND PATTERN DIMENSIONS

Figure 3 provides the land pattern dimensions for SOT 23

components. These numbers represent industry consensus

on the best dimensions based on empirical knowledge of fab-

ricated land patterns.

In the table, the dimensions shown are at maximum material

condition (MMC). The least material condition (LMC) should

not exceed the fabrication (F) allowance shown on page 4.

The LMC and the MMC provide the limits for each dimension.

The dotted line in Figure 3 shows the grid placement court-

yard which is the area required to place land patterns and

their respective components in adjacent proximity without

interference or shorting. Numbers in the table represent the

number of grid elements (each element is 0.5 by 0.5 mm) in

accordance with the international grid detailed in IEC publica-

tion 97.

RLP No.

Component

Identifier Z (mm) G (mm) X (mm)

Y (mm) C (mm) E (mm)

Placement Grid

(No. of Grid

Elements)ref ref ref

210 SOT 23

(reflow solder)

3.60 0.80 1.00 1.40 2.20 0.95 8x8

*Note: If a more robust pattern is desired for wave soldering, add 0.2 mm to ‘‘Z’’ and identify as RLP 210W.

Figure 3 SOT 23 land pattern dimensions

ZG

Y

Y

C

▼▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

▼

E

X

▼

▼

Grid placement courtyard

▼

IPC-782-8-6-3

IPC-SM-782

Subject

SOT 23

Date

8/93

Section

8.6

Revision

Page3of4

电子技术应用 www.ChinaAET.com