IPC-CM-770D-1996.pdf - 第57页

January 1996 IPC-CM-770 IPC-I- Figure 12-4 Double Row Plastic Chip Carrier ADEQUATE GOOD SOLDER FILLET A LINE PARALLEL Il TO CHIP CARRIER II SOLDER FILLET INSUFFICIENT LEAD CENTERED ON GOOD SOLDER FILLET CHIP CARRIER TER…

IPC-CM-770 Januaty 1996

close tolerances make these packages particularly adapt-

able to automatic assembly, testing and handling equip-

ment.

The conductors consist of clad copper which is electro-

plated with copper to

0.005

mm, then electroplated with

nickel to 0.000125-0.00025 mm and finally electroplated

with gold to

0.00005-0.0001

mm. This combination of met-

allization provides an excellent base for automatic wire

bonding in the cavity area, and yet does not put enough

gold on the footprint to embrittle the solder joint.

12.1.3 Package Materials and Construction

Chip carri-

ers are available in many constructions and materials com-

parable to dual-inline-packages (DIPs).

Plastic premolded chip carriers, recommended primarily

for commercial application, have the advantages and draw-

backs of a plastic DIP: Low cost, nonhermetic, 0°C to

70°C operating temperature range (sometimes, -25°C to

85”C), and nominal environment protection.

Glass-frit sealed chip carriers are similar in construction to

ceramic DIPs (Cerdips). They are hermetic and are envi-

ronmentally testable, costing more than the plastic con-

struction but less than the solder-sealed carrier. They are

candidates for some high-reliability packaging applica-

tions, but some require special handling to avoid damage to

the package. Solder-sealed 3-layer chip carriers are equiva-

lent of solder- sealed DIPs. These hermetic devices are the

most expensive chip carrier because of high gold content.

However, seal temperature is lower than that of the lower

cost Cerdip-type, and the package accepts all high-

reliability processing required for MIL-M-385

10.

12.1.3.1 Plastic Package Chip Carrier

There are two

types of plastic chip carriers: premolded and postmolded.

Both types are composite metaUdielectric assemblies that

include a conductor lead frame and a molded insulating

body. The premolded chip carrier has one or more aper-

tures for mounting microelectronic elements, while the

postmolded chip carrier is a complete assembly without

apertures. All necessary plating operations are performed

by the package manufacturer to eliminate plating or tinning

by the user.

12.1.3.2 Ceramic Package Chip Carrier

The ceramic

chip carrier is usually constructed from a 90% to 96% alu-

mina or beryllia base, using a single layer or multilayer

cofired metallization process originally developed for the

DIP. The metallization is generally a trimetal combination

of a refractory metal (such as tungsten or molybdenum),

nickel and gold.

12.1.4 Type Designations

The 50-mil center and 40-mil

center chip carrier standard families have the JEDEC des-

ignations shown in Table 12-3 (from JEDEC 95-83).

Table 12-3 JEDEC Designations

Type

Designation Description

MS002

1.27mm [0.050”] center, leaded Type A-24 MS006

1.27mm [0.050”] center, leadless Type

D

MS005

1.27mm [0.050”] center, leadless Type C MS004

1.27mm [0.050”] center, leadless Type

B

MS003

1.27mm [0.050”] center, leadless Tape A

MS007 1.27 mm [0.050”] center, leaded Type A

MS008 1.27 mm [0.050”] center, leaded type

B

MS009 1 .O2 mm [0.040”] center, packages

terminal

12.1.5 Component Considerations

Direct-soldered

leadless ceramic chip carriers exhibit lower junction to

board thermal resistance as compared to leaded chip carri-

ers. However, the rigid interface is more susceptible to sol-

der joint cracking due to thermal expansion mismatch

between the component packages and the substrate.

The compliant leads of the leaded packages are designed to

absorb thermally induced stress. Copper alloy leads with

thermal and electrical conductivity higher than used for

DIPs are used in some leaded plastic chip carriers to facili-

tate lead forming and thermal coupling to the substrate.

Component packages with the cavity up (i.e., with the heat-

radiating surface adjacent to the substrate) are typically

chosen for military systems in which a substrate is cooled

by conduction to the assembly structure.

12.2 Through-Hole Mounting

In general through-hole

mounting does not apply to chip carriers. However, in

some cases leaded chip carriers utilize clip type leads

designed for through-hole mounting. Characterization of

issues related to mounting of these devices

so

configured is

similar to considerations in Sections

10

and

11.

Leaded-type A and all leadless-type chip carriers can be

interconnected to the printed board using through-hole

mounted sockets. There are some advantages to this

approach including simplified replacement of the chip in

the event failure or design change and reduced exposure of

the chip to damage during assembly and soldering.

12.3 Surface Mounting

12.3.1 Component Preparation

12.3.1.1 Metallurgical Considerations

The general

requirement for cleanliness and solderability of termina-

tions on all components is of utmost importance in the case

of both leadless and leaded chip carriers since inspection,

repair and rework of soldered surface mount component

assemblies is in general more complex than that for

through-hole mounted components. Frequent socketing of

3

-20

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

January

1996

IPC-CM-770

IPC-I-

Figure 12-4 Double

Row

Plastic Chip Carrier

ADEQUATE

GOOD SOLDER FILLET

A

LINE PARALLEL

Il

TO CHIP CARRIER

II

SOLDER FILLET

INSUFFICIENT

LEAD CENTERED ON

GOOD SOLDER FILLET

CHIP CARRIER TERMINAL AND CHIP CARRIER TERMINAL AND

LEAD

OVERHANGS

LEAD ALIGNED FLUSH

TO

\

SOLDER

oN

CHIP CARRIER TERMINAL

\\

ONE EDGE ONLY

PREFERRED ACCEPTABLE NOT PREFERRED

IPC-1-00223

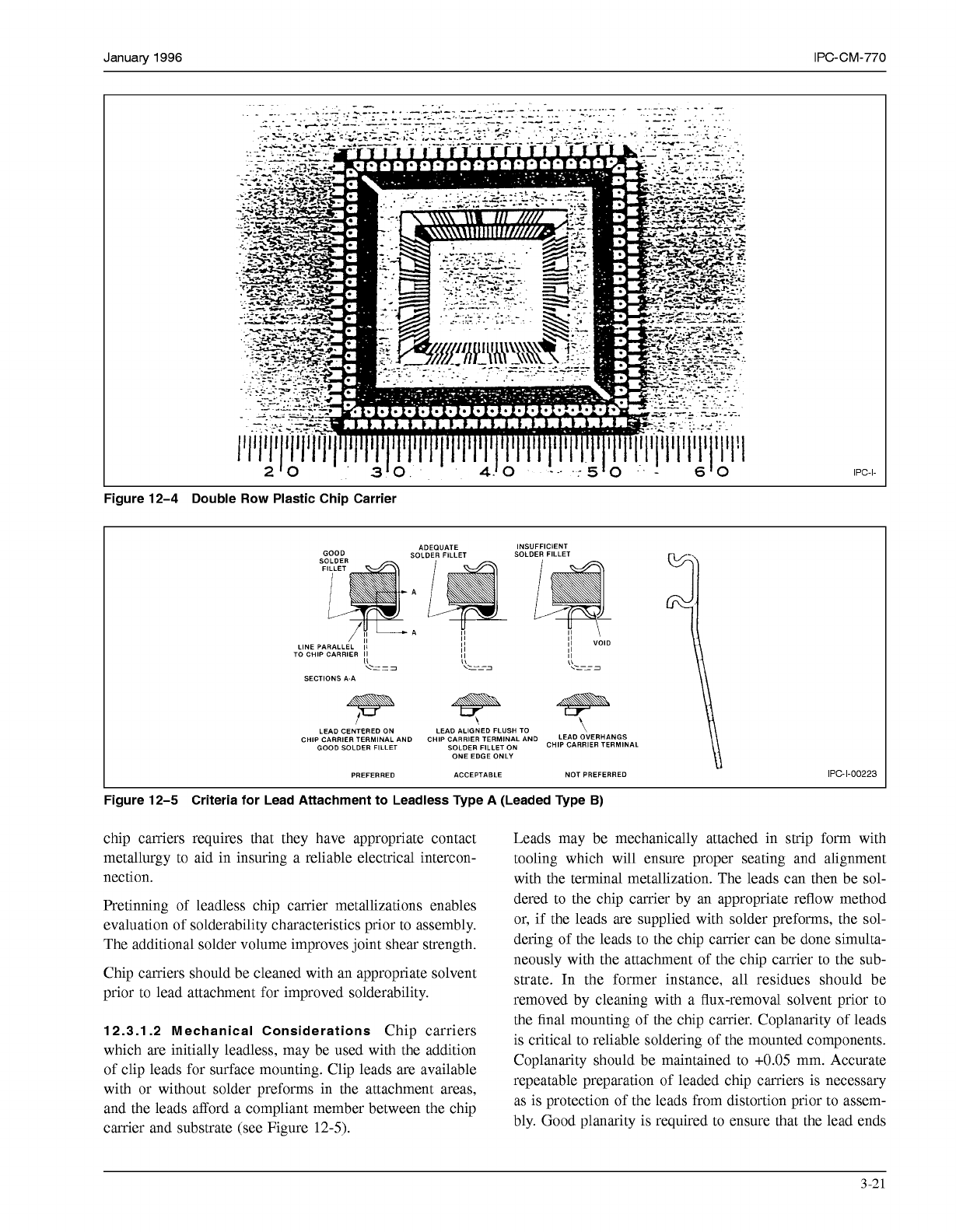

Figure 12-5 Criteria for Lead Attachment to Leadless Type A (Leaded Type

B)

chip carriers requires that they have appropriate contact

metallurgy to aid in insuring a reliable electrical intercon-

nection.

Pretinning of leadless chip carrier metallizations enables

evaluation of solderability characteristics prior to assembly.

The additional solder volume improves joint shear strength.

Chip carriers should be cleaned with an appropriate solvent

prior to lead attachment for improved solderability.

12.3.1.2 Mechanical Considerations

Chip carriers

which are initially leadless, may be used with the addition

of clip leads for surface mounting. Clip leads are available

with or without solder preforms in the attachment areas,

and the leads afford a compliant member between the chip

carrier and substrate (see Figure

12-5).

Leads may be mechanically attached in strip form with

tooling which will ensure proper seating and alignment

with the terminal metallization. The leads can then be sol-

dered to the chip carrier by an appropriate reflow method

or, if the leads are supplied with solder preforms, the sol-

dering of the leads to the chip carrier can be done simulta-

neously with the attachment of the chip carrier to the sub-

strate. In the former instance, all residues should be

removed by cleaning with a flux-removal solvent prior to

the final mounting of the chip carrier. Coplanarity of leads

is critical to reliable soldering of the mounted components.

Coplanarity should be maintained to

+0.05

mm. Accurate

repeatable preparation of leaded chip carriers is necessary

as is protection of the leads from distortion prior to assem-

bly. Good planarity is required to ensure that the lead ends

3-21

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

IPC-CM-770

Januaty

1996

make adequate contact with substrate solder lands. Flatness

of the substrate is also of concern and needs to be con-

trolled.

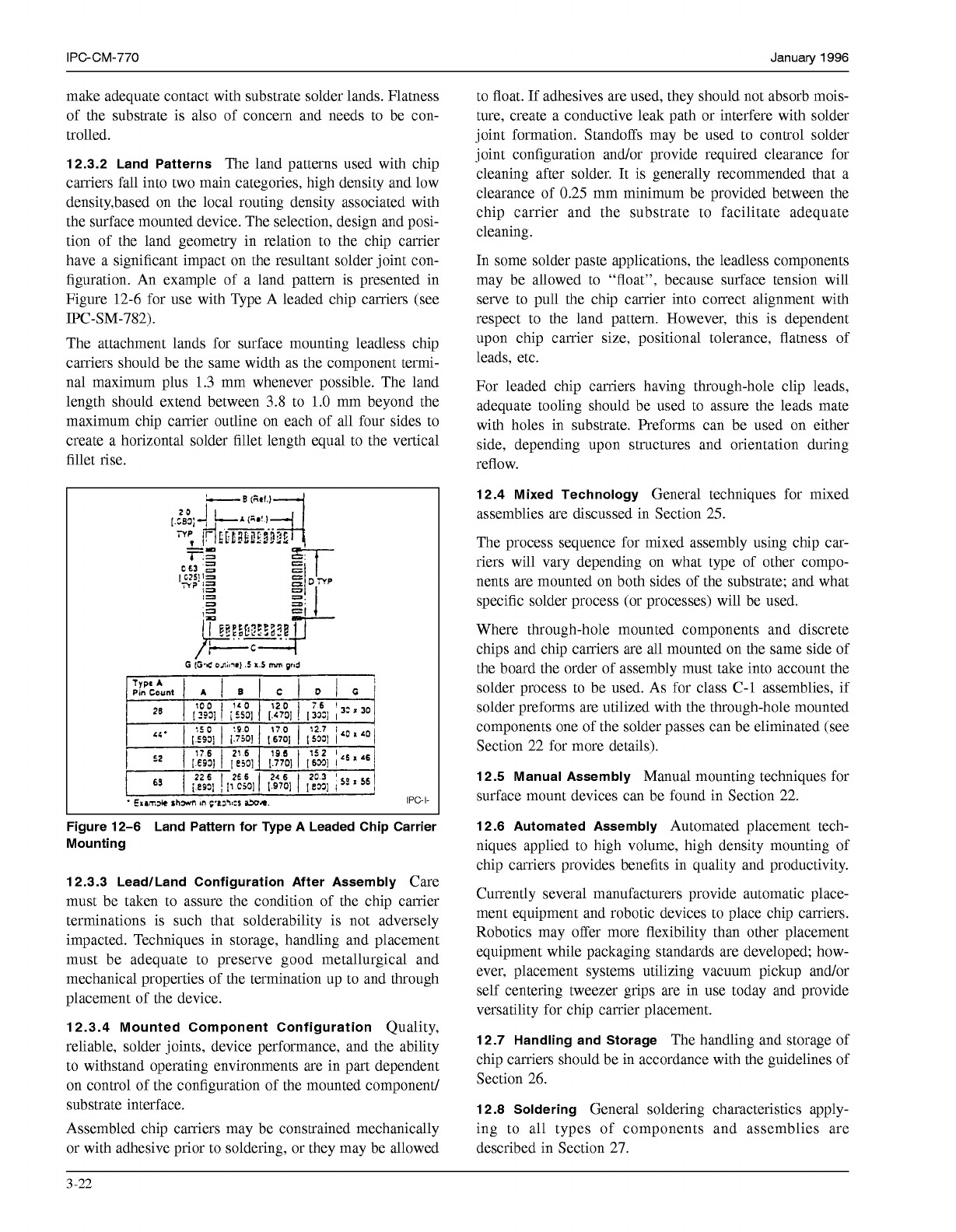

12.3.2 Land Patterns

The land patterns used with chip

carriers fall into two main categories, high density and low

density,based on the local routing density associated with

the surface mounted device. The selection, design and posi-

tion of the land geometry in relation to the chip carrier

have a significant impact on the resultant solder joint con-

figuration. An example of a land pattern is presented in

Figure 12-6 for use with Type A leaded chip carriers (see

IPC-SM-782).

The attachment lands for surface mounting leadless chip

carriers should be the same width as the component termi-

nal maximum plus 1.3 mm whenever possible. The land

length should extend between 3.8 to

1.0

mm beyond the

maximum chip carrier outline on each of all four sides to

create a horizontal solder fillet length equal to the vertical

fillet rise.

IPC-I-

L

Figure 12-6 Land Pattern for Type A Leaded Chip Carrier

Mounting

12.3.3 LeadlLand Configuration After Assembly

Care

must be taken to assure the condition of the chip carrier

terminations is such that solderability is not adversely

impacted. Techniques in storage, handling and placement

must be adequate to preserve good metallurgical and

mechanical properties of the termination up to and through

placement of the device.

12.3.4 Mounted Component Configuration

Quality,

reliable, solder joints, device performance, and the ability

to withstand operating environments are in part dependent

on control of the configuration of the mounted component/

substrate interface.

Assembled chip carriers may be constrained mechanically

or with adhesive prior to soldering, or they may be allowed

to float.

If

adhesives are used, they should not absorb mois-

ture, create a conductive leak path or interfere with solder

joint formation. Standoffs may be used to control solder

joint configuration and/or provide required clearance for

cleaning after solder. It is generally recommended that a

clearance of 0.25 mm minimum be provided between the

chip carrier and the substrate to facilitate adequate

cleaning.

In some solder paste applications, the leadless components

may be allowed to “float”, because surface tension will

serve to pull the chip carrier into correct alignment with

respect to the land pattern. However, this is dependent

upon chip carrier size, positional tolerance, flatness of

leads, etc.

For leaded chip carriers having through-hole clip leads,

adequate tooling should be used to assure the leads mate

with holes in substrate. Preforms can be used on either

side, depending upon structures and orientation during

reflow.

12.4 Mixed Technology

General techniques for mixed

assemblies are discussed in Section 25.

The process sequence for mixed assembly using chip car-

riers will vary depending on what type of other compo-

nents are mounted on both sides of the substrate; and what

specific solder process (or processes) will be used.

Where through-hole mounted components and discrete

chips and chip carriers are all mounted on the same side of

the board the order of assembly must take into account the

solder process to be used. As for class C-1 assemblies, if

solder preforms are utilized with the through-hole mounted

components one of the solder passes can be eliminated (see

Section 22 for more details).

12.5 Manual Assembly

Manual mounting techniques for

surface mount devices can be found in Section 22.

12.6 Automated Assembly

Automated placement tech-

niques applied to high volume, high density mounting of

chip carriers provides benefits in quality and productivity.

Currently several manufacturers provide automatic place-

ment equipment and robotic devices to place chip carriers.

Robotics may offer more flexibility than other placement

equipment while packaging standards are developed; how-

ever, placement systems utilizing vacuum pickup and/or

self centering tweezer grips are in use today and provide

versatility for chip carrier placement.

12.7 Handling and Storage

The handling and storage of

chip carriers should be in accordance with the guidelines of

Section 26.

12.8 Soldering

General soldering characteristics apply-

ing to all types of components and assemblies are

described in Section 27.

3

-22

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services

COPYRIGHT Association Connecting Electronics Industries

Licensed by Information Handling Services