IPC-7351B CN_edit.pdf - 第28页

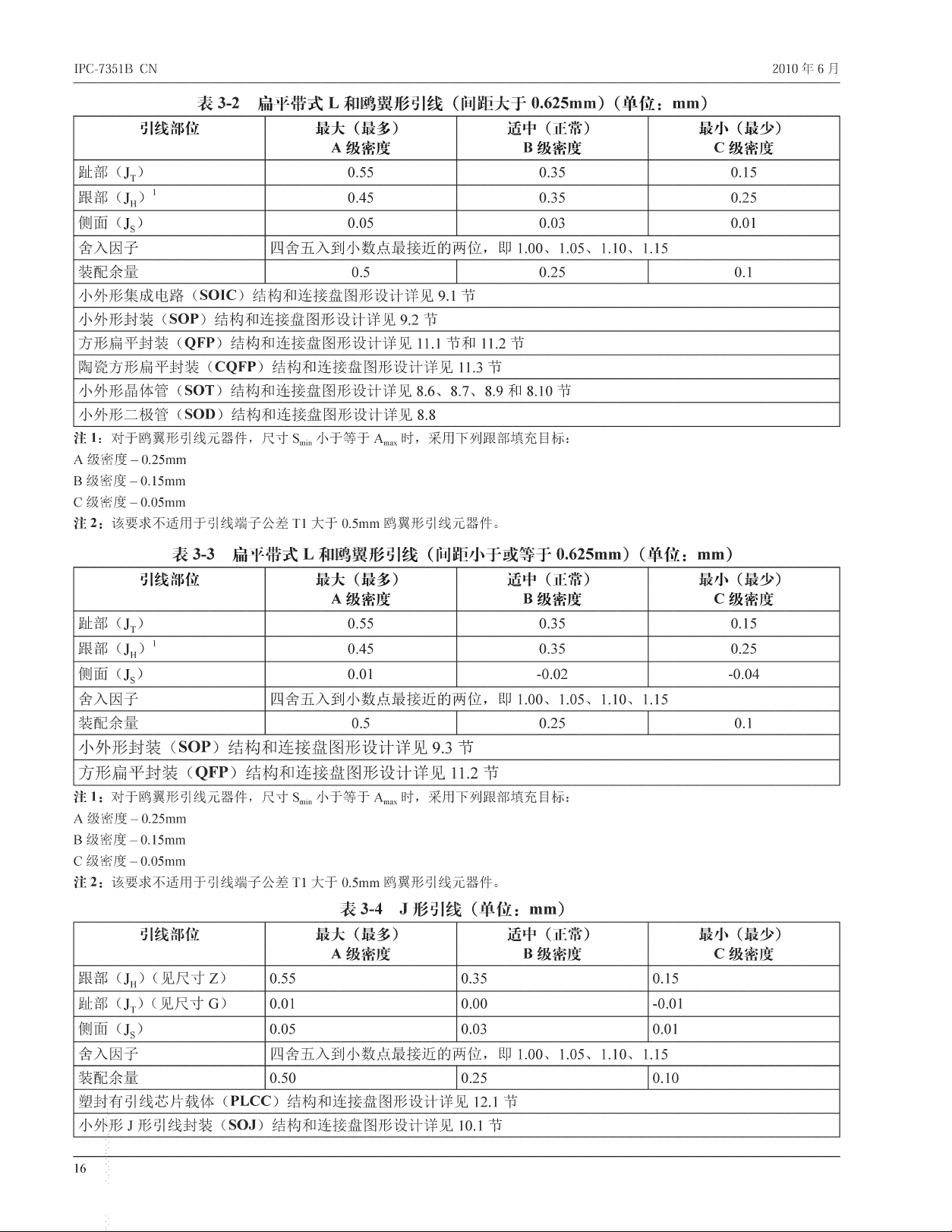

I P C - 7 35 1 B CN 2 0 1 0 年 6 月 表 3 - 2 扁 f 带 式 L 和 鸪 翼 形 引 线 ( 间 距 大 于 0 . 6 2 5 m m ) ( 单 位 : m i n ) 引 线 部 位 最 大 ( 最 多 ) A 级 密 度 适 中 ( 正 常 ) B 级 密 度 最 小 ( 最 少 ) C 级 密 度 趾 部 ( J T ) 0 .5 5 0 .35 0 . 1 5 跟 部 ( J H ) 1…

2010 年 6 月 IPC-7351BCN

表 3 - 1 片式元器件公差分析要素

公差要素 详细说明

元器件公差

每个元器件尺寸在MMC与 LMC条件下,长度、宽度和端子或引线之间的距离之差。公式中的“ C ”

即为该公差。

印制板公差

每个连接盘图形尺寸在MMC与 LMC条件下的差值。公式中的“F ” 即为该公差。

定位精度 定位精度定义为准确位置直径(DTP)。它是指连接盘图形的理论中心与元器件图心的偏移量(包

括 表 3 -26中的要素定位公差)。

趾部填充

连接盘超出端子或引线端头的部分(见 表 3-2至表 3-2)。

跟部填充

连接盘超出内部端子或引线跟部的部分(见 表 3 -2 至表3-2)。

侧面填充宽度

连接盘超出端子或引线任一侧的部分(见表3-2至表3-2)。

包含在IPC-7351连接盘图形计算器中的连接盘图形库可根据完成后的连接盘图形尺寸完成对假设焊点与所丨丨

形成焊点的公差分析。元器件尺寸公差、连 接 盘 图 形 尺 寸 (在互连基板上的制作公差)及元器件贴装设备:丨

精度都要考虑在内。这些公差用统计学的方法进行描述,并假设元器件、制作和贴装精度公差均为均匀分布。

在 IPC-7351连接盘图形 库中分别给 出 了 制 作 公 差 (F ) 和 设 备 贴 装 精 度 公 差 (P )。可根据用户的设备能

力或制作标准对这些数据进行修改。例如,许多印制板制造商将补偿蚀刻因素、增加或“ 膨胀”连接盘部分。

在这种情况下,印制板制造商的蚀刻补偿因素和IPC-7351默 认 的 “ F ” 公差叠加,就会在连接盘尺寸上

形 成 “ 双倍蚀刻补偿”,超出了预期。这样,在 IPC-7351连接盘图形计算器的“ 计算器设定” 菜单中,制

作公差需设定为0.0mm。

元 器 件 公 差 范 围 (Cp Cs,Cw) 是给定的最大尺寸与最小尺寸之差。用户可根据经验和元器件供应商所

提供相关信息修改这些数值。

已根据工业生产经验和可靠性测试得到了趾部、跟 部 或 侧 面 (JT,JH,Js) 的最少焊料填充尺寸。焊点强

度主要由焊料体积决定。可见的焊料填充是良好湿润的必要证据。因而,库文件电子数据表中的参数值

通常可保证得到良好的焊料填充。然而,对于这三种连接盘图形,如果任何一种连接盘图形的用户希望

为贴装和焊接设备创造更可靠的工艺条件,可修改焊盘尺寸分析中的单个要素以实现新的和理想的尺寸

条件。这包括元器件、印制板或贴装精度范围,还有预期的最小焊点或连接盘伸出尺寸。另外,本标准

认识到对焊料填充或连接盘突出条件有不同的目标需求。

表 3 -2 至 表 3-22给出了该标准建立的三个目标所釆用的原则。这些表反映了连接盘伸出的最大(最多)、

适 中 (标称) 、最 小 (最少)实体状况三种情况,用以设计各种表面贴装元器件引线或端子的连接盘图形。

除非另有说明,IPC-7351标准中的三个目标是指A 、B 、C 三种密度等级。

对于一些不同类型元器件、连接盘图形设计概念有所不同。如无趾部、跟部或侧面的焊料填充;与整个

端子与连接盘外围一样相似。无论圆形或矩形的连接盘,一旦公差确定,它就可应用在某个特定元器件

的连接盘外围。因 此 使 用 “ 外 围” 这个词,用来表示在端子周围的要素。这个词适用于表3 -17至 表 3-19

及 表 3-21。详 见 15.4至 15.5。

注 : 在 使 用 表 3 -2 和 表 3 - 3 中的信息时注意以下几点:由于某些元器件的器件托高的降低(少 于 0.15mm),

在确定鸥翼形元器件连接盘图形长度时,要注意跟部焊料填充能延伸到封装本体,从而导致焊料接触封

装本体,所以要确保这些焊料不会导致元器件引线桥接。元器件尺寸公差范围过大可能会导致连接盘图

形偏大而使跟部焊料填充延伸至元器件本体下。这种情况下,使用大尺寸的连接盘、小尺寸元器件的安

装 面 (印制板表面与欧翼形元器件底部之间的托高)以及过厚的焊膏的配合,会导致在贴装过程中一部

分焊料粘附在元器件上,进而导致在再流焊接后相邻元器件引线桥接。

15

IPC-7351B CN

2010 年 6 月

表 3 - 2 扁f 带 式 L 和 鸪 翼 形 引 线 (间距大于0 .6 2 5 m m )( 单位:min)

引线部位 最 大 (最多)

A 级密度

适 中 (正常)

B 级密度

最 小 (最少)

C 级密度

趾 部 (JT)

0.55 0.35 0.15

跟 部 (J H) 1

0.45 0.35 0.25

侧 面 (J s )

0.05 0.03 0.01

舍入因子

四舍五入到小数点最接近的两位,即 1..00、1.05、:L10、1.15

装配余量

0.5 0.25 0.1

小外 形 集 成 电 路 (S O I C ) 结构和连接盘图形设计详见9 .1 节

小 外 形 封 装 (S O .P )结构和连接盘图形设计详见9 .2 节

方 形 扁 平 封 装 (Q F P ) 结构和连接盘图形设计详见1 L 1 节 和 11.2节

陶瓷方形扁平 封 装(C Q F P ) 结构和连接盘图形设计详见11.3节

小 外 形 晶 体 管 (S O T ) 结构和连接盘图形设计详见8.6、8.7、8 .9 和 8.1 0节

小 外 形 二 极 管 (S O D ) 结构和连接盘图形设计详见8.8

注 1 : 对于鸥翼形引线元器件,尺 寸 Smm小于等于 Ainax时,釆用下列跟部填充目标:

A 级密度 _ 0.25mm

B 级 密 度- 0.15mm

C 级 密 度 - 0,05mm

注 2 : 该要求不适用于引线端子公差T 1 大 于 0.5m m 瞎翼形引线元器件。

表 3 - 3 扁平带式 L _ _ 翼 形 引 线 (间距小于或等于0.625H1II1)( 单 位 :min)

引线部位 最 大 (最多)

A 级密度

适 中 (正常)

B 级密度

最 小 (最少)

C 级密度

趾 部 (JT)

0.55 0.35 0.15

跟 部 (J H) 1

0.45 035 025

侧 面 (J s )

0.01

4102 -d04

舍入因子

四舍五入到小数点最接近的两位,即 1..00、1,05、1,10、1.15

装配余量

0.5 025 0.1

小 外 形 封 装 (S O P ) 结 构 和 连 接 盘 图 形 设 计 详 见 9 .3 节

方 形 扁 平 封 装 (Q F P ) 结 构 和 连 接 盘 图 形 设 计 详 见 1 1 .2 节

注 1 : 对于鸥翼形引线元器件,尺 寸 Smm小于等于 Amax时,釆用下列跟部填充目标:

A 级 密度 - 0.25mm

B 级 密 度- 0.15mm

C 级 密 度 - 0,05mm

注 2 : 该要求不适用于引线端子公差T 1 大 于 0.5m m 鸥翼形引线元器件。

表 3-4 J 形 引 线 (单位:min)

引线部位 最 大

(最多)

A 级密度

适 中 ( : £ 常 )

B 级密度

最 小 (最少)

C 级密度

跟 部 (JH) ( 见 尺 寸 Z)

0.55 0.35 0.15

趾 部 (JT) ( 见 尺 寸 G)

0.01 0.00 -0,01

侧 面 (Js )

0.05 0.03 0.01

舍入因子

四舍五入到小数点最接近的两位,即 1.00、1.05、1,10、1.15

装配余量

0.50 0.25 0.10

塑封 有 引线芯片载体 (P L C C ) 结构和连接盘图形设计详见1.2J.节

小外形 J 形弓1线 封 装 (S O J ) 结构和连接盘图形设计详见10.1节

16

201 0 年 6 月 IPC-735IB CN

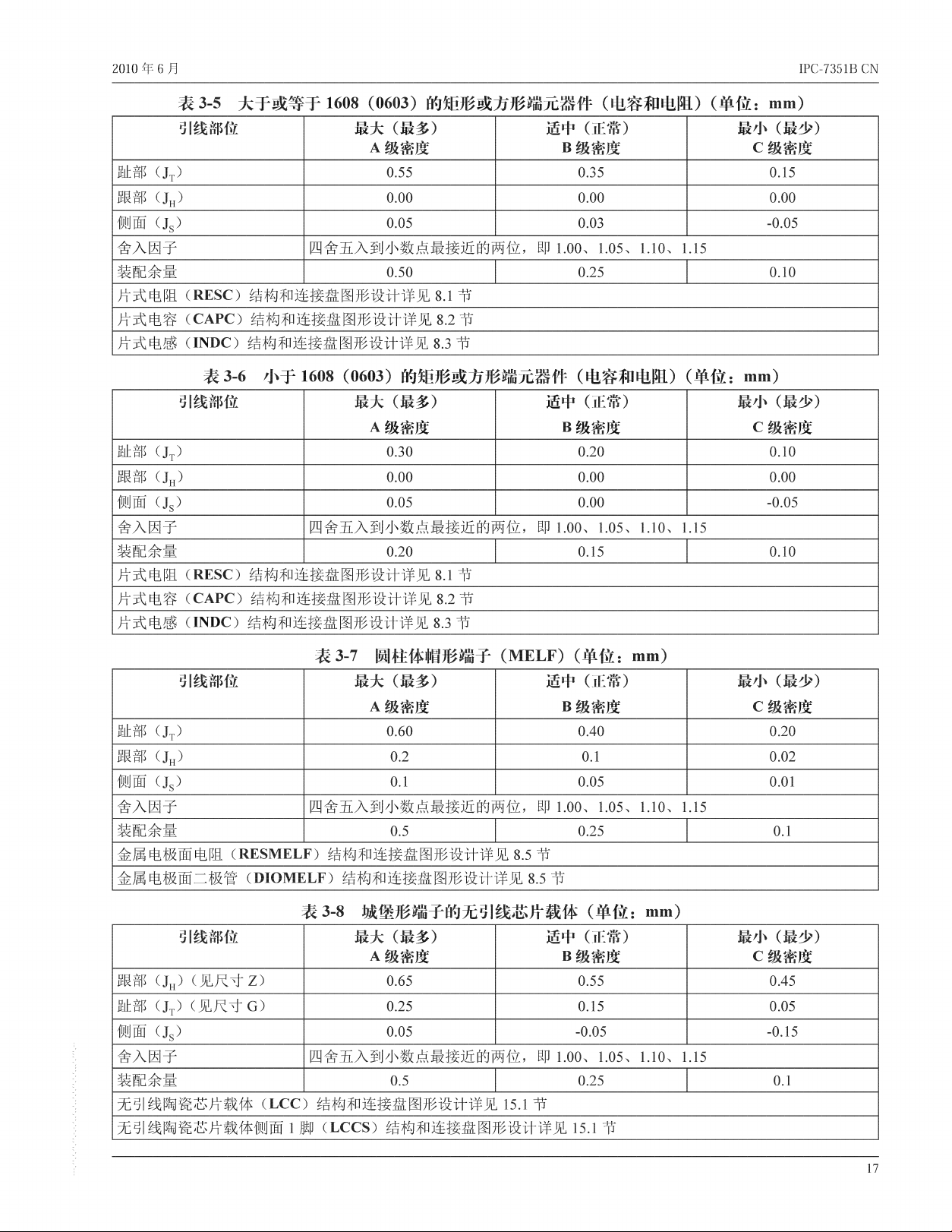

表 3 - 5 大 于 或 等 于 1608 ( 0 6 0 3 ) 的矩形或方 形端元器件(电容和电阻)(单位:m m)

引线部位 最 大 (最多)

A 级密度

适 中 (正常)

B 级密度

最 小 (最少)

C 级密度

趾 部 (JT)

0.55 035 0.15

跟 部 (JH)

0.00 0.00 0.00

侧 面 (Js)

0.05 0.03 -0.05

舍入因子

四舍五入到小数点最接近的两位,即 LOO、L05、1,10、L15

装配余量

0.50 0.25 0.10

片 式 电 阻 C R E S C )结构和连接盘图形设计详见8 .1 节

片 式 电 容 (C A P C ) 结构和连接盘图形设计详见8 .2 节

片 式 电 感 (I N D C ) 结构和连接盘图形设计详见8 .3 节

表 3 - 6 小 于 1608 ( 0 6 0 3 ) 的矩形或方 形端元器件(电容和电阻)(单 位 :min)

引线部位

最 大 (最多)

A 级密度

适 中 ( : £ 常 )

B 级密度

最 小 (最少)

C 级密度

趾 部 (JT)

0.30 0.20 0.10

跟 部 (JH)

0.00 0.00 0.00

侧 面 (Js)

0.05 0.00 -d05

舍入因子

四舍五入到小数点最接近的两位,即 1,00、1,05、1,10、L15

装配余量

0.20 0.15 0.10

片 式 电 阻 (R E S C ) 结构和连接盘图形设计详见8 .1 节

片 式 电 容 (C A P C ) 结构和连接盘图形设计详见8 2 节

片 式 电 感 (I N D C ) 结构和连接盘图形设计详见8 .3 节

表 3 _ 7 圆柱 体 帽 形 端 子 (M E L F ) ( 单 位:腿m)

引线部位 最 大

(最多)

A 级密度

适 中 (正常)

B 级密度

最 小 (最少)

C 级密度

趾 部 (JT)

0.60 0.40 0.20

跟 部 (JH)

0.2 0

.1

0.02

侧 面 (Js)

0.1 0.05 0.01

舍入因子

四舍五入到小数点最接近的两位,即 1.00、1.05、1.10、L15

装配余量

0.5 0.25 0.1

金 属 电 极 面 电 阻 (R E S M E L F )结构和连接盘图形设计详见8 .5 节

金 属 电 极 面 二 极 管 (M O M E L F ) 结构和连接盘图形设计详见8 .5 节

表 3 - 8 城堡形端子的无引线芯片载体(单 位 :m m)

引线部位

最 大 (最多)

A 级密度

适 中 (正常)

B 级密度

最 小 (最少)

C 级密度

跟 部 (JH) ( 见 尺 寸 Z)

0.65 0.55 0.45

趾 部 (JT) ( 见 尺 寸 G)

0.25 0.15 0.05

侧 面 (Js)

0.05 »0.05 4U 5

舍入因子

四舍五入到小数点最接近的两位,即 1.00、1.05、L10、1.15

装配余量

0.5 0.25 0.1

无引线 陶 瓷芯片载体(L C C ) 结构和连接盘图形设计详见1.5J.节

无引线陶瓷芯片载体侧面1 脚 (L C C S )结构和连接盘图形设计详见15.1节

17