IPC-7351B CN_edit.pdf - 第57页

2 0 1 0 年 6 月 I P C - 7 3 5 I B CN 为 确 保 探 针 採 头 与 印 制 板 的 精 密 对 准 ,必 须 向 夹 具 开 发 商 提 供 探 针 的 精 确 X 和 Y 位 置 及 具 体 的 网 络 。 可 以 从 C A D 数 据 获 取 测 试 点 的 准 确 位 置 , 将 数 据 提 供 给 夹 具 制 造 商 。 这 些 数 据 将 减 少 夹 具 的 开 发 时 间 ,免 去 在 夹…

IPC-7351B CN

2010 年 6 月

5 . 2 . 1 测 试 原 则 应 该 制 定 测 试 原 则 ,使其涵盖产品所必须的测试方法的任意组合。然后 ,在开始设计

过程之前,确定实施所要求测试的简单策略。在产品开发周期的初期而不是结束时规划可测试性可明显

地降低每个节点的测试成本,并且可提高整个产品开发周期从最初的设计到最后的测试的可测试性。

最好的测试策略是为每种可釆用的测试方法做出规定。既使在开发周期的初期就很明确地规定了产品的

测试程序,在完成设计后,也可能会发生变化。概述测试原则时,需要考虑以下几点:

a) 所有元器件导通孔的布局策略

b) 提供每个网络测试节点

C ) 每个测试节点最好在印制板的相同面

d) 合适的测试点焊盘尺寸及间距

既使在高密度设计中,从板的任一面提供到每个网络节点的1.00%覆盖的原则也是能够实现的。但是在设

计开始时就必须做出这一决定。

5 . 2 . 2 裸 板 测 试 策 略 建 立 产 品 的 测 试 原 则 后 ,就可以定义测试策略或测试程序。纵观测试程序中的几

个要素,要考虑:

a ) 釆 用 A O I光学检测内层。

b ) 光学检测外层连接盘/ 导通孔连接。

c ) 裸板测试中,测试探针仅放置在任一面上的导通孔。

d ) 探针不能损伤SM T焊盘。

e ) 装载测试板后,探测可以放置在辅面的导通孔上。

f ) 将焊膏丝网印刷在密封板的导通孔上。

必须组织所有涉及测试的并行工程团队成员制定实际产品测试策略。这样将会确保各种测试类型及程序

的集合不会有太多的冗余或形成可能危及测试完整性的间隙。

5 . 3 组装板的所有节点可测试性测试板所需要的测试探针数等于装置节点的总数或装置之间公共连接

的总数。但 是 ,多数高密度表面贴装设计印制板,常常要求使用双面放置测试点或使用抓斗式测试夹具,

因为从板的一面不能测试所有的节点。

在线测 试 (In-Circuit Test,以下简称为ICT ) 只需要测试每个网络的任意节点。每个网络至少有两个节点,

有的有很多节点,例如:存储板上一个网络可能连接很多节点。为了 达 到 IC T 测试的全面覆盖,只测试

每个网络的任意一个节点即可。因此,完 成 IC T 所要求的

测试探针总数明显少于裸板测试所要求的数量。

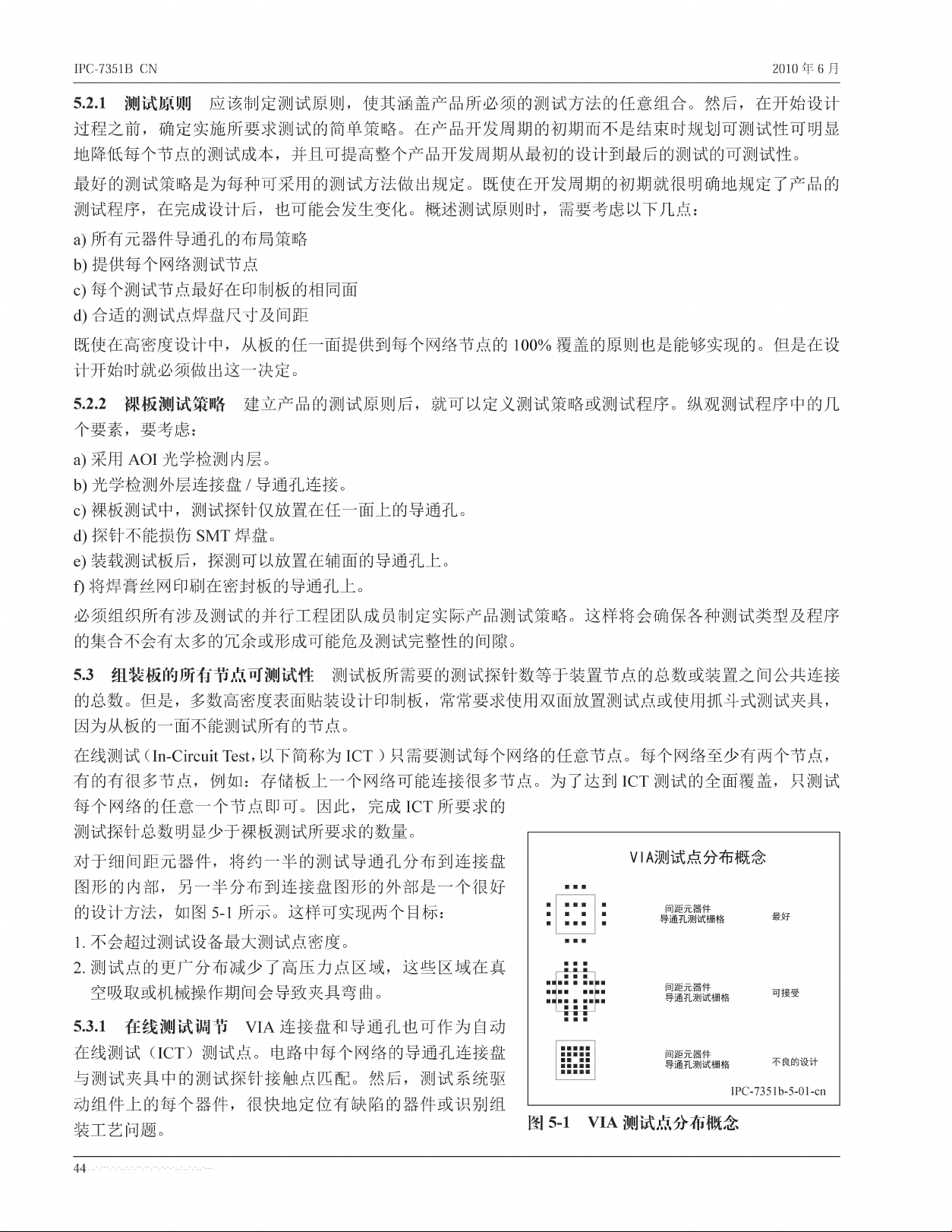

对于细间距元器件,将约一半的测试导通孔分布到连接盘

图形的内部,另一半分布到连接盘图形的外部是一个很好

的设计方法,如 图 5-1 所示。这样可实现两个目标:

L 不会超过测试设备最大测试点密度。

2 .测试点的更广分布减少了高压力点区域,这些区域在真

空吸取或机械操作期间会导致夹具弯曲。

5 . 3 . 1 在 线 测 试 调 节 V IA 连接盘和导通孔也可作为自动

在 线 测 试 (I C T ) 测试点。电路中每个网络的导通孔连接盘

与测试夹具中的测试探针接触点匹配。然 后 ,测试系统驱

动组件上的每个器件,很快地定位有缺陷的器件或识别组

装工艺问题。 图七1 V I A 测试点分布概念

VIA测试点分布概念

圖圔圖

圖 _ _ _

: 间距元器件 ^

圖

圖

圖 圖

圖圔圖

: 导通孔测试栅格 ®女子

圖圔圖

圖圖圖

■ ■ ■

圖圖圖

圖圖圖圖 圖圍

_圖 间距兀器件 與

„ 导通孔测试栅格

圖圖圖

圍圍圍

圖圖圖

间距元器件

圖圖 圖圖

导通孔测试栅格 不良的设1+

lPC~7351b~5~01~cn

44、

201 0 年 6 月 IPC-735IB CN

为确保探针採头与印制板的精密对准,必须向夹具开发商提供探针的精确X 和 Y 位置及具体的网络。可

以从 C A D 数据获取测试点的准确位置,将数据提供给夹具制造商。这些数据将减少夹具的开发时间,免

去在夹具基座上钻过多的非功能孔。对于小批量组装或高密度组装,借助于飞针测试设备的无夹具测试

是一种可选方案。

5 . 3 . 2 多 探 针测试 一 些测试 探 针 系统会对组装板施加相当大的变形力,是已知的早期失效的来源。印

制板布局必须确保印制板上探测点之间有充分的距离并且交叉排列,以避免在多探针测试中过度地变形。

当探针点位置过度密集时,在测试夹具设计中可能需要设计另外的支撑点,以抵消高探针压力过于集中

的影响。印制板支撑区域应该位于板上无导体和元器件的地方。

5 . 4 部分节点可测如果设计时为测试连接盘留出了足够的空间,部分 节 点 测 试 (小 于 100% ) 还可以釆

用 探 针 (针床)测试,但这样做不如全部网络测试有效。节点测试少于100% 时,可能不能完全检查出短

路、在线测试不能彻底检查出来的缺陷及其他一些故障。

因而,为了检测、查找短路、缺陷和坏元器件,更大的负担就放到了功能测试或系统测试上。这种负担

反过来会随节点可测试百分比变化而变化。功能测试的额外工作可能包括诊断印制电路板故障的额外的

成 本 (经常性的),也可能意味着开发一个更详细的功能测试(非经常性成本)。

5 . 5 无 测 试 节 点 无 测 试 节 点 (0 % ) 没法针床测试,所有组装缺陷和元器件测试都推迟到功能测试或系

统测试设备上进行。一般每个缺陷的修理成本要高得多并不常见,即总维修成本小于开发和运行ATE针

床测试的成本。换句话说:一次性合格率必须相当高才适于用这种测试方法。

5 . 6 测试夹具的影响两面探针测试的印制板需要使用测试夹 具 。这种夹具较贵,制作时间更长,要求

在印制板主面上更大的测试连接盘以防止由于公差累加导致的重合问题,而且他们更难维护。

5 . 7 印制板测试特征

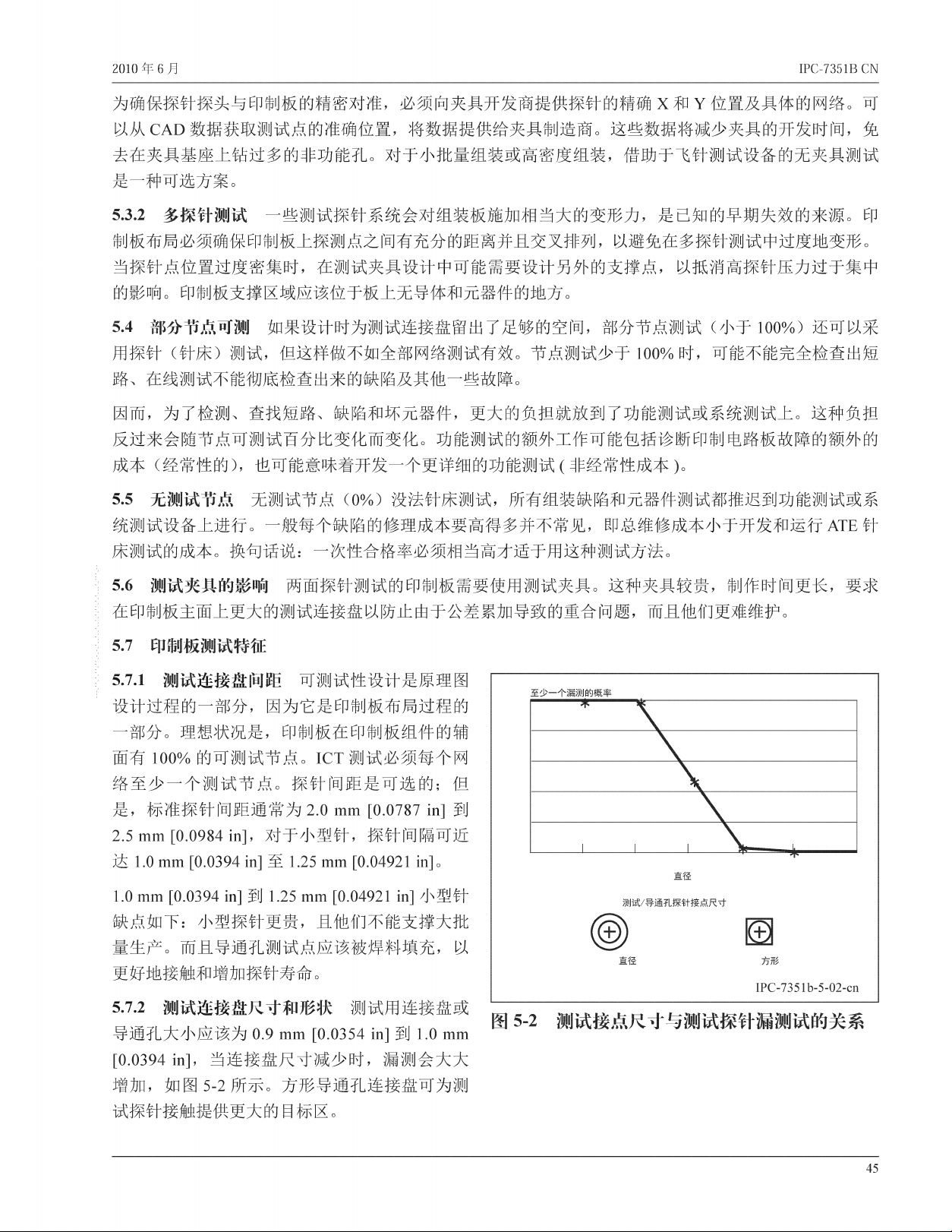

5 . 7 . 1 测 试 连 接 盘 间 距 可 测 试 性 设 计 是 原 理 图

设计过程的一部分,因为它是印制板布局过程的

一部分。理想状况是,印制板在印制板组件的辅

面 有 1 00% 的可测试节点。IC T 测试必须每个网

络 至 少 一 个 测 试 节 点 。探 针 间 距 是 可 选 的 ;但

是 ,标准探针 间 距 通常为 2 J mm [0.0787 in] 到

2.5 mm [0.0984 m ] , 对于小型针,探针间隔可近

达 L0 mm [0.0394 In] 至 L25 mm [0,04921 in]。

L0 mm [0.0394 In] 到 L25 mm [0.04921 In] 小型针

缺点如下:小型探针更贵,且他们不能支撑大批

量生产。而且导通孔测试点应该被焊料填充,以

更好地接触和增加探针寿命。

5 . 7 . 2 测 试 连 接 盘 尺 寸 和 形 状 测 试 用 连 接 盘 或

导通孔大小应该为0.9 mm [0.0354 in ] 到 L0 mm

[0.0394 i n ] , 当连接盘尺寸减少时,漏测会大大

增加 ,如 图 5 - 2 所示 。方形导通孔连接盘可为测

试探针接触提供更大的目标区。

45

IPC-7351B CN

2010 年 6 月

5 . 7 . 3 测试参数设计下列是一些通常需要考虑的重要焊盘设计规范,应该将其考虑到印制板中:

a ) 在印制板的对角上应该有两个未电镀的定位孔。

b ) 测试连接盘应该距印制板的边缘最少2.5mm [0.0984 I n ] , 以方便真空夹具使用。

c ) 当釆用V IA 孔作为测试点时,应该釆取措施确保不能以牺牲信号质量为代价来保证测试能力。

d ) 测试连接盘距贴装焊盘间距应该最少为0.63 mm [0.0248 in]。

e ) 如果可能,为电源和接地网络提供多个测试连接盘。

f ) 如果可能,为所有没有连接的网络提供测试连接盘。 自由运行的电路门有时会导致IC T 测试不稳定,

这样可提供将这些干扰信号接地的一种方法。

有时 希望IC T 测试期间提供驱动和感应节点测试连接盘,以完成6 线桥接测量。测试工程师应该给出这

样做的指导说明。

另外,在需要修改电路布局时,保持组装图上的测试导通孔和测试连接盘不变是很有帮助的。不移动测

试连接盘的改版可避免夹具修改,节约成本和时间。

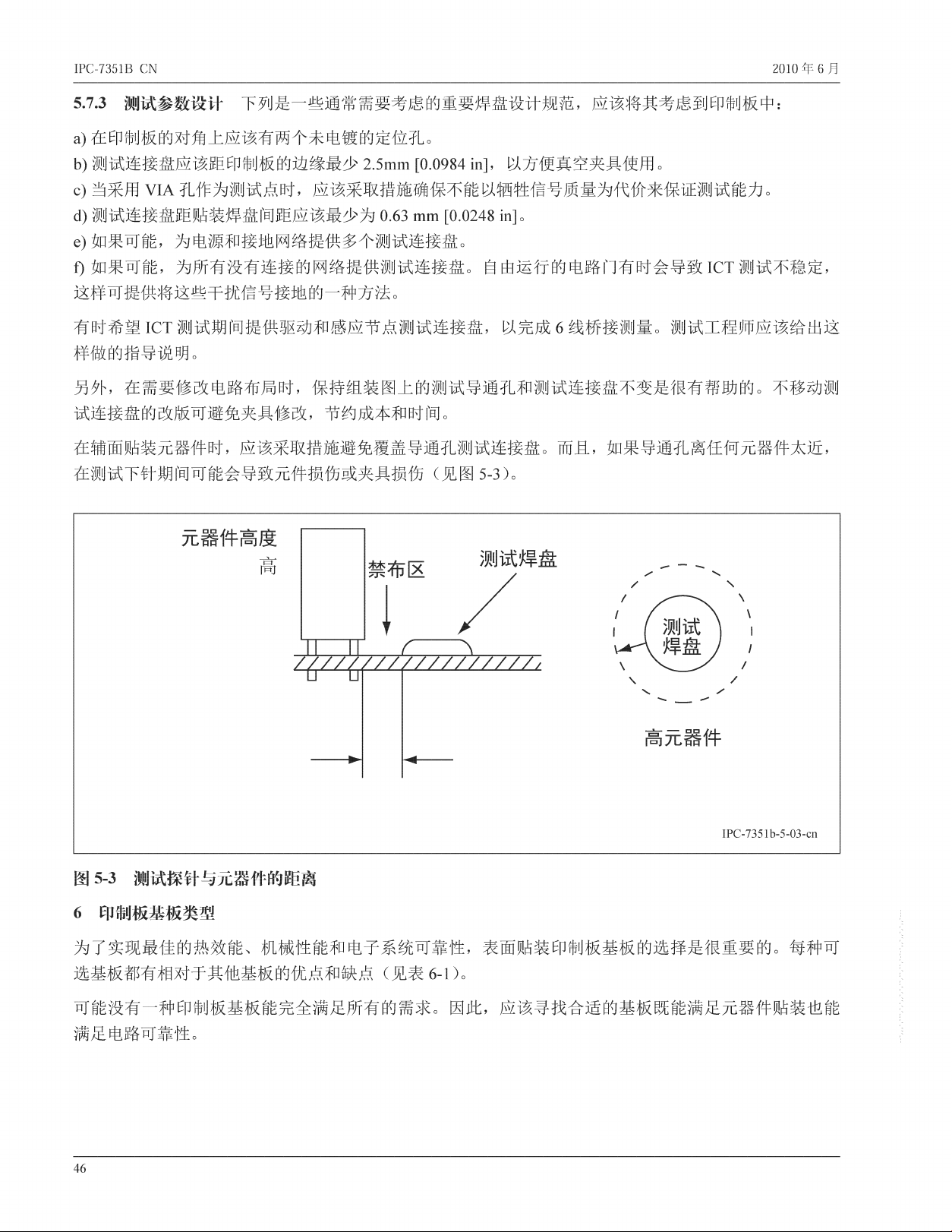

在辅面贴装元器件时,应该釆取措施避免覆盖导通孔测试连接盘。而且,如果导通孔离任何元器件太近,

在测试下针期间可能会导致元件损伤或夹具损伤(见 图 5-3)。

高元器件

IPC-7351b-5-03-cn

_ 5_3 测试探针与元器件的距离

6 印制板基板类型

为了实现最佳的热效能、机械性能和电子系统可靠性,表面贴装印制板基板的选择是很重要的。每种可

选基板都有相对于其他基板的优点和缺点(见 表 6-1 )。

可能没有一种印制板基板能完全满足所有的需求。因此,应该寻找合适的基板既能满足元器件贴装也能

满足电路可靠性。

46