IPC-7351B CN_edit.pdf - 第54页

I P C - 7 35 1 B CN 2 0 1 0 年 6 月 表 3 - 2 7 各 种 印 制 板 表 面 涂 层 的 主 要 属 性 特 征 H A S L O S P 化 学 镀 镍 / 浸 金 电 解 镍 / 电 镀 金 浸 银 浸 锡 保 质 期 适 当 的 处 置 1 年 6 个 月 大 于 1 年 小 于 1 年 6 个 月 6 个 月 与 焊 接 表 面 的 处 置 / 接 触 应 该 避 免 必 须 避 免 应 …

2010 年 6 月 IPC-7351BCN

3 . 5 表面处理

3 . 5 . 1 阻 焊 膜 涂 层 阻焊膜涂层用于保护印制板上的电路。阻焊膜有两种形式,液体阻焊膜和干膜阻焊

膜 。可釆用几种工艺方法涂敷聚合膜材料,并可提供各种厚度。例如 ,液体材料在涂敷完成后的厚度可

从 0.02mm[0.0079in] 到 0.025mm[0.00984in] , 而干膜产品的厚度有 0.04mm[0.016in]、0.08mm[0.0315in] 和

0.10mm[0.0394in]。尽管可釆用丝网印刷阻焊膜,但 对 于 SM T应用,推荐光成像阻焊膜。

光学工艺提供了精密的图形成像,可去除连接盘图形表面的膜残留物。膜厚度可能不是多数表面贴装组

件上的一个因素,但 是 当 细 间 距 元 件 (0.63mm[0.0248in]或更小)或 1C 器件贴装在印制板上时,薄阻焊

膜可提供更好的焊料印刷控制。

3 . 5 . 2 阻 焊 膜 开 窗 阻焊膜可用于将连接盘图形与板上的其他导电要素如导通孔、连接盘或导体隔离开。

焊盘之间没有导线穿过之处,可釆用一组简单的通窗阻焊膜开口,如 图 3 -25所示。

对于在连接盘之间有走线的连接盘设计(见 图 3-26),阻焊膜图形必须完全覆盖导线。由于需要更严格的

公差以覆盖导线同时又不会侵占连接盘区域,所以更精密的重合是必需的。印制板制造商禁止将阻焊膜

印在连接盘上。开窗距离变化范围为从0.0mm[0.0in]到 0.1mm[0.0040in]。

通 窗

IPC-7351b-3-25-cn

图 3 - 2 5 通窗阻焊 图 3 - 2 6 阻焊开窗

3 . 5 . 3 连 接 盘 表 面 涂 层 阻焊膜开口裸露表面贴装元器件的焊盘。此焊盘通常是铜基的,因此需要保护

以防止铜被氧化,进而导致焊盘表面的可焊性差。

涂层或镀层的选择取决于组装厂的喜好或被组装元器件的类型。最好对整块板釆用一种涂层或镀层。由

于不同的表面涂层要求不同的工艺步骤,所以不推荐混合釆用不同类型的表面涂层。选择涂层时根据不

同的元器件类型、引脚间距或组装工艺或引线端子涂层特性。

印制板的表面涂层可能需要具备下列功能:可焊性保护、用于接点/ 开关的导电表层、打线邦定表层及焊点

连接面。当选择最适当的表面涂层时,必须考虑印制板的各种元器件及组装操作。没有哪一种涂层对于所

有的 情 况都 是“ 最佳的”。最常用的一些表面涂层是:热 风 整 平 (HASL)、有 机 表 面 保 护 (O SP)、浸锡、

及 贵 重 金 属 涂 层 (包括化学镀镍/ 浸金、电解镍/ 电 镀 金 及 浸 银 )。

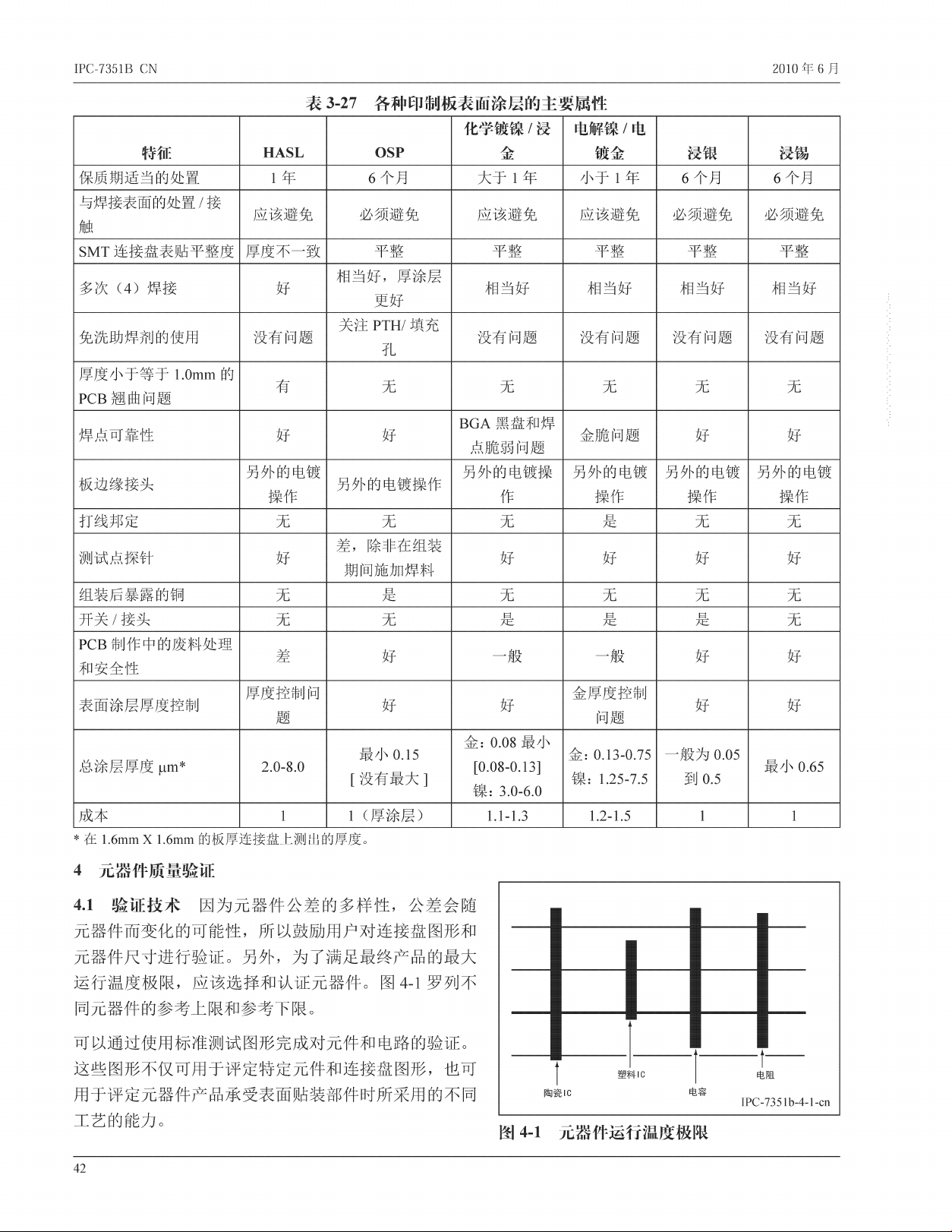

表 3-2 7给出了选择适当的表面涂层时必须考虑的一些因素。尽管 多数 H A S L合金由锡 / 铅成份组成,但

随着向无铅焊料的转换,新 的 H A SL工艺已由锡/ 铜成份组成,来完成表面涂层。出乎意料地是,由于新

合金的流动特征,HA SL连接盘似乎比原来的锡/ 铅合金涂层的连接盘更平整。但是,注意:印制板板材

料和镀铜孔结构必须承受略高的温度。

41

IPC-7351B CN

2010 年 6 月

表 3 - 2 7 各种印制板表面涂层的主要属性

特征

HASL

OSP

化学 镀镍/浸

金

电解 镍/ 电

镀金 浸银 浸锡

保质期适当的处置

1 年

6 个月

大 于 1 年

小 于 1 年

6 个月 6 个月

与焊接表面的处置/接

触

应该避免

必须避免 应该避免 应该避免 必须避免 必须避免

SM T 连接盘表贴平整度

厚度不一致

平整 平整 平整 平整 平整

多 次 (4 ) 焊接

好

相当好,厚涂层

更好

相当好 相当好 相当好 相当好

免洗助焊剂的使用 没有问题

关 注 PTH/填充

孔

没有问题 没有问题 没有问题 没有问题

厚度 小于等 于1.0mm的

PC B 翘曲问题

有 无 无 无 无 无

焊点可靠性

好 好

B G A 黑盘和焊

点脆弱问题

金脆问题

好 好

板边缘接头

另外的电镀

操作

另外的电镀操作

另外的电镀操

作

另外的电镀

操作

另外的电镀

操作

另外的电镀

操作

打线邦定

无 无 无

是

无 无

测试点探针 好

差 ,除非在组装

期间施加焊料

好 好 好 好

组装后暴露的铜

无 是 无 无 无 无

开 关 /接头

无 无 是 是 是 无

P C B 制作中的废料处理

和安全性

差

好 一般 一般 好 好

表面涂层厚度控制

厚度控制问

题

好 好

金厚度控制

问题

好 好

总涂 层厚度|im*

2.0»8.0

最 小 0.15

[ 没有最大 ]

金 :0 .0 8 最小

[0.08^0.13]

镍 :3j0-6j0

金:0.13^0.75

11: 1.25-7,5

一 般 为 0.05

到

最 小 0.65

成本

1

1 ( 厚涂层)

12^1.5

1 1

* 在 1.6mm X L 6m m 的板厚连接盘上测出的厚度。

4 元器件质量验证

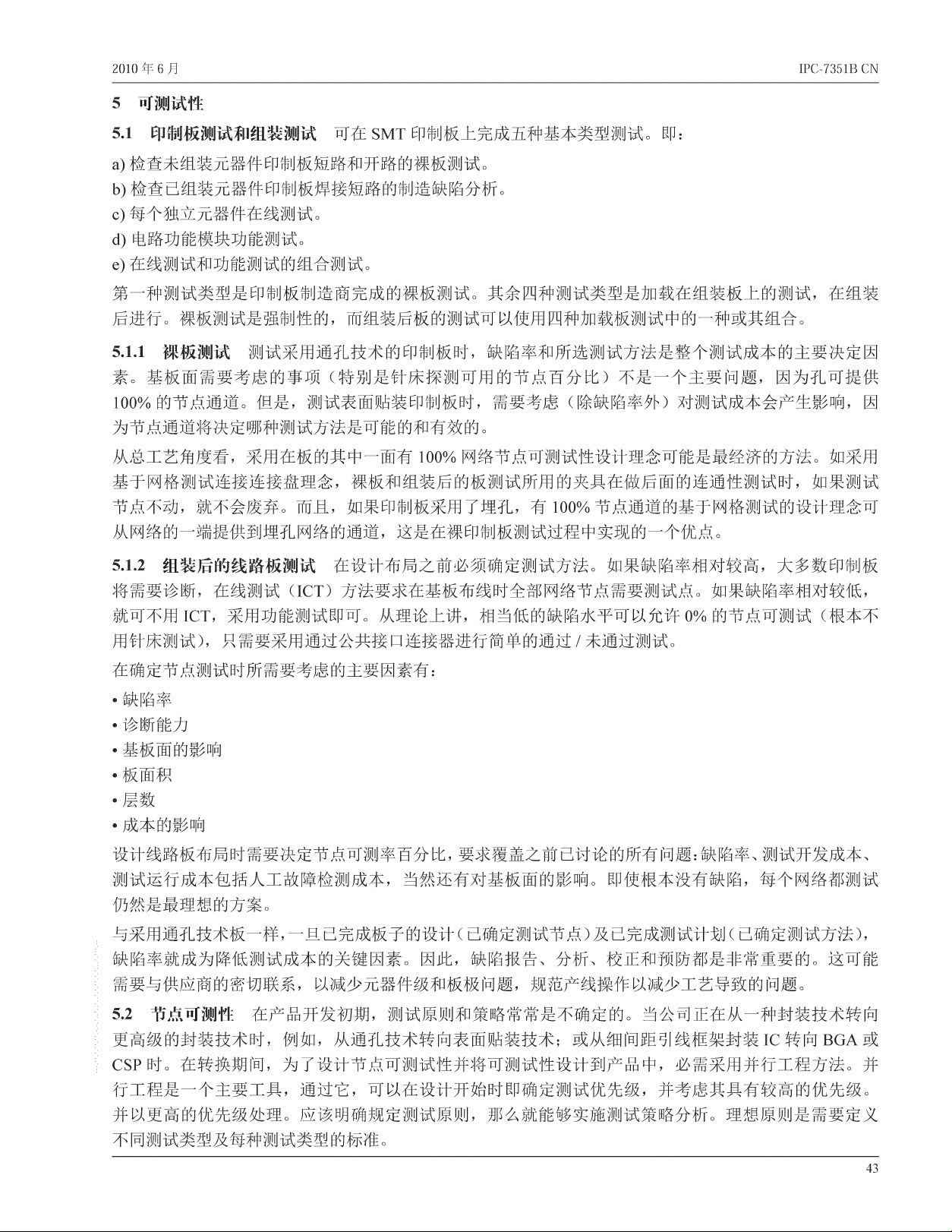

4 . 1 验 证 技 术 因 为 元 器 件 公 差 的 多 样 性 ,公差会随

元器件而变化的可能性,所以鼓励用户对连接盘图形和

元器件尺寸进行验证。另外,为了满足最终产品的最大

运行温度极限,应该选择和认证元器件。图 4 -1 罗列不

同元器件的参考上限和参考下限。

可以通过使用标准测试图形完成对元件和电路的验证。

这些图形不仅可用于评定特定元件和连接盘图形,也可

用于评定元器件产品承受表面贴装部件时所釆用的不同

工艺的能力。

图 4 - 1 元器件运行温度极限

42

201 0 年 6 月 IPC-735IB CN

5 可测试性

5 . 1 印 制 板 测 试 和 组 装 测 试 可 在 S M T 印制板上完成五种基本类型测试。艮P:

a ) 检查未组装元器件印制板短路和开路的裸板测试。

b ) 检查已组装元器件印制板焊接短路的制造缺陷分析。

c ) 每个独立元器件在线测试。

d ) 电路功能模块功能测试。

e ) 在线测试和功能测试的组合测试。

第一种测试类型是印制板制造商完成的裸板测试。其余四种测试类型是加载在组装板上的测试,在组装

后进行。裸板测试是强制性的,而组装后板的测试可以使用四种加载板测试中的一种或其组合。

5 . 1 . 1 裸 板 测 试 测 试 釆 用 通 孔 技 术 的 印 制 板 时 ,缺陷率和所选测试方法是整个测试成本的主要决定因

素 。基 板 面 需 要 考 虑 的 事 项 (特别是针 床探测可用的节点百 分比)不是一个主要问题,因为孔可提供

100% 的节点通道。但是,测试表面贴装印制板时,需 要 考 虑 (除缺陷率外)对测试成本会产生影响,因

为节点通道将决定哪种测试方法是可能的和有效的。

从总工艺角度看,釆用在板的其中一面有100% 网络节点可测试性设计理念可能是最经济的方法。如釆用

基于网格测试连接连接盘理念,裸板和组装后的板测试所用的夹具在做后面的连通性测试时,如果测试

节点不动,就不会废弃。而且,如果印制板釆用了埋孔,有 100% 节点通道的基于网格测试的设计理念可

从网络的一端提供到埋孔网络的通道,这是在裸印制板测试过程中实现的一个优点。

5 . 1 . 2 组装后的线 路板 测 试 在 设计 布 局 之 前必 须 确 定 测试 方法 。如果缺陷率相对较高,大多数印制板

将需要诊断,在 线 测 试 (I C T ) 方法要求在基板布线时全部网络节点需要测试点。如果缺陷率相对较低,

就可不用ICT,釆用功能测试即可。从理论上讲,相当低的缺陷水平可以允许0 % 的 节 点 可 测 试 (根本不

用针床测试) ,只需要釆用通过公共接口连接器进行简单的通过/ 未通过测试。

在确定节点测试时所需要考虑的主要因素有:

• 缺陷率

• 诊断能力

• 基板面的影响

• 板面积

•层数

• 成本的影响

设计线路板布局时需要决定节点可测率百分比,要求覆盖之前已讨论的所有问题: 缺陷率、测试开发成本、

测试运行成本包括人工故障检测成本,当然还有对基板面的影响。即使根本没有缺陷,每个网络都测试

仍然是最理想的方案。

与釆用通孔技术板一样,一旦已完成板子的设计(已确定测试节点)及已完成测试计划(已确定测试方法),

缺陷率就成为降低测试成本的关键因素。因此,缺陷报告、分析、校正和预防都是非常重要的。这可能

需要与供应商的密切联系,以减少元器件级和板极问题,规范产线操作以减少工艺导致的问题。

5 . 2 节 点 可 测 性 在 产 品 开 发 初 期 ,测试原则和策略常常是不确定的。当公司正在从一种封装技术转向

更高级的封装技术时,例如,从通孔技术转向表面贴装技术;或从细间距引线框架封装1C转 向 B G A 或

C S P 时。在转换期间,为了设计节点可测试性并将可测试性设计到产品中,必需釆用并行工程方法。并

行工程是一个主要工具,通过它,可以在设计开始时即确定测试优先级,并考虑其具有较高的优先级。

并以更高的优先级处理。应该明确规定测试原则,那么就能够实施测试策略分析。理想原则是需要定义

不同测试类型及每种测试类型的标准。

43