IPC-7351B CN_edit.pdf - 第80页

IP C -7 3 5 1 B CN 2 0 1 0 年 6 月 I P C - 7 3 5 1 b - l l - 0 2 - c n I P C - 7 3 5 1 b - l l - 0 3 - c n 图 1 1 - 2 Q F P 结构 图 1 1 - 3 C Q F P 结构 注 : 本 体 四 面 具 有 鸥 翼 形 封 装 通 常 釆 用 再 流 焊 工 艺 。高 引 线 密 度 细 间 距 元 件 可 能 需 要 在 …

201 0 年 6 月 IPC-735IB CN

表 1 1 - 1 本体四面具有鸪翼形引线的元器件的可焊性测试

J-S TD -002中的测试方法A/A1

J-STD -002中的测试方法D

蒸汽老化默认值

焊 料 槽 / 浸 入 和 观 察 测 试 (有

引线元器件和标准金属线)

抗溶 蚀 /金属层退润湿测试

类 别 3,蒸汽条 件下8h±15m m

镀层可能由锡铅合金组成,也可能是其无铅替代物。如果使用的是锡铅,焊料应该含有58%-68% 的锡。

端子上的表面涂层可以使用热浸法或使用电镀溶液。电镀后的端子应该能够进行电镀后再流焊操作,使

焊料溶化。如果使用锡铅表面涂层,其厚度应该至少达到0.0075mm[(I0003iii]。

端子应当是对称的,并且不应当有结瘤、结块和突出等等会影响元器件的对称性和尺寸公差的瑕疵。末

尾端子应当覆盖元器件的末端,并且应当延伸至元器件的顶部和底部。

在贵重金属电极上使用焊料时,在电极金属层和焊料之间应当有一层扩散阻挡层。阻挡层应该是镍或者

同性质替代物,并且其厚度应该至少达到(X00125mm[0.00005in]。

本体四面具有鸥翼形引线的元器件系列通常情况下都釆用标准再流焊工艺。元器件应该能够承受一个标

准再流焊系统中的1 0 次循环。每次循环中,锡铅条件和无铅条件下分别应当有10-30秒 或 20-40秒处于

最高温度,高低差异在5 ° C 以内。

部件还必须能够在熔融焊料中达到最低的浸入时间,相应时间和温度见表11-2。如果釆用再流焊接工艺,

IPC/JEDEC J-STD-020中的要求显示了再流条件的适合周期和曲线,详 见 表 11-3。除此之外,湿度敏感性

等 级 (M S L ) 应当符合J-STD-020标准中的定义,从而合理确立元器件的现场寿命。

表 1 1 - 2 可焊性、浸入方法:测 试 严 格 条 件 (时间和温度)

合金组成

严格条件

(215 + 3) °C

(3 + /0 3) s (1 0 ± l)s

(2 3 5 ± 5 ) °C

(2+/0.2) s (5 ± d 5 )s

(2 4 5 ± 5 ) °C

(3+ /03 ) s

(2 5 0 ± 5 ) °C

(3+ /03 ) s

SnPb

X X X X

Sn96.5Ag3.0Cu0.5

X

Sn993Cu.0.7

X

以上合金选择仅用于测试需要。含有3 .( ^ 〖%到4 1 ^ 1 % 银、0.5贾1 % 到 1.0胃〖%铜,其余都为锡的焊料合金可以取代

Sn96 jA .g3,0C ud5。含 有 0,45wt% 到 0,9wt% 铜 ,其余都为锡的焊料合金可以取代Sn99,3Cud7。

注 1 : “ X ” 代表适用。

注 2 : 合金组成的定义请参阅IPC-J-SHM )06。

注 3 : 本表中所列举的基本无铅焊料合金是目前比较适用于无铅焊接工艺的。如果所使用的焊料合金未列在此表中,应该证明所

列的严格条件也是适用的。

表 1 1 - 3 封装最高再流温度

再流条件

封装厚度> 2 .5m m 或

封装体积> 350mm3

封装厚度< 2 .5m m 或

封装体积< 350醒歷3

锡铅共晶

对流 225+0/-5°C 对流 240+0/-5°C

无铅

对流 245+0 ° C 对流 260+0 ° C

注 1 : 封装体积不包括外 部端子 (焊料球、凸点、连接盘和引线)和 / 或独立的散热层。

注 2 : 再流焊中达到的最大元器件温度取决于封装厚度和体积。对流再流焊工艺的使用缩小了封装之间的热梯度。

但是,表 面 贴 装 器 件 (S_MD)贴装的热容量不同引起的热梯度依然存在。

注 3 : 预 期 使 用 “ 无 铅” 组装工艺的元器件应当用定义的“ 无铅” 最高温度和曲线进行评估。

所有元件都应当标识有元件编号和索引区域。索引区域应当指明1 脚的位置。

67

IPC-7351B CN

2010年 6 月

IPC-7351b-ll-02-cn IPC-7351b-ll-03-cn

图 11-2 Q F P 结构

图 11-3 CQFP结构

注 :本体四面具有鸥翼形封装通常釆用再流焊工艺。高引线密度细间距元件可能需要在基本贴装和再流

制造操作之外进行特殊的工艺流程。某些情况 下,贴装、切割和再流工艺的独立操作可以代替传统的

SM T工艺。

11.1 BQFP 或 PQFP 见图 11-1。 BQFP 的 引 线

中 心 距 为 0.635mm。IPC-7355 B Q FP元器件外形来

源 于 JED EC第 9 5 出 版 物 中 的 外 形 M O-069和 MO-

086。

1 1 . 1 .1 载 体 封 装 方 式 B Q F P 的载体封装方式是管

装 ;但是,托盘封装可以提供最佳的处理条件。

11.2 Q F P 扁 平 封 装 (QFP) 是为了适应低厚度和

高密度的要求而开发的。和 SO P —样 ,Q F P 元器件

多用于存储卡技术。正 方 形 Q F P 系列的引线中心距

有 0.80mm、0.65mm、0.63mm、0.40mm 或 0.30mm

几种。IPC-7375 Q F P 元器件外形来源于JED EC第 9 5 出版物中的外形MO-108。

元件封装底部具有散热焊盘,直接与印制板表面接触,这 是 Q F P 系列元件的显著特征。在印制板上进行

焊接时,Q F P 元件可以通过这种方式获得热传导途径从而达到有效散热目的。也有 些 Q FP 元件没有热焊

盘引脚。详 见 3.1.5.7热焊盘的钢网设计要求。

每个封装有两种不同的引脚数量可供选择,元器 件 还 是 会 符合标准(例如:一个 间距为0.3m m 的 5X 5封

装 可 以 有 5 6 或 4 8 个引脚,还是 符 合 EIAJ-7404-1标 准 )。方 形 扁 平 封 装 (Q F P ) 也是正方形的,且有更

大的间距。(见 图 11-2)

1 1 . 2 . 1 载 体 封 装 方 式 扁平封装的载体封装方式可能是管装;但是,在很多情况下,扁平封装使用托盘

作为载体。

11.3 C Q F P 见 图 11-3中的陶瓷 方 形扁平 封 装 (C Q F P )结构。有引线陶瓷芯片载体通常有一个用于放

芯片的腔体。围绕这个腔体用陶瓷或者玻璃料焊接、用环氧树脂粘合或玻璃原料密封,以达到密封效果。

68

201 0 年 6 月 IPC-735IB CN

这种结构的一个例外是JEDEC标准 中 的 MS-044,其引线框架上键合,然后引线框在两个陶瓷体之间用

玻璃料进行密封,类似 于陶 瓷 双 列 直插 式 封 装 (C E R D IP )的制作工艺。陶瓷封装通常有2 8 到 196个不

等的 引线 布 局 ,中 心 距 有 1.27mm、0,80mm.和 0,63m..m几 种 。除了 M S-044的例外情况之外,IPC-7355

CQFP元器件外形来源于JED EC第 9 5 出版物中的外形MO-084、M O-104和 MO-114。

加引线前的陶瓷芯片载体在供应时,制造商通常会附带铜合金或科瓦铁镍钴合金的引线。引线通常和芯

片载体的顶面键合。但是 ,引线也可以和封装的城堡形端子相连。通常使用的连接方法是钎焊法或热压

键合。有一些加引线前的封装使用的是引线框架结构。这种芯片载体的陶瓷本体被分成了对立的两半,

分别位于一个引线框架的上方和下方,同时框架上已经预先键合了芯片。密封是通过玻璃料完成的。

引线可以形成不同的形状,例 如 “ J ”、“ L ” 或 “ C ” 形 。弯 曲 成 “L ” 形 的 引 线 称 之 为 “ 鸥翼形”。

加引线前的芯片载体在供应时附加有直引线,用一条常见的带子绑住。用户在使用时应该解开带子,同

时将引线弯曲成需要的形状。这样可以在运输和处理过程中减少引线弯曲的几率。引线可进行预先上锡

或者涂上黄金镀层,这样主要是适应高可靠性用户需要的封装要求。

1 1 . 3 .1 载体封装方式推荐 管状载体以达到最 佳处理条件。

12 IPC-7356本体四面具有J 形引线的元器件

本体四面具有J 形引线的元器件也称作有引线芯片载体,为封装体上有端子伸出的陶瓷或塑料封装。出于

清洗、检验或者适应不同热膨胀系数方面的考虑,这些端子起到了将封装本体和封装互连结构分开的作

用 。引线可能在连接芯片之前或之后被连接到封装本体上。

对于塑料有引线芯片载体,主要的封装差异关系到芯片安装到封装体上的连接点。模制前封装体的有引

线本体上有一个用于放芯片的腔 体 。模制后的封装体上,芯片已经连接到一个引线框架上,并且在组件

外围模制了一个绝缘塑料外壳。制造商所供应的模制后封装体没有开孔。

有引线陶瓷芯片载体也可以用类似的方法分类,但是在类别上有所区别。这个区别关系到引线连接到陶

瓷本 体 上 的连 接 点 (如果需要)。加引线前陶瓷芯片载体在供应时通常附带有铜合金或科瓦铁镍钴合金引

线 ,这些引线被铜焊到陶瓷封装体上的金属部分。一般情况下,封装上留有用于放置芯片的空腔体。芯

片周围用玻璃料焊接、环氧树脂粘合或连接陶瓷或金属盖子,以达到密封效果。这些步骤之后,有引线

的组件将被贴装到印制电路板上。

加引线后的陶瓷芯片载体通常在已连接芯片的陶瓷封装的金属化部分焊接了引线。这些引线可能表现为

锋利夹片或焊料柱的形式。通常情况下,引线连接到组件上后马上就会进行印制板贴装。

表面贴装有引线芯 片 载体上的 高 引线共 面 性 对于实 现 印制电 路 板 上的可 靠 焊 接是非 常 重要的 一 个 因

素。其平面性可能从封装体的最低三个引线测得。推 荐 共 面 性 最 大 值 为 最 理 想 条 件 是

0.05mm[0.002In]o

引线端接点上应当涂上一层表面处理剂,起到保护作用并且维持可焊性。对引线端接点的评估应当使用

[PC J-STD -002中描述的方法。用户和供应商之间如果没有其他的协议,则 A /A 1和 D 应当为默认的测试

方法。用户和供应商需要对IPC-J-STD-002中定义的涂覆层耐久性要求达成一致。如果没有提供,那么

IPC-J-STD-002中 的 “ 典型涂覆层耐久性等级3 ” 成为表面处理剂的默认条件,详 见 表 1.2-1。

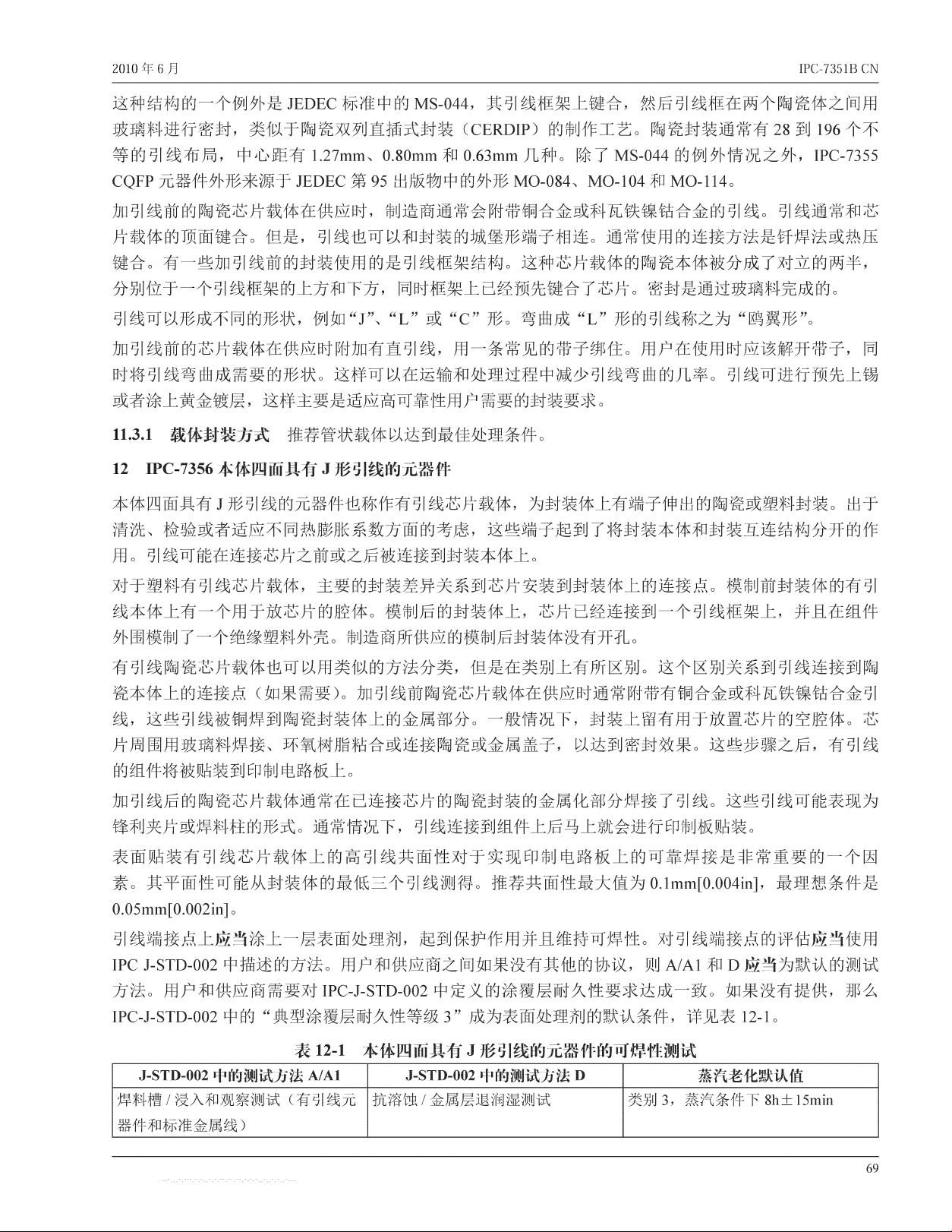

表 1 2 - 1 本体四面具有J 形引线的元器件的可焊性测试

J-S TD -002中的测试方法A/A1

J-S TD -002中的测试方法D

蒸汽老化默认值

焊 料 槽 / 浸 入 和 观 察 测 试 (有引线元

器件和标准金属线)

抗 溶 蚀 /金属层退润湿测试

类 别 3 ,蒸汽 条件下8h + 1.5min

69